#### Lina: a fast design optimisation tool for software-based FPGA programming

#### André Bannwart Perina

Tese de Doutorado do Programa de Pós-Graduação em Ciências de Computação e Matemática Computacional (PPG-CCMC)

SERVIÇO DE PÓS-GRADUAÇÃO DO ICMC-USP

Data de Depósito:

Assinatura:

#### André Bannwart Perina

# Lina: a fast design optimisation tool for software-based FPGA programming

Thesis submitted to the Instituto de Ciências Matemáticas e de Computação – ICMC-USP – in accordance with the requirements of the Computer and Mathematical Sciences Graduate Program, for the degree of Doctor in Science. *FINAL VERSION*

Concentration Area: Computer Science and Computational Mathematics

Advisor: Prof. Dr. Vanderlei Bonato

USP – São Carlos August 2022

#### Ficha catalográfica elaborada pela Biblioteca Prof. Achille Bassi e Seção Técnica de Informática, ICMC/USP, com os dados inseridos pelo(a) autor(a)

Perina, André Bannwart

Lina: a fast design optimisation tool for

software-based FPGA programming / André Bannwart

Perina; orientador Vanderlei Bonato. -- São Carlos,

2022.

189 p.

Tese (Doutorado - Programa de Pós-Graduação em

Ciências de Computação e Matemática Computacional) -Instituto de Ciências Matemáticas e de Computação,

Universidade de São Paulo, 2022.

1. FPGA. 2. High-level synthesis. 3. Design

space exploration. 4. Synthesis-less design

exploration. I. Bonato, Vanderlei, orient. II.

Titulo.

Bibliotecários responsáveis pela estrutura de catalogação da publicação de acordo com a AACR2: Gláucia Maria Saia Cristianini - CRB - 8/4938 Juliana de Souza Moraes - CRB - 8/6176 André Bannwart Perina

# Lina: uma ferramenta de otimização de projeto para programação de FPGAs baseada em software

Tese apresentada ao Instituto de Ciências Matemáticas e de Computação – ICMC-USP, como parte dos requisitos para obtenção do título de Doutor em Ciências – Ciências de Computação e Matemática Computacional. *VERSÃO REVISADA*

Área de Concentração: Ciências de Computação e Matemática Computacional

Orientador: Prof. Dr. Vanderlei Bonato

USP – São Carlos Agosto de 2022

The path that resulted in this thesis includes several contributions in various forms. Here is the acknowledgment for those.

First, I would like to thank Prof. Vanderlei Bonato for the significant insight, suggestions and guidelines given through these years. A great thank you also goes to Prof. Jürgen Becker for the great advisorship given through the last years. Also Prof. Eduardo Marques, Prof. Alexandre Delbem, Prof. João Cardoso and Prof. Pedro Diniz for all the research lessons that I gathered in my academic years.

I also appreciate all the support, both research and emotional, of all the people I've met in the research community. A special thank you to the Laboratório de Computação Reconfigurável (LCR), including Carlos, Leandro, Erinaldo, Marcilyanne. Also my great appreciation for the Institute for Information Processing Technologies of the Karlsruhe Institute of Technology (ITIV-KIT), that provided significant support for this work (thank you Arthur, Augusto, Birgitta, Fabian, Florian, Jens, Kevin, Steffen, and all of ITIV).

I also leave my deep thank you to all family and friends who have been involved in this journey. To my family in São Vicente / Santos and Indaiatuba, and specially to my brother, my mother and my father for always being around when needed. Thank you to the friends in São Carlos for all the experience (thank you Gaperia for all friendship!), to the friends in Indaiatuba, São Vicente / Santos, Karlsruhe. You all have been vital through this journey. A special thank you to my friends Carol, Filipe and Maria for all the patience, friendship and support.

In addition, I would like to thank all the infrastructural and financial support given for this research:

- To the institutes and universities ICMC-USP and ITIV-KIT;

- To the "Fundação de Amparo à Pesquisa do Estado de São Paulo" (FAPESP) for the significant support given through processes no. 2016/18937-7 and 2018/22289-6;

- To the "Coordenação de Aperfeiçoamento de Pessoal de Nível Superior Brasil" (CAPES), which partially financed this project through finance code 001;

- To the "Conselho Nacional de Desenvolvimento Científico e Tecnológico" (CNPq) that financed the early steps of my graduate program;

• To the "Paderborn Center for Parallel Computing" and "Intel Labs Academic Compute Environment", for providing access to the Intel Hardware Accelerator Research Program (HARP) resources.

At last, I thank the examination board for the insights and suggestions provided during defence.

"All for freedom and for pleasure Nothing ever lasts forever Everybody wants to rule the world" (Tears for Fears)

### RESUMO

PERINA, A. B. Lina: uma ferramenta de otimização de projeto para programação de FPGAs baseada em software. 2022. 189 p. Tese (Doutorado em Ciências – Ciências de Computação e Matemática Computacional) – Instituto de Ciências Matemáticas e de Computação, Universidade de São Paulo, São Carlos – SP, 2022.

A contínua jornada da indústria de semicondutores levou ao desenvolvimento de diversas arquiteturas alternativas para uma computação eficiente. "Field-Programmable Gate Arrays" (FPGAs) e "Graphics Processing Units" (GPUs) são exemplos de dispositivos utilizados para acelerar aplicações. FPGAs são capazes de oferecer um paralelismo massivo para tarefas adequadas quando apropriadamente programados. No entanto, projetar para FPGA não é trivial e requer um conhecimento específico que foge do desenvolvimento usual em software. Como uma alternativa buscando aumentar a programabilidade, ferramentas de Síntese de Alto Nível (do inglês "High-Level Synthesis", ou HLS) permitem o uso de linguagens de alto-nível como C/C++/OpenCL para programar FPGAs. No entanto, experimentos preliminares e outros estudos na literatura demonstram que ainda são necessárias diversas modificações no código de alto nível para que os resultados sejam minimamente aceitáveis. Tal aspecto mitiga a democratização e simplificação propostas pelas ferramentas HLS. A contribuição principal desta tese considera C/C++ como linguagem de entrada HLS, e é composta por uma ferramenta de exploração de espaço de projeto acoplada à um estimador denominado Lina. Baseado no estimador Lin-analyzer, Lina usa a execução instrumentada de um código em alto-nível para aproximar o método de compilação do Vivado HLS, um compilador HLS C/C++ para FPGAs da Xilinx. Para um dado kernel C/C++, Lina calcula uma rápida estimativa para métricas de tempo de execução e recursos de FPGA ocupados. Junto com diretivas de otimização usadas pelo compilador HLS que o Lina também suporta, a metodologia aqui proposta permite a otimização não apenas do tempo de execução, mas também de recursos lógicos de FPGA. Considerando 16 kernels C/C++ do benchmark PolyBench, as soluções estimadas como ótimas pelo Lina estiveram dentro de 1% das melhores opções consideradas. Uma média de  $14 - 16 \times$  de speedup de performance foi atingida, o que representa 70% do valor máximo alcançável considerando os espaços de projeto explorados. Adicionalmente, Lina suporta a exploração de transações com memórias off-chip em busca de otimizações como coalescência, empacotamento de dados, ou até informar sobre potenciais limitações do compilador HLS que possam degradar a performance.

**Palavras-chave:** FPGA, Síntese de alto nível, Exploração de espaço de projeto, Exploração sem síntese de projeto.

### ABSTRACT

PERINA, A. B. Lina: a fast design optimisation tool for software-based FPGA programming. 2022. 189 p. Tese (Doutorado em Ciências – Ciências de Computação e Matemática Computacional) – Instituto de Ciências Matemáticas e de Computação, Universidade de São Paulo, São Carlos – SP, 2022.

The continuous technology push on the semiconductor industry has led to the development of several alternate architectures for efficient computing. Field-Programmable Gate Arrays (FPGAs) and Graphics Processing Units (GPUs) are examples of devices used to accelerate applications. FPGAs are able to provide massive parallelism for suitable tasks when properly programmed. However, designing for FPGA is non-trivial and requires specific knowledge that deviates from the usual software programming. As an alternative towards increasing programmability, High-Level Synthesis (HLS) tools allow high-level languages such as C/C++/OpenCL to be used as input for FPGA design. However, early experiments and other studies in the literature demonstrate that significant code modification is still necessary so that the results are minimally acceptable. This aspect mitigates the democratisation and simplification that HLS tools seek to achieve. The major contribution of this thesis works on the C/C++ level, composed of a design space exploration tool that uses an estimator named Lina. Based on Lin-analyzer, Lina uses a traced execution of a software code to approximate the compilation behaviour of Vivado HLS, a C/C++ HLS compiler for Xilinx FPGAs. For a given C/C++ kernel, Lina provides a fast approximation of metrics such as execution time and FPGA resources occupied. Along with HLS compiler optimisation directives that Lina supports in its estimation, our exploration method allows the optimisation of not only execution time, but also FPGA resource usage. We then used Lina to optimise 16 C/C++ kernels from the PolyBench benchmark, and the estimated optimal solutions were among the 1% best options. An average of  $14 - 16 \times$  performance speedup was achieved, accounting for 70% of the reachable speedup when considering the traversed design spaces. Additionally, Lina allows the exploration of off-chip memory transactions in search of optimisations such as coalescing, data packing, or to inform about potential HLS compiler limitations that could degrade performance.

**Keywords:** FPGA, High-level synthesis, Design space exploration, Synthesis-less design exploration.

| Figure 1 $-$ | Transistor count of several integrated circuits over the last decades   | 33 |

|--------------|-------------------------------------------------------------------------|----|

| Figure 2 –   | Power density evolution over different transistor sizes. ITRS estima-   |    |

|              | tions are from 2013 (Semiconductor Industry Association, 2013) and      |    |

|              | conservative estimations are from Borkar (2010)                         | 35 |

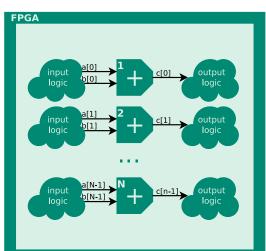

| Figure 3 –   | Simple depiction of a vector add example on CPU and FPGA                | 36 |

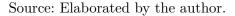

| Figure 4 –   | Basic depiction of the hardware generated by an HLS compiler. Con-      |    |

|              | tinuous lines represent data lanes, and dotted lines represent control  |    |

|              | lanes. Three FUs are shown in this example: two adders and one divider. | 38 |

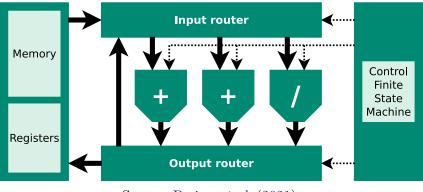

| Figure 5 –   | Comparison between manual optimisation approach (left) and the auto-    |    |

|              | matic optimisation approach using the proposed DSE framework (right).   | 39 |

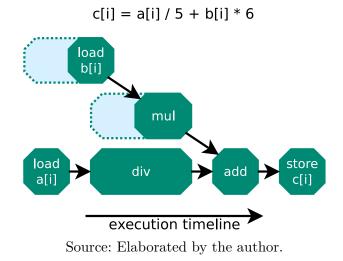

| Figure 6 –   | Example of a simple function and its dependency graph. The dashed       |    |

|              | region of the nodes represent the schedule window and the edges rep-    |    |

|              | resent the data dependencies                                            | 48 |

| Figure 7 –   | Example of loop unroll with factor 3                                    | 50 |

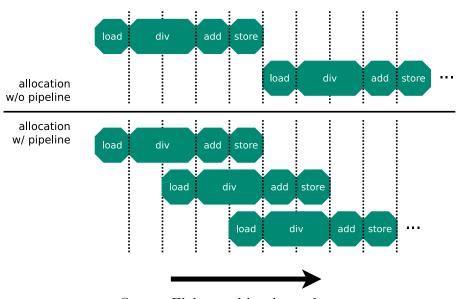

| Figure 8 –   | Example of loop scheduling without and with pipeline directive (new     |    |

|              | iteration starting every 2 cycles).                                     | 50 |

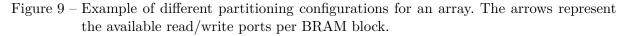

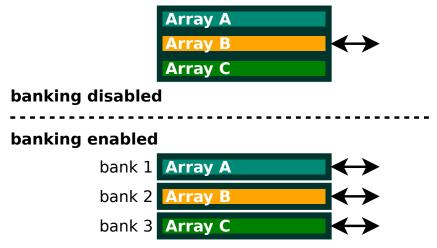

| Figure 9 $-$ | Example of different partitioning configurations for an array. The ar-  |    |

|              | rows represent the available read/write ports per BRAM block. $\hdots$  | 51 |

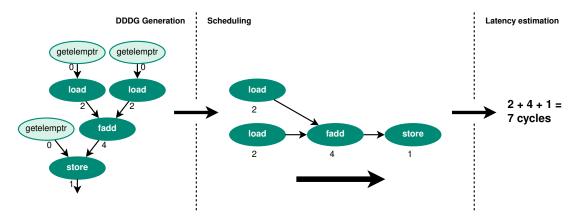

| Figure 10 –  | Example of DDDG generated from the LLVM IR of a vector add              | 52 |

| Figure 11 –  | Example of a DDDG scheduling and its latency calculation. In this       |    |

|              | example, the two load nodes are for different arrays and thus allowed   |    |

|              | to occur in parallel. Nodes with no relation to hardware generation     |    |

|              | (e.g. the getelementptr instructions) are removed prior to scheduling). | 52 |

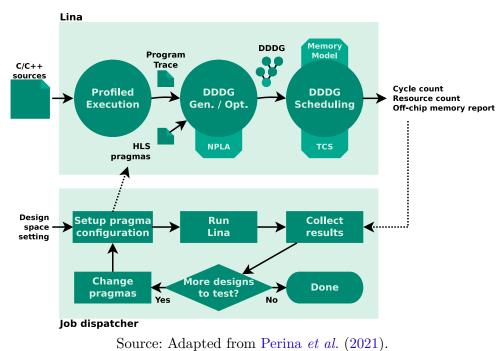

| Figure 12 –  | Lina flow: the trace is generated once for a given software code, then  |    |

|              | successive combinations of HLS pragmas are provided by the job dis-     |    |

|              | patcher to estimate each design's latency and resource count. NPLA      |    |

|              | and TCS stand for Non-Perfect Loop Analyser and Timing-Constrained      |    |

|              | Scheduler, respectively                                                 | 56 |

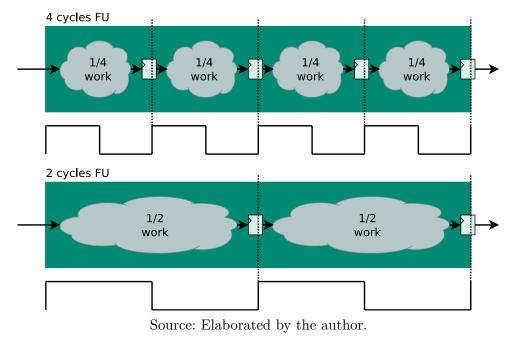

| Figure 13 –  | Depiction of two configurations for one FU, with latencies of 4 $(top)$ |    |

|              | and 2 (bottom) cycles, respectively. Smaller latencies lead to greater  |    |

|              | work per cycle, which in turn constrains the frequency                  | 57 |

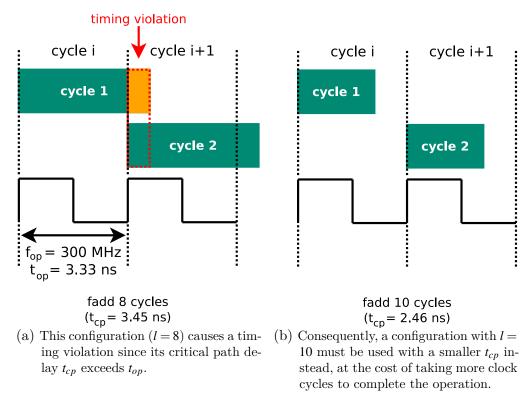

| Figure 14 –  | Two fadd configurations considered at a target clock frequency of       |    |

|              | 300MHz                                                                  | 60 |

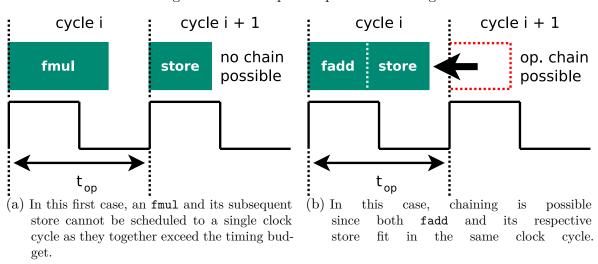

| Figure 15 – | Attempts of operation chaining                                                                                                                                                                                                                                                                                                                                                                                                       | 61       |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

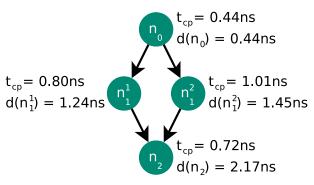

| Figure 16 – | Example of dependent nodes, their critical path delays $t_{cp}$ and largest delays up to each node $(d(\cdot))$ .                                                                                                                                                                                                                                                                                                                    | 63       |

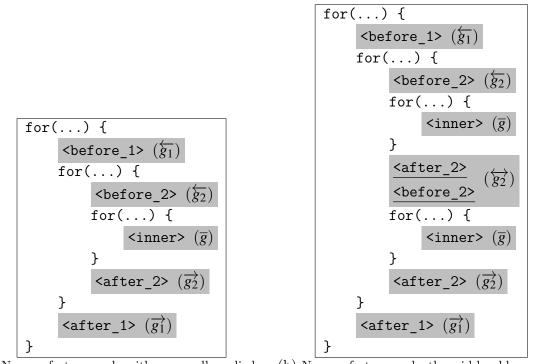

| Figure 17 – | Examples of non-perfect loop nests. Shaded regions represent the group<br>of statements that are placed before, inside, and after each loop level.<br>A separate DDDG $g$ is generated for each region. The notation used<br>to identify the DDDGs generated according to each region is shown in<br>parentheses.                                                                                                                    | 64       |

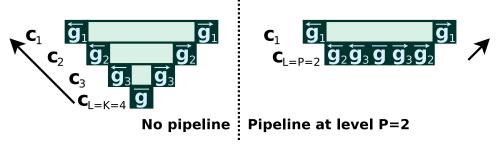

| Figure 18 – | Abstract example of a non-perfect loop nest $(K = 4 \text{ loop levels})$ and<br>how the $c_l$ values are calculated. At left, there is no pipeline enabled<br>and thus the calculation starts from the innermost level $(L = K = 4)$ .<br>At right, pipeline is enabled for the loop level $P = 2$ and thus the<br>calculation starts from $L = P = 2$ .                                                                            | 65       |

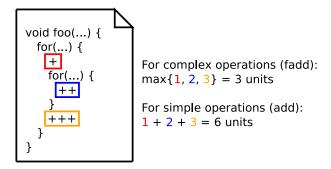

| Figure 19 – | Two examples of FU calculation based on the RCLS allocation results $FUc_q$ of each DDDG (each + denotes one FU allocated). The first calculation considers these adders as floating-point (complex) and the other canciders as integer (circula).                                                                                                                                                                                   | 67       |

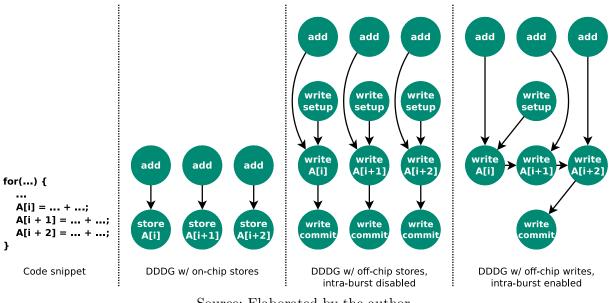

| Figure 20 – | other considers as integer (simple)                                                                                                                                                                                                                                                                                                                                                                                                  | 67<br>73 |

| Figure 21 – | Examples of DDDGs for a simple loop. Please note that although<br>there is no DDDG dependency between the three transactions when<br>intra-burst is disabled, they might be constrained during the RCLS<br>phase and overlapping is dependent on certain conditions (please see<br>subsubsection 3.2.4.2 for more details)                                                                                                           | 74       |

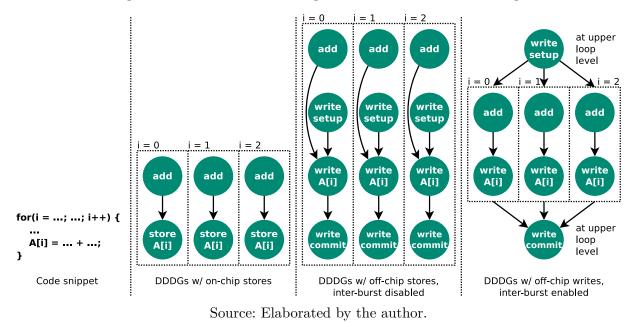

| Figure 22 – | Examples of DDDGs for a simple loop. DDDGs representing multiple<br>iterations are presented to exemplify the relation to the setup and<br>commit steps, though only one iteration is scheduled. Similar to last<br>figure, the RCLS phase might constrain multiple transactions to not<br>overlap even if their DDDGs are independent.                                                                                              | 75       |

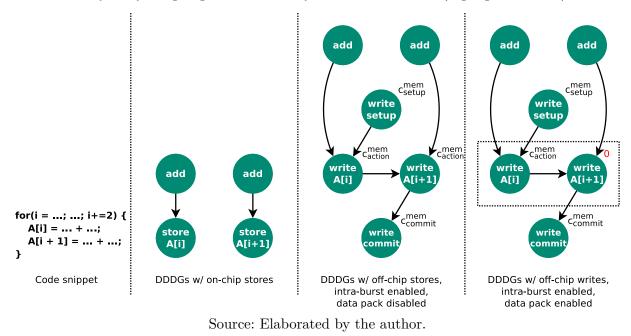

| Figure 23 – | Examples of DDDGs for a simple loop. The off-chip memory nodes are<br>annotated with the number of cycles required to solve each one. In the<br>last (right) case, the data packing analysis of Lina identifies that both<br>writes can be packed together as a single vectorised value. Lina allows<br>both nodes to be scheduled in the same clock cycle by assigning 0 to<br>the latency of the second write (highlighted in red) | 76       |

| Figure 24 – | the latency of the second write (highlighted in red)                                                                                                                                                                                                                                                                                                                                                                                 | 10       |

|             | indicate available read/write interfaces                                                                                                                                                                                                                                                                                                                                                                                             | 77       |

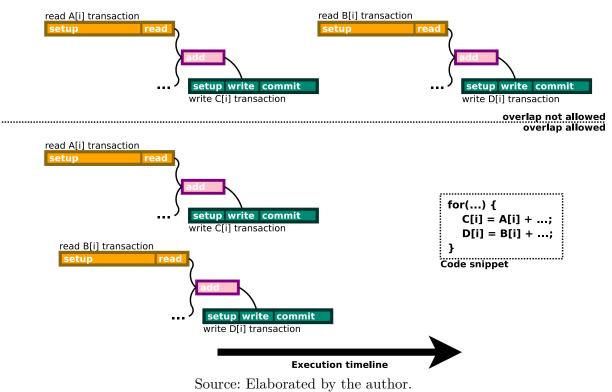

| Figure 25 – | Example of a code snippet with two independent read-add-write se-<br>quence of instructions. In the first case (above) the transactions are<br>not allowed to overlap and more clock cycles are required, whereas in<br>the second case (below), the transactions are allowed to overlap                                                                             | 78 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 26 – | Example of a "read-after-write" code pattern: The B array is accessed for read right after a write transaction to the same array (both transactions indicated in red).                                                                                                                                                                                               | 80 |

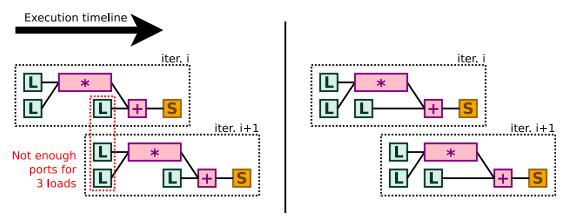

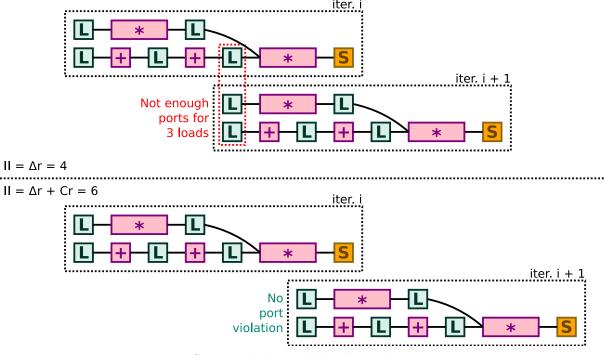

| Figure 27 – | Two schedule attempts with $H = 2$ . Instructions are represented by<br>small boxes ( $L$ and $S$ stand for load and store, respectively). At left,<br>the pipeline is not possible at this $H$ due to requiring more read ports<br>than available. At right, one of the load instructions is moved within<br>the schedule, which in turn lifts the port restriction | 82 |

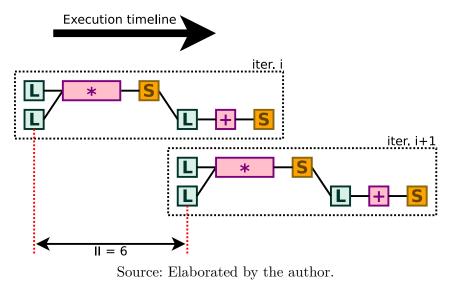

| Figure 28 – | Pipeline schedule with the presence of load/stores that cannot be easily moved. In this case, Vivado HLS reached an <i>II</i> of 6. Although this pipeline has 3 concurrent loads, they are not for the same array and thus there is no violation.                                                                                                                   | 83 |

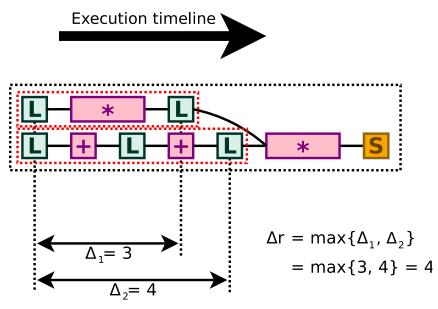

| Figure 29 – | Example of a schedule with multiple dependent loads and the respective $\Delta r_m$ calculation. Assume that all loads are for the same dual-ported interface. There are two independent read dependency paths for this interface, each indicated with a red dotted box                                                                                              | 85 |

| Figure 30 – | Two pipeline schedules for the same computation. At top, $II$ is set to $\Delta r_m = 4$ which triggers a read interface violation (indicated in red). At bottom, the $II$ value is relaxed to $\Delta r_m + Cr_m = 4 + 2 = 6$ . In this case, there is no port violation.                                                                                           | 86 |

| Figure 31 – | Snippets of a memory report generated by Lina                                                                                                                                                                                                                                                                                                                        | 86 |

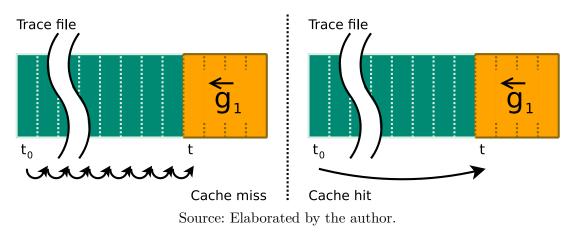

| Figure 32 – | Two examples of dynamic trace traversal for the generation of DDDG $\overleftarrow{g}_1$ . At left, there is a cache miss, and the trace must be traversed instruction-wise until the first instruction from $\overleftarrow{g}_1$ . At right, there is                                                                                                              |    |

a cache hit and Lina can proceed directly to the cached cursor t. . . . . . . 87

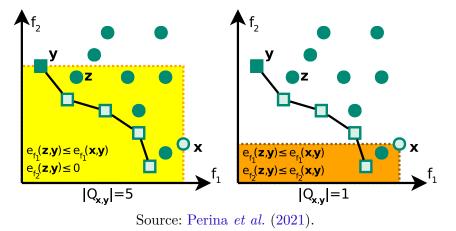

| Figure 33 – | Example of a two-objective design space, where the true Pareto points<br>are indicated as square points, the estimated Pareto point as $\mathbf{x}$ , and the<br>error metrics as $e_{f_1}$ and $e_{f_2}$ . The coloured regions represent the points<br>$\mathbf{z} \in D - P_{\text{viv}}$ that compose $Q_{\mathbf{x},\mathbf{y}}$ . In this example, $e_{f_2}(\mathbf{x},\mathbf{y})$ is negative.<br>At left, $Q_{\mathbf{x},\mathbf{y}}$ is constructed according to Equation 3.32. At right, the<br>predicate that defines $Q_{\mathbf{x},\mathbf{y}}$ does not use the <b>max</b> operator. Many other<br>points $\mathbf{z}$ are better approximations to $\mathbf{y}$ than $\mathbf{x}$ when considering both<br>objectives, even though $\mathbf{x}$ has a smaller $f_2$ objective than $\mathbf{y}$ . One<br>example of such point $\mathbf{z}$ is shown in the figure. The left case better<br>reflects this scenario by including more $\mathbf{z}$ points in $Q_{\mathbf{x},\mathbf{y}}$ , leading to a<br>larger NOD value |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 34 – | Xilinx Zynq UltraScale+ ZCU104 development kit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

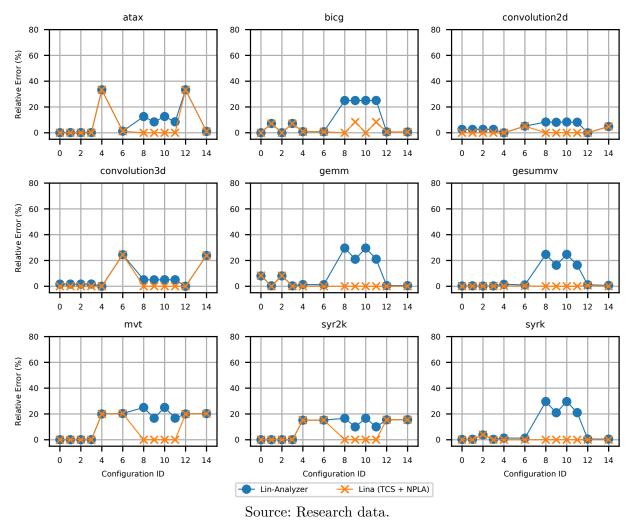

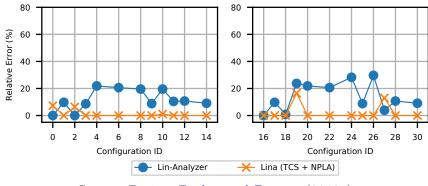

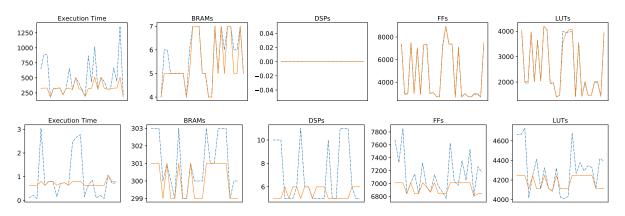

| Figure 35 – | Lina/Lin-analyzer estimation errors relative to the cycle counts reported by Vivado HLS. The x-axis represent different pragma configurations, and partitioning is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

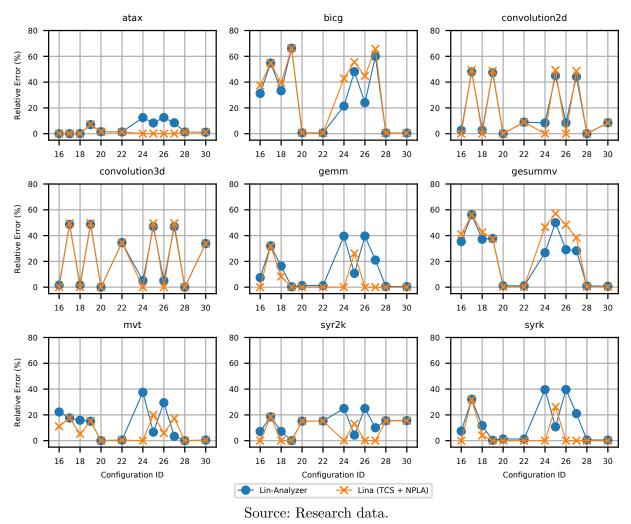

| Figure 36 – | Lina/Lin-analyzer estimation errors relative to the cycle counts reported by Vivado HLS. The x-axis represent different pragma configurations, and partitioning is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

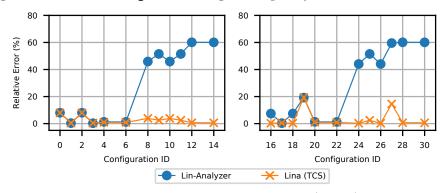

| Figure 37 – | Results for gemm with higher frequency for IDs 8-14 and 24-30 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

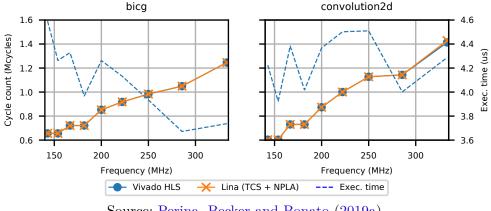

| Figure 38 – | Cycle count reported by Lina and Vivado HLS for bicg and conv2d<br>in different frequencies (all optimisations disabled). The dashed line<br>represents the design execution times considering frequency and cycle<br>count. Both plots are scaled to the same intervals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 39 – | Relative errors for a variant of gemm with different loop bounds 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

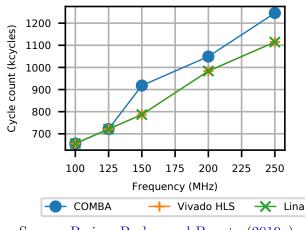

| Figure 40 – | Cycle count comparison between COMBA, Lina and Vivado HLS for<br>the <b>bicg</b> kernel at different frequencies (all optimisations disabled),<br>using a preliminary hardware profile library                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

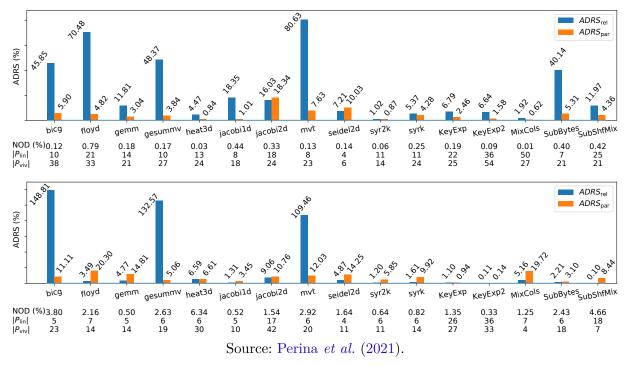

| Figure 41 – | Values of $ADRS_{rel}$ , $ADRS_{par}$ , NOD, $ P_{lin} $ and $ P_{viv} $ for each kernel in experiments hls (above) and fullsyn (below)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

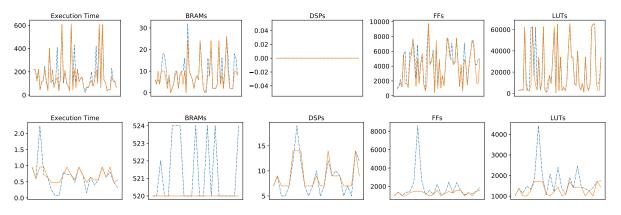

| Figure 42 – | Objective values for an approximation with low ADRS values (above) and high ADRS values (bottom) for the fullsyn experiment. The top plots represent KeyExp, and the bottom plots represent bicg. The blue dashed line represents the true Pareto points, and the continuous orange line represents the closest estimated Pareto points to each true solution. The y-axes represent the true objective value for each point (design execution time given in ns for KeyExp and $10^{-2}$ s for bicg) 105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 43 – | Objective values for an approximation with low ADRS values (above)<br>and high ADRS values (bettern) for the blg superiment. The ten |       |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------|-------|

|             | and high ADRS values (bottom) for the hls experiment. The top                                                                        |       |

|             | plots represent KeyExp2, and the bottom plots represent mvt. The                                                                     |       |

|             | blue dashed line represents the true Pareto points, and the continuous                                                               |       |

|             | orange line represents the closest estimated Pareto points to each true                                                              |       |

|             | solution. The y-axes represent the true objective value for each point $(1 + 1)^{-2}$                                                | 105   |

|             | (design execution time given in ns for KeyExp2 and $10^{-2}$ s for mvt)                                                              | . 105 |

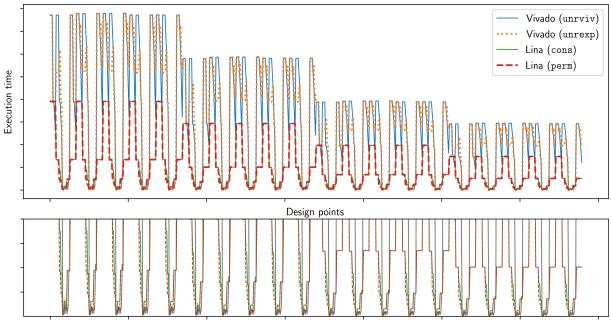

| Figure 44 – | Design execution time values and estimates for each design point in the                                                              |       |

|             | space (padmemory). The plot presented at bottom is a zoomed interval                                                                 |       |

|             | of the top plot.                                                                                                                     | . 112 |

| Figure 45 – | Design execution time values and estimates for each design point in the                                                              |       |

|             | space (padlogic). The plot presented at bottom is a zoomed interval                                                                  |       |

|             | of the top plot.                                                                                                                     | . 112 |

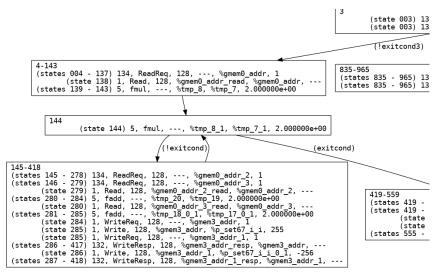

| Figure 46 – | Part of an FSM generated by vivado-fsmgen                                                                                            | . 131 |

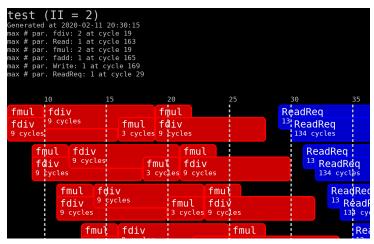

| Figure 47 – | Part of a scheduled pipeline as presented by pipelook                                                                                | . 132 |

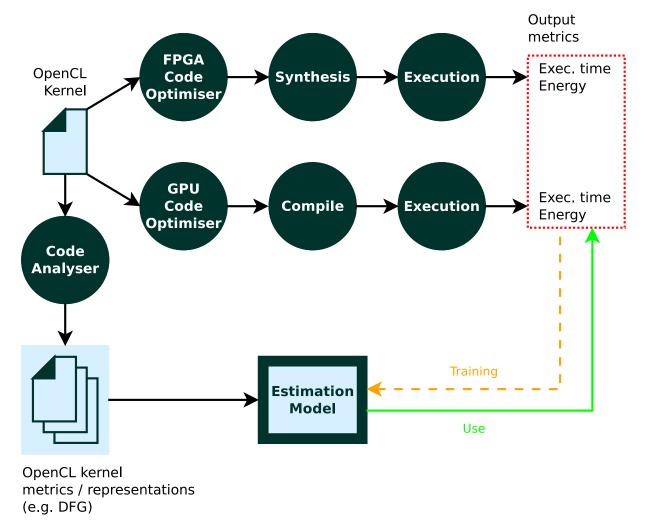

| Figure 48 – | Abstract representation of our proposed model. First, a reference set of                                                             |       |

|             | OpenCL kernels is optimised, executed and profiled. A code analyser is                                                               |       |

|             | then used to derive other representations (e.g. DFG) and/or numerical                                                                |       |

|             | metrics from each kernel. These, along with the profiled output metrics,                                                             |       |

|             | are used to train the estimation model (dashed orange arrow). During                                                                 |       |

|             | the use phase (solid green arrow), a test OpenCL kernel (KUT) is                                                                     |       |

|             | analysed and fed to the the estimation model. The model outputs an                                                                   |       |

|             | early estimation for the output metrics, considering the optimisation                                                                |       |

|             | phases for each platform.                                                                                                            | . 136 |

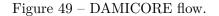

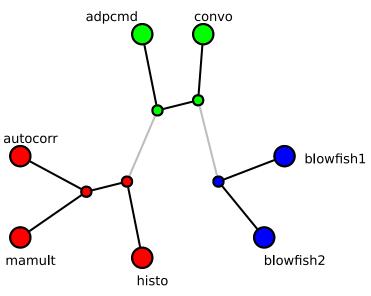

| Figure 49 – | DAMICORE flow.                                                                                                                       |       |

|             | Visual representation of a DAMICORE output. Each labelled node is                                                                    |       |

| i iguio oo  | a kernel.                                                                                                                            | 138   |

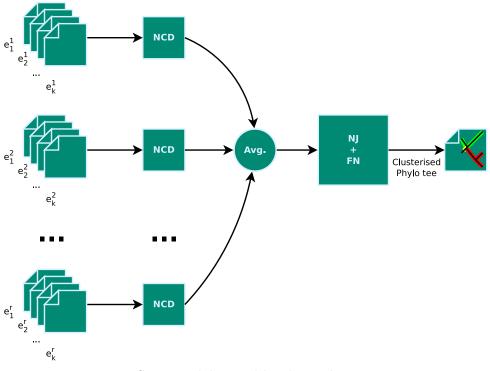

| Figuro 51 - | Overview of mdamicore2 using average NCD matrix calculation.                                                                         |       |

| -           | Generated phylogenetic tree for best case in experiment 5                                                                            |       |

| <u> </u>    |                                                                                                                                      | . 140 |

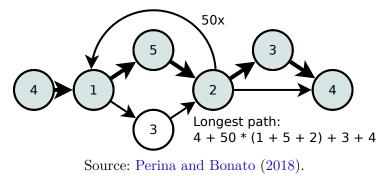

| Figure 53 – | Example of control-flow graph and its longest path in thicker edges.                                                                 |       |

|             | The weight of a node describes the amount of contained instructions.                                                                 | 150   |

|             | As an example, it is assumed a loop trip count of 50                                                                                 | . 150 |

| Figure 54 – | Comparison between the task and NDRange models for a simple vector                                                                   |       |

|             | add                                                                                                                                  | . 156 |

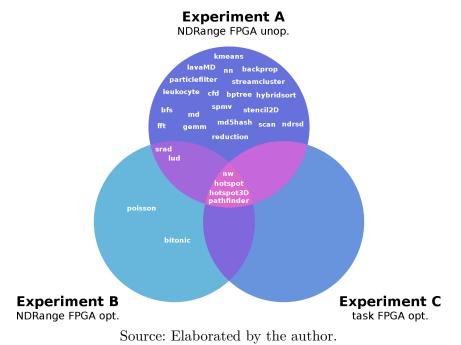

| Figure 55 – | Venn diagram of the kernels collected separated in three classes. Each                                                               |       |

|             | class represents a different level of FPGA optimisation effort and exe-                                                              |       |

|             | cution model. Kernel variants (e.g. $nw(1)$ , $nw(2)$ ) are grouped                                                                  | . 157 |

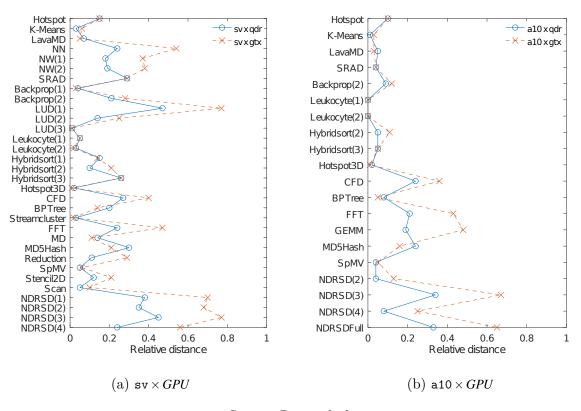

| Figure 56 – | Relative analysis for experiment A comparing each FPGA against both                                                                  |       |

|             | GPUs                                                                                                                                 | . 166 |

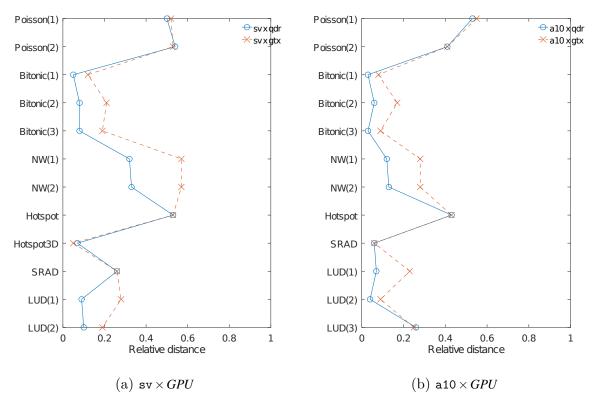

| Figure 57 – | Relative analysis for experiment B comparing each FPGA against both      |     |

|-------------|--------------------------------------------------------------------------|-----|

|             | GPUs                                                                     | 167 |

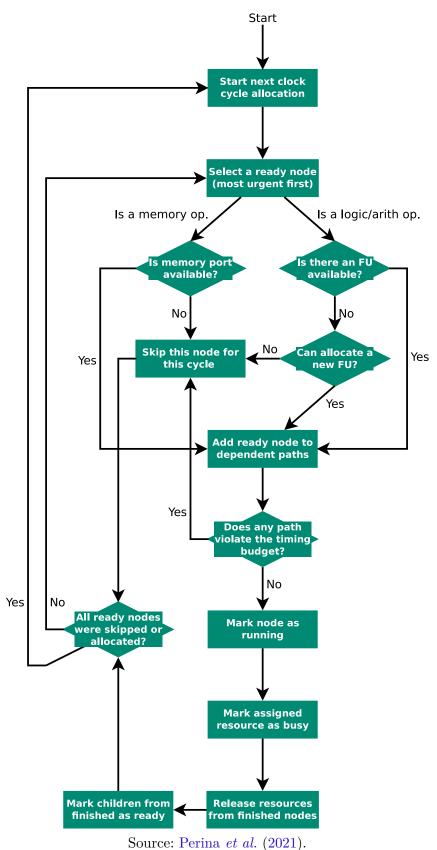

| Figure 58 – | Flowchart of the resource and timing-constrained scheduling performed    |     |

|             | by Lina. The urgency of a ready node is defined by the ALAP schedul-     |     |

|             | ing results (lower values are more urgent)                               | 174 |

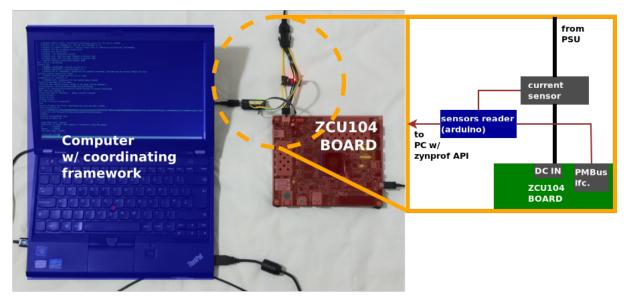

| Figure 59 – | Overview of the experimental framework                                   | 176 |

| Figure 60 – | FPGA experimental setup. The power sensing system is highlighted.        |     |

|             | An Arduino module reads the PSU current sensor and communicates          |     |

|             | with the regulators using the PMBus interface. The raw information       |     |

|             | is collected and sent to the host machine, which calculates consumed     |     |

|             | energy using a tool named zynprof                                        | 177 |

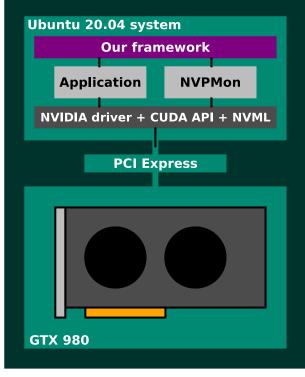

| Figure 61 – | GPU experimental setup. Our framework coordinates the application        |     |

|             | and extracts the power measurements from NVIDIA's NVML using             |     |

|             | our in-house tool (NVPMon).                                              | 178 |

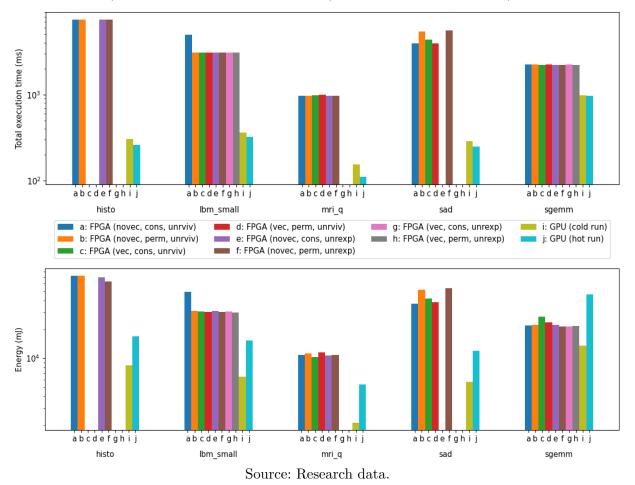

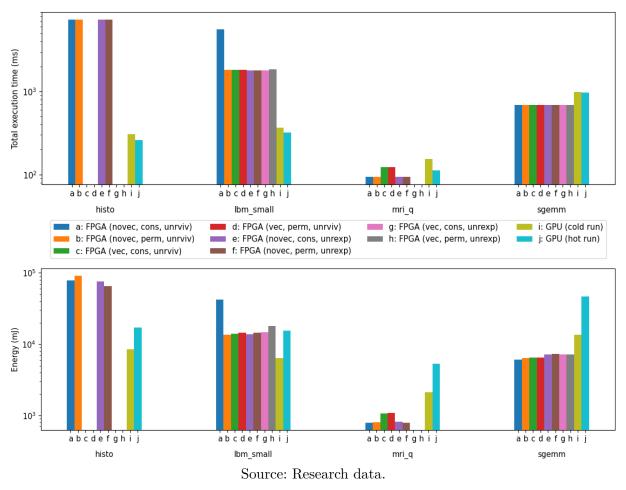

| Figure 62 – | Total execution time (top) and consumed energy (bottom) of each ker-     |     |

|             | nel on both platforms. Each is represented by 8 Lina explorations (left- |     |

|             | most bars, from "a" to "h") and 2 GPU execution scenarios (rightmost     |     |

|             | bars, "i" and "j")                                                       | 185 |

| Figure 63 – | Extrapolated execution time and energy values for the kernels in FPGA,   |     |

|             | compared to the real values in GPU. These estimations consider that      |     |

|             | the speedup achieved by the whole FPGA application is the same as        |     |

|             | the speedup achieved by the computation loop alone                       | 188 |

| Chart | 1 –  | Differences between Lin-analyzer and Lina                               |

|-------|------|-------------------------------------------------------------------------|

| Chart | 2 -  | Instructions executed by SDSoC/Vivado-generated designs for off-chip    |

|       |      | access, their relation to the abstract transaction steps, and the cycle |

|       |      | count of each instruction in the ZCU104 platform                        |

| Chart | 3 -  | The effect of scheduling policies on the memory model                   |

| Chart | 4 -  | Kernels used in the first validation                                    |

| Chart | 5 -  | Parameters used in the exploration                                      |

| Chart | 6 –  | Validation kernel set                                                   |

| Chart | 7 –  | Optimisation knobs                                                      |

| Chart | 8 -  | ZFNet CNN layer configuration used                                      |

| Chart | 9 –  | Optimisation knobs for the CNN kernels                                  |

| Chart | 10 - | Convolution experiments                                                 |

| Chart | 11 - | Related work comparison                                                 |

| Chart | 12 – | Tools used by our first approach, related to the abstract model previ-  |

|       |      | ously presented                                                         |

| Chart | 13 – | Execution results for the initial kernel set                            |

| Chart | 14 - | Tools used by our second approach, related to the abstract model pre-   |

|       |      | viously presented                                                       |

| Chart | 15 - | Extracted code features using OpCount                                   |

| Chart | 16 – | Neural networks setup parameters                                        |

| Chart | 17 – | FPGA-unoptimised NDRange kernels                                        |

| Chart | 18 - | FPGA-optimised NDRange kernels                                          |

| Chart | 19 – | FPGA-optimised task kernels                                             |

| Chart | 20 - | Class mapping for each experiment                                       |

| Chart | 21 - | Platforms used                                                          |

| Chart | 22 - | Last experiment kernel set                                              |

| Chart | 23 - | DSE knobs for the Parboil kernels                                       |

| Chart | 24 - | Modifications performed in each Parboil kernel                          |

| Algorithm 1 –   | The recursive exploration algorithm                                  | 59 |

|-----------------|----------------------------------------------------------------------|----|

| Algorithm $2$ – | The FU characterisation algorithm                                    | 60 |

| Algorithm 3 –   | Former approach to verify if in-clock cycle scheduling is possible . | 62 |

| Source code 1 $-$ Example of simple function used to characterise FUs $\ldots$       | 58 |

|--------------------------------------------------------------------------------------|----|

| Source code $2 -$ Rolled and unrolled (factor of 2) examples of a simple loop nest,  |    |

| both arrays are off-chip                                                             | 81 |

| Source code 3 $-$ Manually unrolled (factor of 2) variant of the simple loop nest .  | 81 |

| Source code 4 – Basic loop nest of a CNN kernel                                      | 96 |

| Source code 5 $-$ The padlogic CNN kernel $\ldots$                                   | 97 |

| Source code 6 $-$ Explicitly unrolled padmemory kernel, with all reads placed before |    |

| writes                                                                               | 98 |

| Source code 7 – OpenCL kernel template for histo                                     | 83 |

| Table 1 –   | Lina DSE execution times (hls experiment, in s)                                                                  | 106 |

|-------------|------------------------------------------------------------------------------------------------------------------|-----|

| Table 2 –   | Speedup results from COMBA and our DSE                                                                           | 108 |

| Table 3 $-$ | Design space sizes and exploration execution times (including per-point                                          |     |

|             | times) for COMBA and our DSE. All times are in $s.\ \ldots\ \ldots\ \ldots$                                      | 109 |

| Table 4 –   | Performance results for each CNN exploration                                                                     | 110 |

| Table 5 $-$ | Configuration for the best design point for each kernel                                                          | 111 |

| Table 6 $-$ | Experimental setup for the mdamicore2 approach                                                                   | 145 |

| Table 7 $-$ | Best and worst execution cases for each experiment                                                               | 146 |

| Table 8 –   | Average values for each experiment                                                                               | 147 |

| Table 9 $-$ | Performance results for all networks                                                                             | 153 |

| Table 10 –  | Compilation and execution success results                                                                        | 163 |

| Table 11 –  | Experiment A: absolute analysis                                                                                  | 164 |

| Table 12 –  | Experiment A: relative analysis.                                                                                 | 165 |

| Table 13 –  | Experiment B: absolute analysis                                                                                  | 166 |

| Table 14 –  | Experiment B: relative analysis.                                                                                 | 168 |

| Table 15 –  | Experiment C: absolute analysis                                                                                  | 168 |

| Table 16 –  | Experiment C: relative analysis.                                                                                 | 168 |

| Table 17 –  | Average execution time ratios all vs. $all^{ab}$                                                                 | 169 |

| Table 18 –  | Average energy consumption ratios all vs. all                                                                    | 169 |

| Table 19 –  | Overall speedups achieved by our optimised kernels compared to the                                               |     |

|             | baseline versions.                                                                                               | 186 |

| Table 20 –  | Overall energy efficiency gains achieved by our optimised kernels com-                                           |     |

|             | pared to the baseline versions. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 186 |

| Table 21 –  | Overall speedups achieved by our optimised kernels compared to the                                               |     |

|             | baseline versions (computation loops only, data transfers between on                                             |     |

|             | and off-chip are not considered)                                                                                 | 187 |

## LIST OF ABBREVIATIONS AND ACRONYMS

| ADRS          | Average Distance from Reference Set                 |

|---------------|-----------------------------------------------------|

| ALAP          | As-Late-As-Possible                                 |

| ANN           | Artificial Neural Network                           |

| AOCL          | Altera (Intel FPGA) SDK for OpenCL                  |

| ASAP          | As-Soon-As-Possible                                 |

| BRAM          | Block RAM                                           |

| CNN           | Convolutional Neural Network                        |

| CPU           | Central Processing Unit                             |

| DDDG          | Dynamic Data Dependency Graph                       |

| DFG           | Data-Flow Graph                                     |

| DSP           | Digital Signal Processor                            |

| DVFS          | Dynamic Voltage Frequency Scaling                   |

| $\mathbf{FF}$ | Flip-Flop                                           |

| FN            | Fast Newman                                         |

| FPGA          | Field-Programmable Gate Array                       |

| FU            | Functional Unit                                     |

| GPU           | Graphics Processing Unit                            |

| HBM           | High-Bandwidth Memory                               |

| HLS           | High-Level Synthesis                                |

| II            | Initiation Interval                                 |

| IR            | Intermediate Representation                         |

| ITRS          | International Technology Roadmap for Semiconductors |

| KUT           | Kernel Under Test                                   |

| LUT           | LookUp Table                                        |

| LVQ           | Learning Vector Quantisation                        |

| MLP           | Multi-Layer Perceptron                              |

| NCD           | Normalised Compression Distance                     |

| NJ            | Neighbour Joining                                   |

| NOD           | Near-Optimal Density                                |

| NVML          | NVIDIA Management Library                           |

| RBF           | Radial Basis Function                               |

|               |                                                     |

- RCLS Resource-Constrained List Scheduling

- RTL Register-Transfer Level

- SDC System of Difference Constraints

- SIMD Single-Instruction, Multiple Data

- SoC System-on-Chip

- TDP Thermal Design Power

| 1         | INTRODUCTION                                             | 33 |

|-----------|----------------------------------------------------------|----|

| 1.1       | Field-Programmable Gate Arrays and High-Level Synthesis  | 35 |

| 1.1.1     | High-Level Synthesis                                     | 37 |

| 1.2       | Motivation and Objective                                 | 38 |

| 1.3       | Thesis Structure                                         | 40 |

| 2         | LITERATURE REVIEW                                        | 41 |

| 2.1       | High-Level Synthesis Compilers                           | 41 |

| 2.2       | High-Level Synthesis Applications and Comparison Studies | 42 |

| 2.3       | High-Level Synthesis Assist Tools                        | 43 |

| 2.3.1     | High-Level Synthesis Estimators                          | 43 |

| 2.3.2     | High-Level Synthesis Optimisation Frameworks             | 44 |

| 2.4       | Final Remarks                                            | 45 |

| 3         | FAST DESIGN SPACE OPTIMISATION FOR C/C++ HLS USING       |    |

|           | LINA                                                     | 47 |

| 3.1       | Overview of High-Level Synthesis and Estimation          | 48 |

| 3.1.1     | Lin-analyzer Overview                                    | 51 |

| 3.2       | DSE Methodology with Lina                                | 54 |

| 3.2.1     | Timing-Constrained Scheduler                             | 56 |

| 3.2.1.1   | Hardware Profile Library and FU Characterisation         | 57 |

| 3.2.1.2   | Initial Timing Analysis                                  | 59 |

| 3.2.1.3   | Operation Chaining                                       | 60 |

| 3.2.2     | Non-Perfect Loop Analyser                                | 63 |

| 3.2.3     | Resource Awareness                                       | 66 |

| 3.2.3.1   | Functional Unit Resource Estimation                      | 66 |

| 3.2.3.2   | Array-related Resource Estimation                        | 68 |

| 3.2.3.2.1 | Scenario I                                               | 68 |

| 3.2.3.2.2 | Scenario II                                              | 68 |

| 3.2.3.2.3 | Scenario III                                             | 69 |

| 3.2.3.2.4 | Total Array Resource Usage                               | 69 |

| 3.2.3.3   | Complete Resource Estimation                             | 69 |

| 3.2.4     | Off-chip Memory Model                                    | 72 |

| 3.2.4.1   | Memory Model Features and Behaviour                                   | . 74               |

|-----------|-----------------------------------------------------------------------|--------------------|

| 3.2.4.1.1 | Intra-iteration bursts                                                | . 74               |

| 3.2.4.1.2 | Inter-iteration bursts                                                | . 74               |

| 3.2.4.1.3 | Data packing                                                          | . 75               |

| 3.2.4.1.4 | Memory banking                                                        | . 76               |

| 3.2.4.1.5 | Port management                                                       | . 77               |

| 3.2.4.2   | Interaction Between Multiple Transactions and Memory Model Policies   | . 77               |

| 3.2.4.3   | Interaction Between Off-chip Transactions and Pragmas                 | . 80               |

| 3.2.4.3.1 | Loop unroll                                                           | . 80               |

| 3.2.4.3.2 | Loop pipeline                                                         | . 81               |

| 3.2.4.4   | Memory Analysis Report                                                | . 85               |

| 3.2.5     | DSE Temporal Locality Caching                                         | . <b>87</b>        |

| 3.2.6     | Exploration Quality Metrics                                           | . <b>88</b>        |

| 3.3       | Experimental Setup                                                    | . 89               |

| 3.3.1     | Platforms and Software Used                                           | . <b>90</b>        |

| 3.3.2     | First Validation: Comparison Against Lin-Analyzer                     | . <b>91</b>        |

| 3.3.3     | Second Validation: Resource and Timing-aware Exploration              | . <b>93</b>        |

| 3.3.3.1   | Additional Experiments on Non-perfect Kernels with Larger Loop Bounds | . 94               |

| 3.3.3.2   | Comparison with Related Work                                          | . 95               |

| 3.3.4     | Third Validation: Off-chip Experiments in the CNN Context             | . <b>95</b>        |

| 3.4       | Results                                                               | . <b>98</b>        |

| 3.4.1     | First Validation: Comparison Against Lin-Analyzer                     | . <b>99</b>        |

| 3.4.2     | Second Validation: Resource and Timing-aware Exploration              | . <i>103</i>       |

| 3.4.2.1   | Impact of Lina Features                                               | . 106              |

| 3.4.2.2   | DSE Exploration Time                                                  | . 106              |

| 3.4.2.3   | Comparison Analysis                                                   | . 107              |

| 3.4.3     | Third Validation: Off-chip Experiments in the CNN Context             | . <i>109</i>       |

| 3.5       | Final Discussion                                                      | . 113              |

| 3.5.1     | Comparison with Related Work                                          | . <b>113</b>       |

| 3.5.2     | Framework Limitations                                                 | . 114              |

| 3.5.3     | Final Remarks                                                         | . 115              |

| 4         | CONCLUSION                                                            | . 117              |

| BIBLIOG   | <b>ГАРНҮ</b>                                                          | . 121              |

| APPEND    | DIX A PUBLISHED MATERIAL AND DEVELOPED TOOL                           | <mark>S</mark> 129 |

| A.1       | Published Material                                                    | . 129              |

| A.2       | Developed Tools                                                       | . 130              |

| APPENDIX B EARLY APPROACHES USING MACHINE LEARN-                            |                                              |             |  |  |

|-----------------------------------------------------------------------------|----------------------------------------------|-------------|--|--|

|                                                                             | ING MODELS                                   | 135         |  |  |

| B.1                                                                         | DAMICORE Approach                            | 136         |  |  |

| B.1.1                                                                       | The mdamicore2 Tool                          | <i>138</i>  |  |  |

| B.1.2                                                                       | Reference Set Generation                     | 139         |  |  |

| B.1.3                                                                       | Decision Making                              | 141         |  |  |

| B.1.4                                                                       | Quality Metric                               | 141         |  |  |

| B.1.5                                                                       | Initial Kernel Set                           | 142         |  |  |

| B.1.6                                                                       | Results                                      | 143         |  |  |

| B.1.6.1                                                                     | Execution Results for the Initial Kernel Set | 143         |  |  |

| B.1.6.2                                                                     | Evaluation of Proposed Model                 | 143         |  |  |

| B.2                                                                         | Neural Network Approach                      | 148         |  |  |

| B.2.1                                                                       | Formulation and Methodology                  | 14 <b>9</b> |  |  |

| B.2.1.1                                                                     | ANN Inputs                                   | 149         |  |  |

| B.2.1.2                                                                     | ANN Outputs                                  | 150         |  |  |

| B.2.2                                                                       | Neural Network Experimental Setup            | 150         |  |  |

| B.2.3                                                                       | Experimental Results                         | 152         |  |  |

| B.3                                                                         | Final Remarks                                | 153         |  |  |

|                                                                             |                                              |             |  |  |

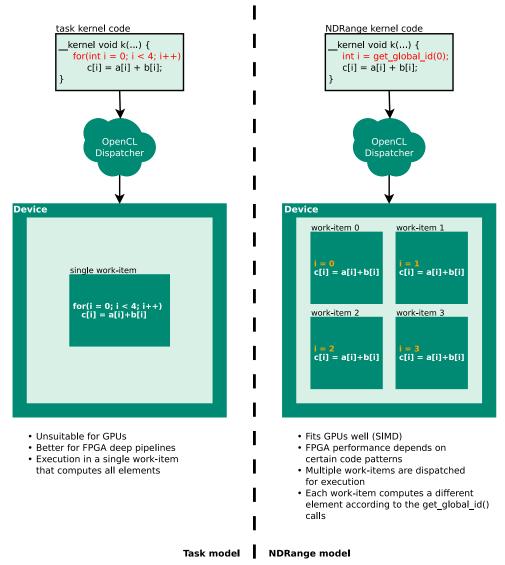

| APPENDIX C COMPARATIVE ANALYSIS OF OPENCL KERNELS                           |                                              |             |  |  |

| <b>C</b> .1                                                                 | IN FPGA AND GPU                              |             |  |  |

| C.1<br>C.2                                                                  | OpenCL Execution Models                      |             |  |  |

|                                                                             | Kernel Set                                   |             |  |  |

| C.2.1                                                                       | Class I: FPGA-unoptimised NDRange Kernels    |             |  |  |

| C.2.2                                                                       | Class II: FPGA-optimised NDRange Kernels     |             |  |  |

| C.2.3                                                                       | Class III: FPGA-optimised Task Kernels       |             |  |  |

| C.3                                                                         | Evaluation Setup                             |             |  |  |

| C.3.1                                                                       | Experimental Setup                           |             |  |  |

| C.3.2                                                                       | Suitability Metrics                          |             |  |  |

| C.3.3                                                                       | Accelerator Platforms                        |             |  |  |

| C.4                                                                         | Results                                      |             |  |  |

| C.4.1                                                                       | Experiment A                                 |             |  |  |

| C.4.2                                                                       | Experiment B                                 |             |  |  |

| C.4.3                                                                       | Experiment C                                 |             |  |  |

| C.4.4                                                                       | Final Comparison                             |             |  |  |

| C.4.5                                                                       | Discussion                                   |             |  |  |

| C.5                                                                         | Final Remarks                                | 171         |  |  |

| APPENDIX D LINA DSE: RESOURCE AND TIMING-CONSTRAINED<br>SCHEDULER FLOWCHART |                                              |             |  |  |

| <b>APPENDI</b> | C E         OPTIMISED FPGA-GPU COMPARATIVE ANALYSIS175 |

|----------------|--------------------------------------------------------|

| E.1            | Experimental Framework                                 |

| <b>E</b> .1.1  | FPGA Platform                                          |

| E.1.2          | GPU Platform                                           |

| <b>E</b> .1.3  | Kernel Set                                             |

| E.1.3.1        | Project Structuring and Modifications Applied          |

| E.2            | <b>Results</b>                                         |

| E.3            | Final Remarks                                          |

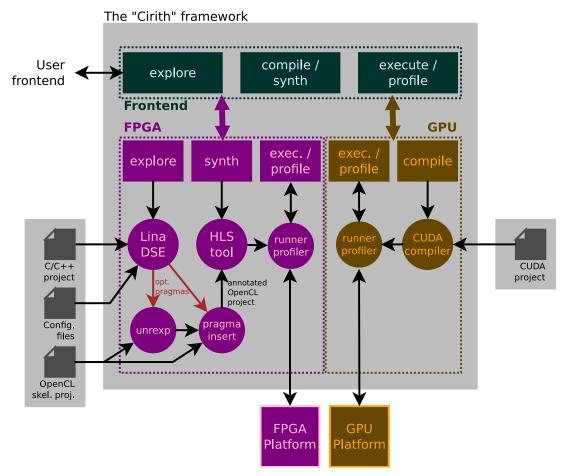

# CHAPTER 1

### INTRODUCTION

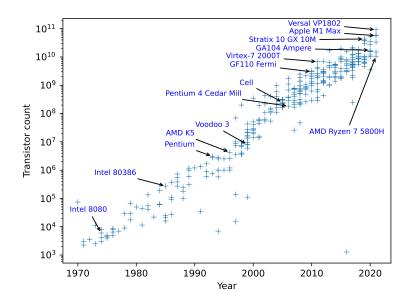

Digital electronic devices are omnipresent in most of modern human society. From staircase light timers to military-grade equipment, the capability and complexity of these devices greatly evolved during the last decades. This evolution is intimately related to the basic building block of every digital circuit: the transistor. Improvements in the fabrication process allowed smaller transistors to be produced, which in turn allowed the production of more complex and faster circuits. Figure 1 shows how the transistor count evolved during the years for common processing units of computers, phones, etc. The transistor count increased from few thousands in the 1970s to billions in late 2010s: a  $7 \times$  order of magnitude increase in the span of 50 years.

Figure 1 – Transistor count of several integrated circuits over the last decades.

Source: Adapted from Roser and Ritchie (2013), Wikipedia (2022).

Still in the 1970s, two "laws" were stated by famous researchers that provided a good insight on what was about to happen in the following years. The first one is the well-known Moore's law, which states that the number of transistors in a dense integrated circuit would double at roughly every two years (MOORE, 1965). The second law is the Dennard (or MOSFET) scaling, which roughly states that as transistors get smaller, their power density stays constant (DENNARD *et al.*, 1974). This has a twofold effect:

- The reduction of the transistor's size causes a reduction on the circuit's delay (since the paths are shorter), which in turn allows higher operating frequencies for the circuit. The reduced size also contributes to a reduced capacitance;

- The reduction of operating voltage, coupled with the reduced capacitance, contributes to lower energy consumption.

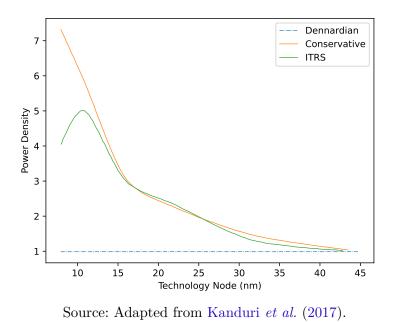

For roughly 30 years, the industry constantly reduced transistor sizes, increased transistor count on a microchip and increased the operating frequency. This allowed a constant evolution on processing capability while the energy consumption was still manageable. As the transistor sizes started to reach a few dozen nanometres, issues started to appear and reduce this downscaling trend. The leakage current of the transistors started to become more pronounced and coupled with the high operating frequencies, the energy efficiency of new devices started to worsen. This trend can be clearly seen in Figure 2, where the power density over different technology sizes is presented (KANDURI *et al.*, 2017). It is quite visible that the power density — as monitored by the International Technology Roadmap for Semiconductors (ITRS) — was not kept constant as proposed by the Dennard scaling. This increase caused issues not only on supplying proper power the whole circuit, but also issues on heat dissipation.

Therefore, the industry started to take different paths in order to circumvent the power density increase. Industry and academic efforts were directed towards finding technologies that could also improve the energy efficiency of the computations performed. Mainstream computer processors — the Central Processing Unit (CPU) — started to include features such as multi-core processing, Dynamic Voltage Frequency Scaling (DVFS) among other technologies that allowed to improve the energy efficiency.

Interest on other architectures also grew. Graphics Processing Units (GPU), for example, became increasingly ubiquituous for parallel computing applications. The GPU's architecture is highly suitable for matrix/vector operations due to its Single-Instruction, Multiple-Data (SIMD) nature. Before the 2000s, GPUs were solely used for graphical purposes of showing user interfaces, or as graphics accelerators for games and visual computation. Larsen and McAllister (2001) presented the first attempt to use a GPU as a computation platform. In this early experiment, a matrix-matrix multiply was performed Figure 2 – Power density evolution over different transistor sizes. ITRS estimations are from 2013 (Semiconductor Industry Association, 2013) and conservative estimations are from Borkar (2010).

using a GPU. Since the GPU up to this point was solely used for graphical purposes, several workarounds were done in order to adapt the inputs and outputs (for example, the input matrices must first be converted to image-like data structures that are readable by the GPU's graphical pipeline). Nonetheless, performance speedup is expected as compared to a matrix multiply performed in a CPU. During the following years, the GPU hardware evolved and programming languages were developed in order to provide a friendlier interface to the GPU as a matrix calculator. Examples of these languages

# 1.1 Field-Programmable Gate Arrays and High-Level Synthesis

include CUDA and OpenCL.

The Field-Programmable Gate Array (FPGA) is a device able to implement logic circuits and can be used in several applications ranging from arithmetic computations, glue logic, network-on-chips, etc. The FPGA is composed of an array of small components such as LookUp Tables (LUT), Flip-Flops (FF), Digital Signal Processors (DSP), and Block RAMs (BRAM). Additionally, a complex on-chip network system is provided to allow the routing between these components.

The FPGA technology is not recent, however it received more attention in the last years due to its natural low-power aspect. FPGAs operate in a frequency range that peaks around 500 MHz (HUTTON, 2015), and therefore the heat dissipation that is generated proportional to the frequency is greatly reduced, as compared to CPUs and GPUs that operate in the GHz level. FPGAs use the same transistor technology as from CPUs/GPUs and therefore they also suffer from static power leakage, which has been increasing over the last years (SEIFOORI *et al.*, 2018).

FPGAs differ significantly from CPUs in terms of programming. While on a CPU the developer writes a program containing a sequence of instructions to perform a given task, in the FPGA the developer must define computation units, the wiring between them, storage logic (registers, BRAMs) and the input/output interface. Considering a vector-add example for arrays with size N, Figure 3 shows the implementation approach on CPU and FPGA. For the FPGA, one must define add units, insert intermediate registers (if applicable), define the inputs/outputs, and connect all components.

(a) Example on CPU: the vector add is described as a sequential list of instructions that operates an Arithmetic Logic Unit (ALU).

(b) Example on FPGA: the vector add is performed in parallel, N adders are instantiated.

Modern CPUs are equipped with optimisations that do allow some parallelism and/or acceleration from sequential software (e.g. multiple cores, out-of-order execution). On the other hand, FPGAs enable true parallelism with an extended degree of freedom, as long as the device's resource and routing budget allows. For the example presented in the last figure, the FPGA design performs all adds in parallel.

FPGA designs are usually described using Register-Transfer Level (RTL) languages. These languages allow the developer to define the computation units, wires, registers, multiplexers, etc. RTL programming differs significantly from software. The developer must be aware of several constraints that are not common in the software world (e.g. timing constraints, synchronisation between different parallel parts of the design, etc.). Furthermore, debugging is tedious and time-consuming due to the significant time spent on compilation<sup>1</sup>.

The input/output interfacing is also not trivial. The designs programmed on an FPGA have direct access to input/output pins of the chip, which must then be interfaced accordingly (e.g. connected to a system bus, or even to simple push switches and LEDs). This also adds another layer of complexity for debugging, since internal values are usually not accessible without probes. However, there are modern FPGAs coupled with standard interfaces that provide a more intuitive usage. For example the Xilinx Zynq UltraScale+family of System-on-Chips (SoC) includes an ARM processor and an FPGA. Using vendor-specific drivers, it is possible to execute a Linux operating system on this platform, and use Linux-based APIs from Xilinx to interface with the FPGA.

### 1.1.1 High-Level Synthesis

FPGAs have been for a long time a niche architecture, used mostly by hardware design experts. Due to their non-trivial programming using RTL, they are still rather unpopular among high-level developers. As an alternative, High-Level Synthesis (HLS) tools provide means of transforming high-level input codes into FPGA hardware designs. Many HLS tools have been released over the last decades. Examples of popular HLS tools include Intel FPGA SDK for OpenCL, Xilinx Vivado HLS<sup>2</sup>, and LegUp.

Given a high-level source code, the HLS compiler applies several analyses to identify data dependencies between operations. Then, non-dependent operations are scheduled to occur in parallel and are allocated to synthesisable computation units known as Functional Units (FU). The customisable aspect of FPGAs allows the HLS compiler to freely decide the amount and type of FUs while balancing resource usage, routing complexity and timing constraints. Figure 4 presents a simplified view of a design generated by HLS compilers. A Finite State Machine (FSM) created by the compiler coordinates which data should be retrieved, computed, and stored at each clock cycle.

The output of the HLS compiler is an automatically generated hardware description (usually as an RTL code). Then, the automatically-generated RTL code is fed to the usual FPGA design synthesis that maps all RTL components to physical FPGA resources. Although HLS is usually not as time consuming as the whole FPGA synthesis and place-route process, it can still take significant time depending on the complexity of the input code (ZHONG *et al.*, 2016).

Performance is highly dependent on how well the HLS compiler extracts parallelism from the code and how well it adapts to the FPGA constraints. Software codes

<sup>&</sup>lt;sup>1</sup> Being a resource allocation and routing problem, FPGA synthesis may take from few minutes to several hours, and might even fail due to failed constraints.

<sup>&</sup>lt;sup>2</sup> Recently renamed to Xilinx Vitis HLS.

Figure 4 – Basic depiction of the hardware generated by an HLS compiler. Continuous lines represent data lanes, and dotted lines represent control lanes. Three FUs are shown in this example: two adders and one divider.

Source: Perina et al. (2021).

frequently contain structures and patterns that are dynamically defined (e.g. a dynamic data dependency, dynamic memory allocation). In these cases, the HLS compiler will either fail or take conservative paths that may severely impact the final performance. Hardware-orientated optimisations — either through manual code rewrite or through the use of compiler directives — are essential to achieve reasonable performance (ZOHOURI *et al.*, 2016; MUSLIM *et al.*, 2017; WELLER *et al.*, 2017).

# 1.2 Motivation and Objective