# **LEONARDO AMORESE GALLO GOMES**

Design of phase shifters in nanowire membrane technology and VCOs in CMOS technology at millimeter-waves for future full front-end integration

## LEONARDO AMORESE GALLO GOMES

# Design of phase shifters in nanowire membrane technology and VCOs in CMOS technology at millimeter-waves for future full front-end integration

## Versão corrigida

PhD Thesis prepared in a cotutelle presented at the Escola Politécnica da Universidade de São Paulo to obtain the title of Doctor in Science from the Universidade de São Paulo and the Université Grenoble Alpes

PPGEE – Programa de Pós-Graduação em Engenharia Elétrica da Escola Politécnica da USP (EPUSP) Concentration Area: Microeletrônica

EEATS – École Doctorale d'Electronique, Electrotechnique, Automatique et Traitement du Signal Area: NENTS – Nano Electronique et Nano Technologies

## Advisors:

Prof. Dr. Ariana M. L. C. Serrano (São Paulo)

Prof. Dr. Philippe Ferrari (Grenoble)

Co-advisor:

Prof. Dr. Gustavo Pamplona Rehder (São Paulo)

São Paulo / Grenoble (2023) Autorizo a reprodução e divulgação total ou parcial deste trabalho, por qualquer meio convencional ou eletrônico, para fins de estudo e pesquisa, desde que citada a fonte.

|               |            | do e corrigido em re<br>lo autor e com a an |        |      |

|---------------|------------|---------------------------------------------|--------|------|

| São Paulo,    | 14_de_     | Fevereiro                                   | de _   | 2023 |

| Assinatura do | autor:     | Seanando C.                                 | g. gon | ny   |

| Assinatura do | orientador | 18                                          |        |      |

## Catalogação-na-publicação

Gomes, Leonardo

Projeto de defasadores em tecnologia de membrana de nanofios e de VCOs em tecnologia CMOS em ondas milimétricas para integração futura em transceptor / L. Gomes -- versão corr. -- São Paulo, 2023.

148 p.

Tese (Doutorado) - Escola Politécnica da Universidade de São Paulo. Departamento de Engenharia de Sistemas Eletrônicos.

1.Microeletrônica 2.Oscilador 3.Defasador 4.Circuitos integrados 5.Ondas milimétricas I.Universidade de São Paulo. Escola Politécnica. Departamento de Engenharia de Sistemas Eletrônicos II.t.

## **ACNKOWLEDGMENTS**

Writing a doctoral thesis in the middle of a pandemic isn't a pleasant endeavor in any way, so I would like to express my wholehearted gratitude to everyone that helped me along the way, be it in the form of academic/technical or emotional support.

To my advisors and professors, Ariana, Philippe, Gustavo, Sylvain and Florence, for the guidance and help while conducting my work, both in Brazil and in France.

To the technicians at LME-USP, Thereza, Cristina, Rita, Alexandre and Igor for all the help with the fabrication processes I did. Also, to Loïc for the help during the measurement campaigns of my circuits.

To my wife, Karol. Your presence and love gave me the strength I needed to carry on my work.

To my parents, Wilson and Lígia, that gave me the support I needed to carry my studies.

To the friends I made along the way, Júlio, Marc, Renato, Tadeu and Mohammed. You helped me so much along the way, both technically and personally.

And finally, I would like to thank the Coordenação de Aperfeiçoamento de Pessoal de Nível Superior (CAPES) for funding my doctoral studies, both in Brazil and during my stay in France.

## **RESUMO**

Esta tese de doutorado está inserida no complexo contexto de telecomunicações em ondas milimétricas, abordando dois elementos importantíssimos de um transceptor nesta faixa de frequências: defasadores e osciladores controlados por tensão.

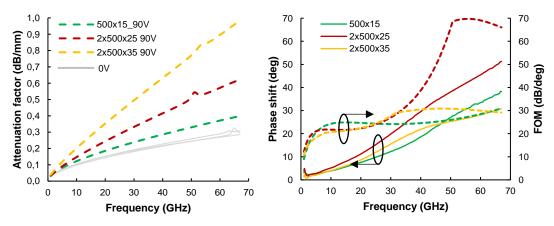

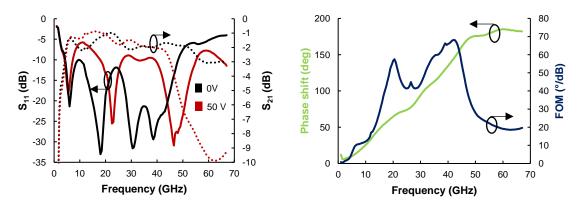

Os defasadores projetados neste trabalho são baseados na plataforma tecnológica da membrana de nanofios metálicos (MnM, acrônimo em inglês), utilizando linhas de onda-lenta suspensas e cristal líquido. As linhas suspensas têm a principal vantagem de apresentarem perdas de transmissão reduzidas devido às baixas oferecidas pelo ar, mantendo a redução de comprimento devido ao efeito de onda lenta. A adição de cristal líquido às linhas suspensas faz intensificar o efeito de onda lenta e permite o controle da velocidade de fase da linha. Este acréscimo tem como efeito adicional baixar a tensão de *pull-in* da linha suspensa, que pode funcionar como um defasador MEMS. O chaveamento eletrostático da linha causa uma variação importante na velocidade de fase. O resultado são defasadores compactos e com alta figura de mérito. Os valores de figura de mérito em 60 GHz são de 43.8 °/dB para a defasagem gerada apenas por cristal líquido e de 108 °/dB para a combinação do cristal líquido com o chaveamento eletrostático MEMS. Estes resultados mostram o forte potencial desta topologia para aplicações em ondas milimétricas.

Os osciladores controlados por tensão foram projetados numa tecnologia BiCMOS otimizada para aplicações em altas frequências, a BiCMOS 55-nm desenvolvida pela *ST Microelectronics*. Esta tecnologia disponibiliza dispositivos de alto desempenho, assim como um conjunto de camadas metálicas de baixas perdas em altas frequências. Os osciladores utilizam um circuito tanque inovador baseado em um ressoador de toco de quarto de comprimento de onda baseado em linhas coplanares de onda-lenta (S-CPS) carregadas periodicamente com varactores MOS. Foi desenvolvida a geometria do circuito tanque objetivando maximizar o controle do varactor na velocidade de fase da linha, assim como um procedimento de projeto que permite se determinar o melhor ressoador dado um conjunto de parâmetros de projeto. Além disto, foram explorados outros elementos ligados ao ressoador S-CPS: o primeiro é um estudo da configuração

da célula de compensação de perdas do circuito tanque; a segunda é a tomada de potência diretamente do tanque, sem a necessidade de amplificador *buffer* entre o tanque e a carga; terceiro e último, o emprego de chaves eletrônicas para se controlar um transformador sintonizável baseado em linhas S-CPS. Os osciladores projetados, centrados em 80 GHz, apresentam faixa de excursão de frequência superiores a 10 %, com figura de mérito melhor do que -170 dB, tendo sido projetado um oscilador com banda de oscilação de quase 20 GHz, cobrindo a banda-E completamente e continuamente. Estes resultados demonstram que o ressoador S-CPS é uma topologia muito poderosa, inovadora e flexível que permite o projeto de osciladores compactos e de alto desempenho para aplicações em ondas milimétricas.

Palavras-chave: CMOS, ondas milimétricas, microeletrônica, circuitos integrados, oscilador, defasador, interposer, linha de onda lenta, óxido de alumina anódica (AAO), telecomunicações.

# **RÉSUMÉ**

Cette thèse de doctorat concerne le domaine des circuits et systèmes de communication en bande millimétrique, avec un focus sur deux éléments importants d'un transceiver, à savoir les déphaseurs et les oscillateurs commandés en tension (VCOs).

La première partie de la thèse concerne la conception, la réalisation et la caractérisation de déphaseurs. Une technologie de type membrane à nanofils métalliques a été utilisée pour les déphaseurs, utilisant à la fois des lignes suspendues de type MEMS et des cristaux liquides comme éléments d'accord. Les lignes suspendues possèdent l'intérêt de conduire à des pertes d'insertion faibles du fait que le diélectrique est l'air. Elles sont miniaturisées grâce à un effet d'onde lente obtenu par l'utilisation d'un lit de nanofils métalliques verticaux sous le ruban d'une ligne microruban. L'insertion des cristaux liquides sous le ruban suspendu permet de contrôler la constante diélectrique effective de la ligne, et donc le déphasage engendré. Cela accentue également l'effet d'onde lente du fait de la constante diélectrique des cristaux liquides, mais en contrepartie bien sûr conduit à une augmentation des pertes diélectriques

Cela conduit également à un effet très positif en abaissant la tension de « pull-in » de l'aspect MEMS.

Le cumul des deux effets (cristaux liquides et MEMS) a permis de démontrer des déphaseurs compacts et performants. La figure de mérite obtenue atteint ainsi 43.8 °/dB avec un contrôle uniquement basé sur la polarisation des cristaux liquides, et 108 °/dB lorsque les deux effets sont combinés. Ces résultats à l'état de l'art montrent le potentiel élevé de la technique utilisée pour la réalisation de déphaseurs en bande millimétrique.

La seconde partie de la thèse concerne la conception, la réalisation et la caractérisation de VCOs, en technologie BiCMOS 55 nm de STMicroelectronics.

Cette technologie propose des actifs hautes performances au sein du Front-End-Of-Line ainsi qu'un Back-End-Of-Line très performant pour la conception des passifs. Les VCOs étudiés au sein du la thèse utilisent des résonateurs innovants basés sur des lignes de type CPS (« Coplanar Stripline ») à ondes lentes, chargées périodiquement par des varactors de type AMOS (« Accumulation MOS »). Plusieurs générations de VCOs ont été réalisées.

La première réalisation a concerné le développement d'une topologie de résonateur permettant de maximiser la variation de phase des résonateurs à travers le contrôle de la capacité des varactors, grâce à une procédure de design permettant une optimisation automatique à partir d'un jeu de paramètres de design.

Par la suite, d'autres innovations ont été apportées à cette première réalisation :

- Une étude permettant d'optimiser la configuration du circuit de compensation des pertes,

- Une topologie sans buffer, permettant de réduire de manière drastique la consommation,

- L'utilisation de switchs permettant de commuter deux résonateurs afin d'élargir la bande d'accord des VCOs.

Toutes les générations de VCOs ont été conçues en bande E autour de 80 GHz, avec un objectif d'accord en fréquence au minimum de 10%. La figure de mérite de l'ensemble des générations est meilleure que -170 dB.

La dernière génération basée sur des résonnateurs commutés permet d'envisager un accord de l'ordre de 20% permettant de couvrir la totalité de la bande E.

L'ensemble des résultats obtenus montre ainsi que l'approche utilisant des résonateurs basés sur des lignes à ondes lentes de type CPS offre un fort potentiel, que ce soit en termes de performances ou de flexibilité de design permettant d'obtenir des résonateurs très compacts en bande millimétrique. Remarquons que cela peut paraître paradoxal de vouloir fournir des efforts en termes de miniaturisation en bande E où la longueur des lignes devient modérée, mais ce serait oublier le coût des technologies qui croît de manière exponentielle avec la performance des actifs et des passifs, nécessitant ainsi des efforts importants en termes de miniaturisation.

Mots clés : Technologie CMOS, technologie membranes à nanofils, ondes millimétriques, microélectronique, oscillateurs, déphaseurs, lignes à ondes lentes, télécommunications.

## **ABSTRACT**

This doctoral thesis is inserted into the complex context of millimeter-wave telecommunications, dealing with two very important elements in a transceiver for such frequencies: phase shifters and voltage-controlled oscillators.

The phase shifters designed in this work are based on the metallic nanowire membrane technology platform (MnM), using suspended, slow-wave lines and liquid crystal. The suspended lines have the main advantage of showing low transmission losses, thanks to the absence of losses of air, keeping the length reduction thanks to the slow-wave effect. The insertion of liquid crystal to the suspended lines intensifies the slow-wave effect and allows the phase velocity controls of the line. Also, it lowers the pull-in voltage of the line, allowing it to work as a MEMS phase-shifter. This electrostatic switching causes a significative decrease of phase velocity, resulting in compact and high-performance phase shifters. The values for the figure of merit are 43.8 °/dB for a pure liquid crystal phase shifter and 108 °/dB for a phase-shifter that combines the phase shift generated by the liquid crystal and MEMS switching. These results show the strong potential of this topology for millimeter wave applications.

The voltage-controlled oscillators were designed in a RF-oriented BiCMOS technology, the 55-nm BiCMOS technology developed by ST Microelectronics. This technology offers high-performance devices and a low-loss back-end. The oscillators use a novel tank circuit based in quarter-wavelength stubs based in slow-wave coplanar striplines (S-CPS) periodically loaded by MOS varactors. The design started with the development of a resonator topology that maximizes varactor control over the phase velocity of the line, as well as a design procedure that enables the determination of the best possible resonator, given a set of design parameters. Also, some other elements of the oscillator were explored: first, the study of the tank loss compensation configuration; second, a bufferless topology, where the output power is derived directly from the tank circuit; third and last, the use of electronic switches to control a tunable transformer based on S-CPS. The oscillators were designed having a center frequency of 80 GHz and all have a frequency tuning range better than 10 %, while displaying a figure of merit better than -170 dB. One of the oscillators displayed a frequency tuning

range of almost 20 %, covering the E-band completely and continually. These results show that the varactor-loaded S-CPS resonator is an innovative oscillator topology that is very powerful and flexible, enabling the design of compact and high-performance oscillator of millimeter-wave applications.

Key words: CMOS, millimeter waves, microelectronics, integrated circuits, oscillator, phase shifter, interposer, slow-wave line, anodic aluminum oxide (AAO), telecommunications.

# **CONTENTS**

| 1 | Intro | duction14                                                         |

|---|-------|-------------------------------------------------------------------|

|   | 1.1   | Context of this thesis14                                          |

|   | 1.2   | Objective17                                                       |

|   | 1.3 E | Bibliographical analysis and state of the art18                   |

|   | 1.3.1 | Phase-shifters19                                                  |

|   | 1.3.2 | CMOS voltage-controlled oscillators at E-band20                   |

| 2 | Mnm   | technology phase shifters25                                       |

|   | 2.1   | Overview of the MnM interposer technology26                       |

|   | 2.2 N | MnM phase shifter27                                               |

|   | 2.2.1 | Suspended microstrip lines28                                      |

|   | 2.2.2 | Liquid crystal MnM phase-shifter37                                |

|   | 2.2.3 | Conclusions55                                                     |

| 3 | CMC   | S E-band Voltage-controlled oscillators57                         |

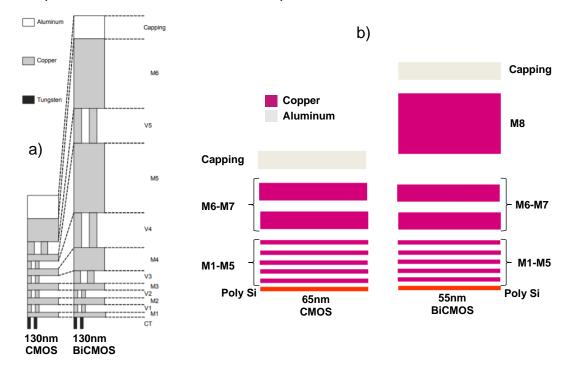

|   | 3.1   | Fechnology of choice: STM 55-nm BiCMOS61                          |

|   | 3.1.1 | Front-end capabilities61                                          |

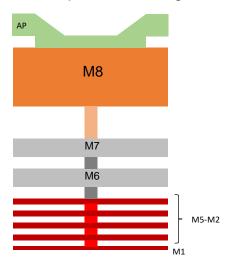

|   | 3.1.2 | Back-end capabilities62                                           |

|   | 3.2   | Slow-wave Coplanar Striplines (S-CPS)63                           |

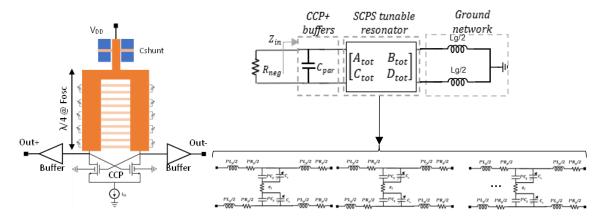

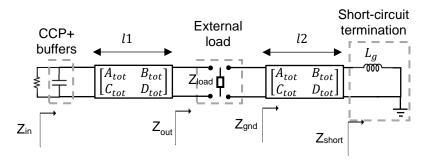

|   | 3.3   | Standing-wave oscillator based on distributed S-CPS resonator     |

|   | 6     | 88                                                                |

|   | 3.3.1 | Distributed S-CPS resonator68                                     |

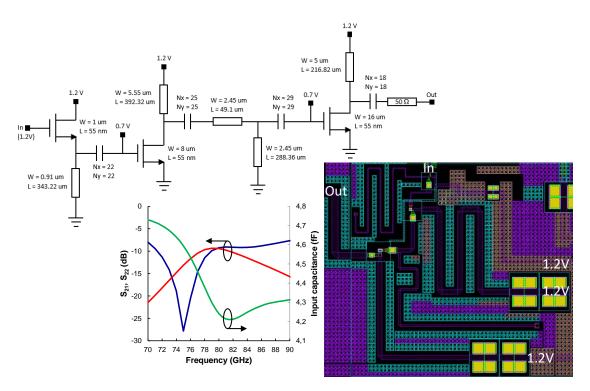

|   | 3.3.2 | MOSFET cross-coupled pair74                                       |

|   | 3.3.3 | Buffer76                                                          |

|   | 3.3.4 | Oscillator design77                                               |

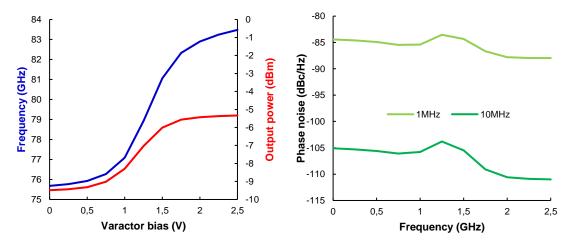

|   | 3.3.5 | VCO results85                                                     |

|   | 3.3.6 | Discussions87                                                     |

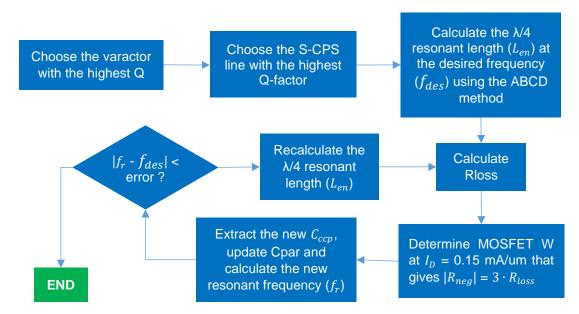

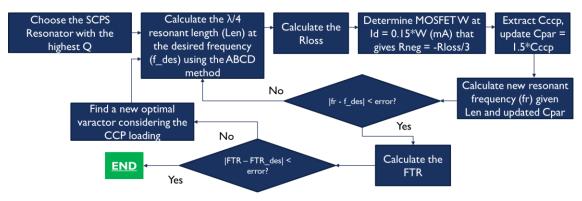

|   | 3.4   | Optimized design algorithm for the standing-wave oscillator based |

| on dis  | tributed  | S-CPS resonator                                     | 88         |

|---------|-----------|-----------------------------------------------------|------------|

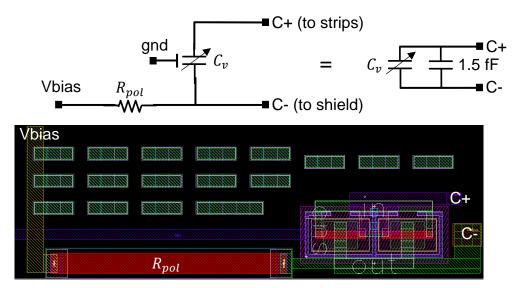

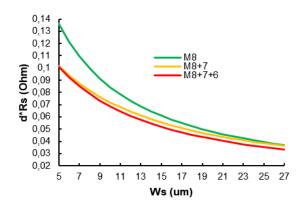

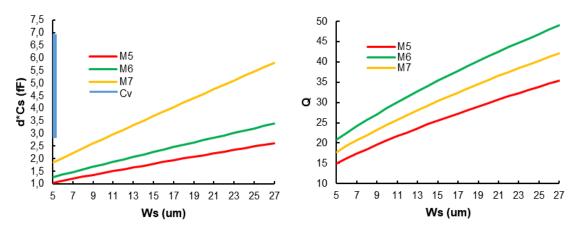

|         | 3.4.1     | Loaded S-CPS optimization                           | 89         |

|         | 3.4.2     | Reduction of the parasitic loads                    | 93         |

|         | 3.4.3     | Optimized VCO design                                | 96         |

|         | 3.4.4     | VCO results                                         | 98         |

|         | 3.4.5     | Discussions                                         | 99         |

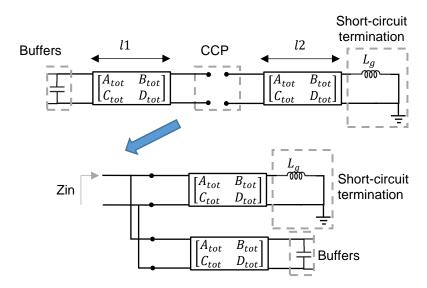

| 3       | 3.5 S     | Standing-wave oscillator based on distributed S-CPS | resonator  |

| with di | istribute | d negative resistance                               | 101        |

|         | 3.5.1     | Working principle                                   | 101        |

|         | 3.5.2     | Equivalent model of the resonator                   | 102        |

|         | 3.5.3     | The different methods of distributing the CCP $gm$  | 104        |

|         | 3.5.4     | Reference case VCO                                  | 107        |

|         | 3.5.5     | Shifted CCP VCO                                     | 109        |

|         | 3.5.6     | Distributed CCP VCO                                 | 112        |

|         | 3.5.7     | Shifted, distributed CCP VCO                        | 115        |

|         | 3.5.8     | Comparison of the designed VCOs                     | 117        |

|         | 3.5.9     | Discussions                                         | 118        |

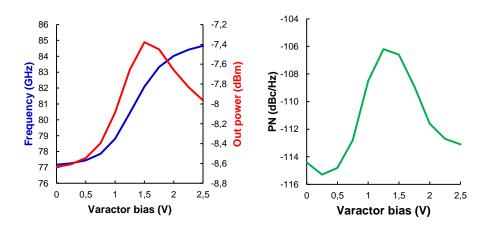

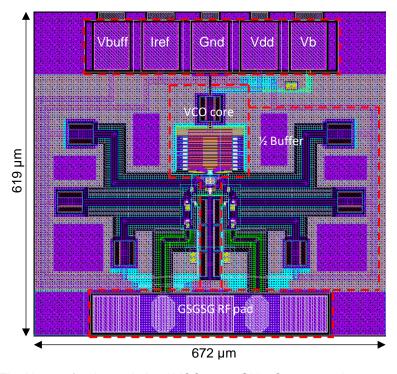

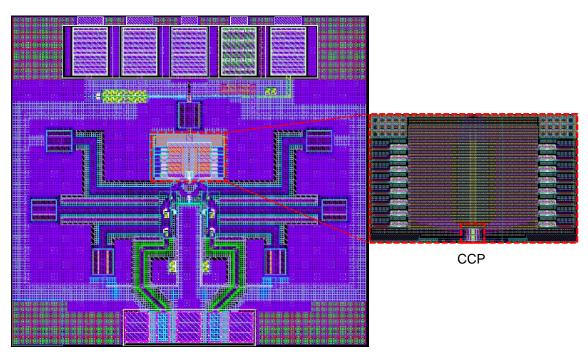

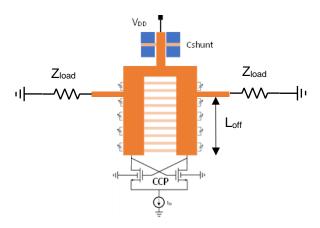

| 3       | 3.6 B     | Sufferless Voltage controlled oscillator            | 118        |

|         | 3.6.1     | Working principle                                   | 118        |

|         | 3.6.2     | Bufferless VCO design                               | 119        |

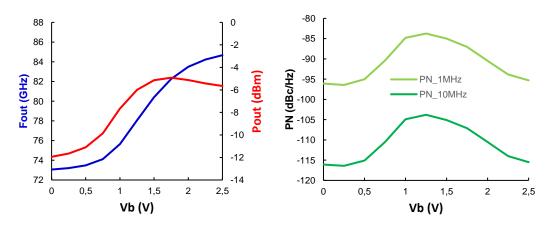

|         | 3.6.3     | VCO results                                         | 120        |

|         | 3.6.4     | Discussions                                         | 124        |

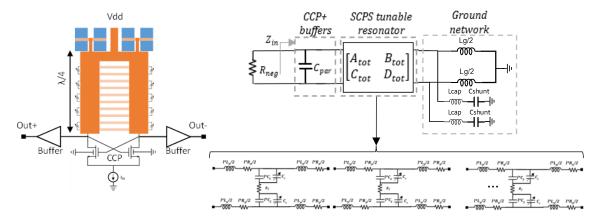

| 3       | 3.7 B     | Sand-switching, coupled-resonator standing-wave     | oscillator |

| based   | on Tun    | able S-CPS transformer                              | 126        |

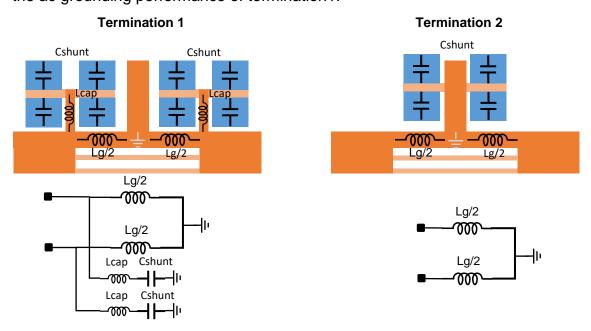

|         | 3.7.1     | Working principle                                   | 126        |

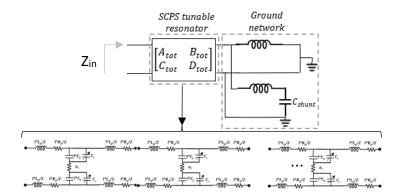

|         | 3.7.2     | tunable S-CPS transformer model                     | 127        |

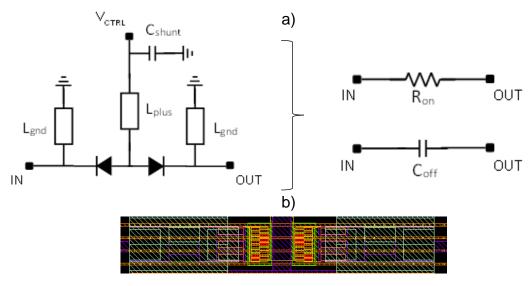

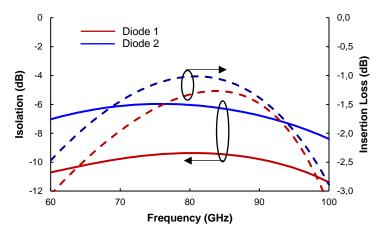

|         | 3.7.3     | Choice and design of RF switch                      | 130        |

|         | 3.7.4     | VCO core design                                     | 133        |

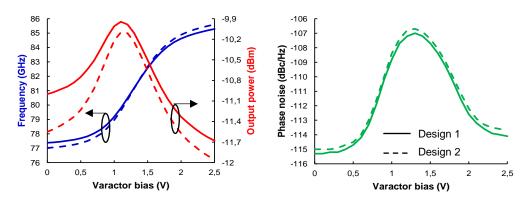

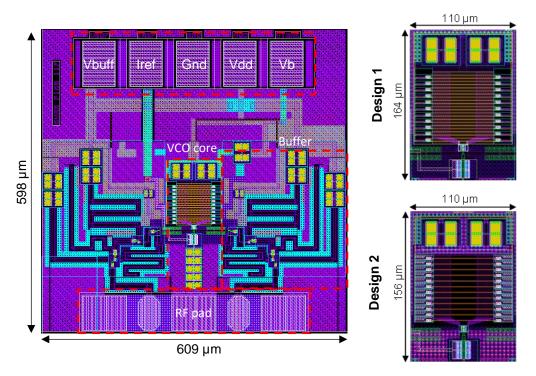

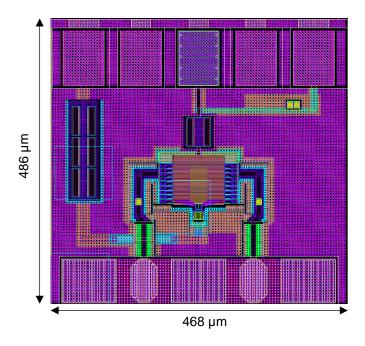

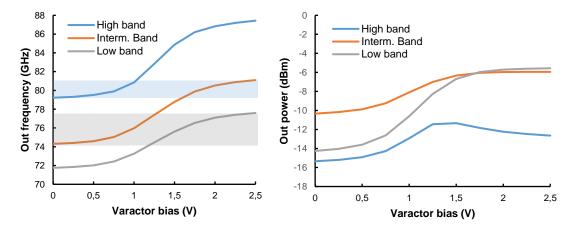

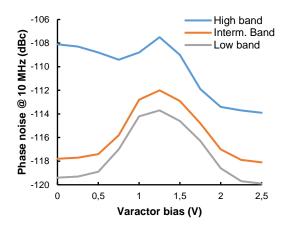

|   | 3.7.5 VCO results | 135 |

|---|-------------------|-----|

|   | 3.7.6 Discussions | 139 |

| 3 | 3.8 Conclusions   | 140 |

| 4 | Conclusion        | 143 |

| 5 | References        | 145 |

## 1 INTRODUCTION

#### 1.1 CONTEXT OF THIS THESIS

Human society has been evolving the way of transmitting knowledge and information ever since the invention of the written language. We, as a society, have come a long way since the first clay tablets have been written: in this rather long meantime we have invented the press, which printed standardized letters onto a paper sheet, greatly quickening the production of books; we have invented radio communications, which transmit information by means of electronically mixing an audio signal to a high-frequency carrier and propagate it on air; we have invented the internet, a medium of transmitting and accessing packets of digital data in a scale and breadth never ever dreamt before. We have received data from the far ends of the solar system, billions of kilometers away. We now have the means of knowing what goes on at the other side of the planet almost in real time. And, with our ever-increasing capability for communication and transmitting information and knowledge, the innate human drive for more keeps pushing the installed telecommunication facilities on, stressing the infrastructure and calling for innovative solutions for current problems and for new technologies and techniques for solving problems that are yet to come.

This need for higher bandwidth is clearly seen by looking at the different specifications for the cellular network generations since the first iteration, or 1G, from the 1980's. Cellular network then was in place to carry analog communications between users in range of a retransmitting antenna. Then, in the 1990's, 2G allowed the digital transmission of the voice signal, which increased call quality, and enabled simple data transfer capability to the users, like SMS messaging and, at the end of its life cycle, simple internet access. In the 2000's, 3G enabled users to access the internet and upload/download images and audio, with download speeds up to 10 Mbps. The 2010's saw the 4G, which high-speed internet connection and bandwidth, with download speeds up to 1 Gbps. This generation enabled the end-user to benefit from high-definition voice transmission, mobile TV, HD video streaming, gaming services, etc.

The ongoing Covid-19 pandemic, at the time of the writing of this manuscript, demanded lockdown and social isolation measures to be taken across the world, which drove the demand for internet connectivity higher than

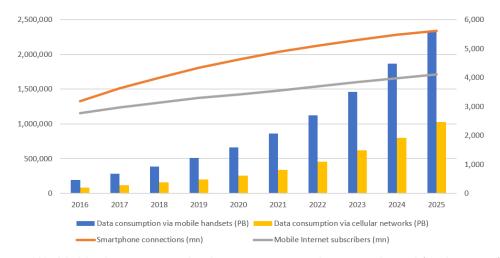

never before [1], both on fixed and cellular networks. This, of course, added to the increasing tendency in data consumption. According to Figure 1, the volume of data consumed in both cellular and fixed networks almost quadrupled in the period between 2016 and 2021. Cellular network alone saw a jump from 86 petabytes to 335 petabytes in this period. The increasing number of users and the necessary bandwidth to accommodate them plus and to enable new functionalities, makes it necessary to move forward again.

Figure 1 – Worldwide data consumption between 2016 and 2021 and trend for the near future, between 2022 and 2025. Source:[2]

The 5G is in the process of being adopted in various urban centers across the world, having reached the number of 1662 cities across 65 countries as of 2021 [3]. This fifth-generation cellular network is aimed for massive multiple input and multiple output (MIMO) networks with capabilities to enable gigabit download speeds, as much as 20 Gbps 5G will be able to accommodate end-user applications such as ultra-HD video streaming, real-time HD video calls, virtual reality, wearable wireless devices, etc. Also, the massive bandwidth is being aimed to accommodate the Internet of Things (IoT) devices that are expected to be deployed in the following years.

One of the new solutions and technologies being brought with the 5G standard are the wireless links using millimeter-waves (mmW), which comprises the frequency range from 30 GHz up to 300 GHz. By increasing the carrier frequency, the link is capable of providing more bandwidth to the end users, which solves the problem of accommodating more, data-hungry users. However, this gain in bandwidth comes at a price: mmW have more free-path losses, and are

more easily absorbed by walls and foliage, which calls for another change of perspective regarding the design of mmW links, which shifts from long-range, broadcasting links to smarter, shorter-range links. Example of mmW bands that have been allocated is: 24-30 GHz for 5G mm-wave links, the unlicensed 57-66 GHz (V-band) for high-speed, short-range links such as IEEE 802.11ad protocol, the 71-76 GHz, 81-86 GHz bands (E-band) for backhauling and 76-81 GHz for automotive radar, etc.

To compensate for the propagation losses, the transmission gain must be increased, and the most power-efficient way to do so is to employ antenna arrays to focus the radiated power. This, however, also comes with a price: the antenna array cannot illuminate a wide solid angle anymore, so the mmW beam needs to be steered to illuminate the end-users. One technique to do so is to employ a beam-steerable front-end: the antennas are fed by phase-shifters, and by carefully changing the phase on each antenna, the radiation direction can be changed.

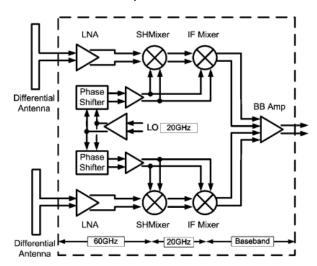

A mmW beam-steering transceiver front-end is a complex system that needs to tackle a number of tasks: from amplification to signal generation, mixing and up/down conversion, signal switching and filtering and the electronic steering of the antenna array irradiation pattern. The basic block diagram for a beam-steering front-end is shown in Figure 2, where a 2-antenna, 60 GHz receiver RFIC implemented in 130-nm CMOS is depicted.

Figure 2 – Block diagram of a 2-antenna, monolithic beam-steering front-end at 60 GHz implemented in a 130 nm CMOS process. Here only the antennas and low-noise amplifiers are implemented in the carrier frequency, the sub-harmonic mixer, intermediate frequency mixer and local oscillator are implemented in the intermediate frequency, 20 GHz. Source: [4]

Here the basic building blocks can be seen: low noise amplifiers to amplify the incoming signal; phase-shifters to realize the beam-steering; power combiners; a local oscillator; and a base-band amplifier to boost the power level of the demodulated signal. It is straightforward to say that a transmitter would employ power amplifiers and power dividers instead. Other examples of such front-ends at 60 GHz and 26 GHz-28 GHz include [5] [6] [7] [8] [9].

The designer needs to choose the topology carefully. The front-end can all be done in the carrier frequency, reducing the die area as the lambda-based components, such as phase-shifters, power divider and interconnecting transmission lines, will be scaled down, but this will increase their insertion loss to a degree. Also, it would increase the burden on the active circuits, as the transistors will be invariably working close to their cutoff frequency, thus increasing the DC power consumption, reflecting the higher transconductance  $(g_m)$  needed to maintain the desired performance parameters. On another hand, some parts could be designed to work on the intermediate frequency, but that would increase the number of mixers in the circuit, as each branch would require a separate up/downconversion mixer, increasing the circuit complexity. Not considering whether the antennas would be implemented on chip, on the package or on the interconnection substrate, each posing their own benefits and shortcomings. Thus, there is not a simple, "one-size-fits-all" solution for designing a beam-steering, mmW front-end.

#### 1.2 OBJECTIVE

This doctoral thesis is inserted in this high-frequency and high-complexity context. The goal of this work is to design two of the building blocks of a high-performance, mmW beam-steering front-end: a voltage-controller oscillator (VCO) at 80 GHz and a phase shifter at 60 GHz.

The reason to have chosen these two very different blocks is the nature of the design and the importance of these blocks. Even though an oscillator and a variable transmission line are two very dissimilar devices, they both employ the same concept at their core: they are electrically-tunable devices which employ some kind of variable capacitance to achieve their goal, either generating different output frequencies or having different conduction phase. VCOs are one of the most important building blocks in a transceiver, either in the generation of

the carrier frequency, LO frequency or clock in phase-locked loop systems. Phase-shifters are the parts that will create the electric phase shift that will steer the antenna array beam, thus they are one of the core devices of a mmW beam-steering front-end.

The phase-shifters will be realized using the Metallic-nanowire-Membrane (MnM) technology platform, for their high-performing passive devices, developed at the *Laboratório de Microeletrônica da Universidade de São Paulo* (LME-USP). The VCO will be designed in an advanced, RF-optimized BiCMOS technology developed by STMicrolectronics. Both designs will be made around slow-wave transmission lines for their compactness and improved electrical performance over traditional microstrip lines.

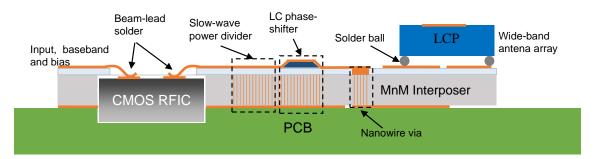

This doctoral thesis marches toward the design of a mmW front-end with beam-steering capabilities. This front-end would utilize the MnM technology platform to realize the RFIC integration and off-chip passive devices, because of its reported high-performance devices and low fabrication cost. The RFICs would be designed using (Bi)CMOS processes, since they enable well-performing circuits at a competitive cost when compared to III-V processes. Figure 3shows a cross-section of such a mmW front-end, showing several devices and integration techniques that are either already developed (such as the nanowire vias and the LCP-MnM antenna) or in development as part of the research work of other colleagues.

Figure 3 - Cross-section of a MnM-based mmW front-end, showing several devices and integration techniques to realize it. Source: author.

## 1.3 BIBLIOGRAPHICAL ANALYSIS AND STATE OF THE ART

This section will present a brief state-of-the-art on mmW phase-shifters and CMOS-based VCOs.

#### 1.3.1 Phase-shifters

Phase shifters can be classified in two categories: active and passive phase-shifters. Active phase shifters consume power and suffer from some non-linearities [10,11], leading to complex thermal dissipation mechanisms for systems with large antenna array. Hence, they are not envisioned in this project.

Several technologies have been used to develop passive phase shifters at mmW, including CMOS/BiCMOS, BST, Liquid Crystal and MEMS. A brief state-of-the-art shows that the phase shifters demonstrated so far either exhibit unacceptable insertion loss, or occupy large surfaces.

A careful comparison of phase shifters realized in all these technologies is not simple, since one has to consider not only the size and the electrical performance, but also the cost, the reliability, and, especially for MEMS, the packaging issue. Here, the phase shifters are only compared in terms of size and electrical performance. The classical Figure of Merit (FOM) is used, defined by the ratio of the maximum phase shift over the maximum insertion loss.

Contrary to MEMS phase shifters, their CMOS/BiCMOS counterparts offer much smaller footprint (0.075 mm² [12] and 0.034 mm² [13]) in a Reflection-Type Phase Shifters (RTPS), but their electrical performance is poor (11°/dB [12] and 13°/dB [13]) since MOS varactors used as tuning elements exhibit Q-factors limited to about 10 at mmW [14]. However, the reduced area yields a high FOM /Area ratio (146°/(dB·mm²) [12] and 382°/(dB·mm²) [13]).

In general, BST-based devices show good electrical performance at RF frequencies, however, the BST loss tangent increases dramatically with frequency, which limits its electrical performance at mmW. For example, [15] reports a FOM of 23°/dB with a footprint of 1.2 mm² at 60 GHz.

Liquid crystal-based phase shifters can show a high FOM at higher frequencies, since LC loss tangent decreases with frequency [16]. A FOM of 42°/dB at 76 GHz was reported in [17]. However, due to the moderate variation of the dielectric constant of the LC, the area of LC phase shifters is usually large, 0.65 mm² in this case. In [18], a slow-wave CPW (S-CPW) was combined with MEMS and LC to take advantage of their high FOM, while reducing the size and response time of the phase shifter. A FOM of 52°/dB at 45 GHz with a 0.38 mm² footprint was obtained. In [19], a continuously tunable phase shifter using a LC-

filled stripline realized on LTCC was demonstrated. The total area occupied by the stripline and LC is 14.6 mm<sup>2</sup>, leading to a FOM greater than 47°/dB between 30 GHz and 34 GHz.

Another type of passive phase shifter is being developed by USP-LME and TU-Darmstadt, Germany in the framework of the DFG project "Novel continuously tunable and miniaturized passive Slow-Wave Phase Shifters with fast response time for millimeter wave applications based on a combined Liquid Crystal (LC) and Nanowire-filled Membrane Technology" in order to develop a liquid crystal-based phase shifter on the MnM. This novel phase shifter uses the MnM slowwave microstrip line, enabling area reduction and, because it is fabricated directly on the MnM substrate, ease of integration with the rest of the beam-steering frontend. [20]

#### 1.3.2 CMOS VOLTAGE-CONTROLLED OSCILLATORS AT E-BAND

An electronic oscillator can be simplified down to an inductor-capacitor resonant circuit fed back by an inverting amplifier. The resonator has a selfoscillating frequency, at which its equivalent impedance will be purely real and equal to its equivalent losses, caused by ohmic losses in the conductors, dielectric losses due to the periodic repolarization of electrical dipoles in the capacitor's dielectric, substrate losses due to eddy currents in the case of an integrated resonator, etc. These losses naturally cause power dissipation in the resonator, resulting in an exponentially-fading output - the resonator will ring, oscillate for a short time until the signal fades out. If the feedback amplifier can (over)compensate this dissipation, the ringing can be indefinitely sustained, and an oscillator is created. This is a rather extensive explanation of the Barkhausen criterion: oscillation in a closed-loop system will occur always when the closedloop gain is equal to 1. If this gain is larger than 1 in magnitude, the system is unstable and its output would rise exponentially, thus a self-sustaining oscillator has to have some sort of gain limiting mechanism to prevent self-destruction or other undesired effects. In the case of the electronic oscillator there is an inherent self-limiting mechanism thanks to the strong non-linearity large signal behavior of a transistor: the voltage gain drops abruptly when the signal amplitude is closer to either power rail (i.e., to ground or to V<sub>DD</sub>). This causes the average gain to remain stable, and the oscillations, self-sustained.

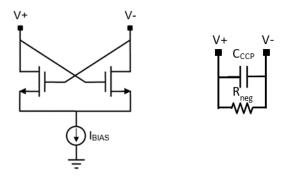

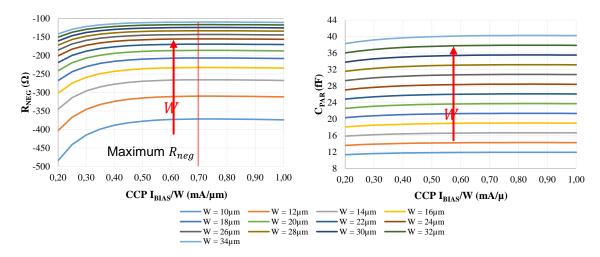

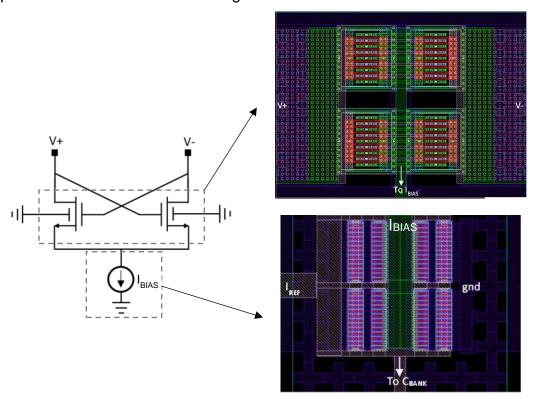

The feedback amplifier can be modelled as a negative resistance in parallel with the equivalent losses of the resonator, and its exact realization will depend on the design. One of the most popular topologies for the loss-compensation amplifier in CMOS technologies is the cross-coupled pair (CCP), which can be understood as two cascaded, tuned and fed-back common-source amplifiers.

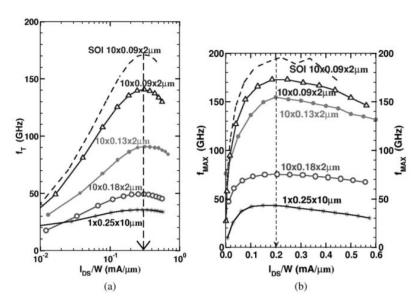

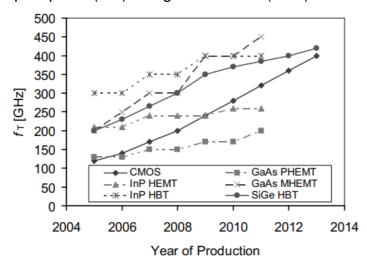

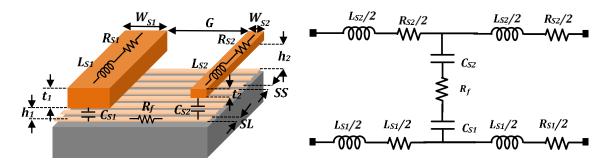

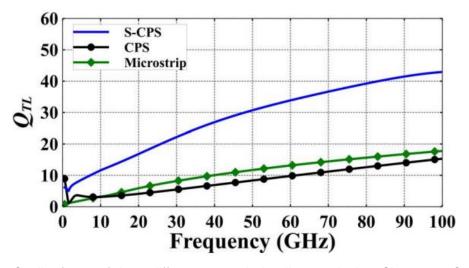

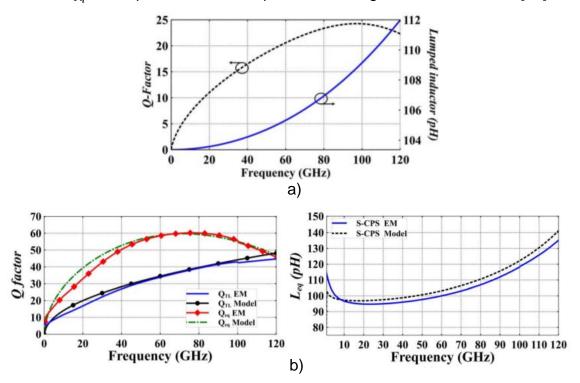

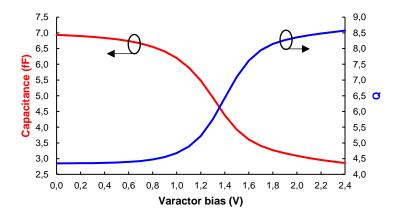

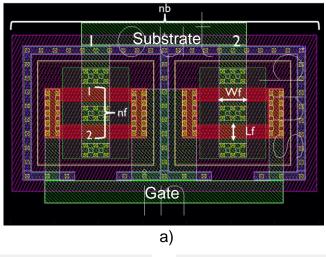

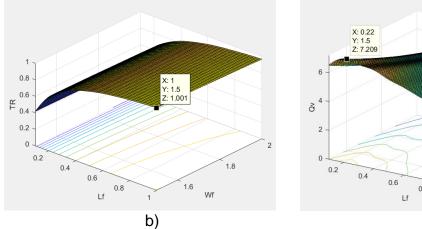

A voltage-controlled oscillator (VCO) is an oscillator whose output frequency is controlled by an electric input. The frequency tuning mechanism is usually done with a variable capacitance, or varactor, which is a voltage-controlled capacitor. Thus, the most basic kind of VCO is based on a varactor-inductor tank [21]. For monolithic VCOs, the inductor is realized by a planar coil realized on the backend of the chip and the varactor, either using a reverse-biased diode or a metaloxide-semiconductor (MOS) capacitor. The inductor-varactor tank performs very well up until the upper limit of the microwave band, as the quality factor (Q-factor) of both the inductor and MOS varactor is well above 10 at frequencies below 10 GHz [22]. At mmW, however, the Q-factor of MOS varactor suffers a dramatic drop, dominated by the gate series resistance [23], and their low Q-factor dominates the Q-factor of the resonant tank. Inductors also do suffer from Qfactor drop, especially because of conductor ohmic losses and substrate losses. Nevertheless, improving the inductor Q-factor still improves the overall Q-factor of the Tank, but the mechanisms to improve the Q-factor have some particularities because of effects that happen at mmW: for example, the patterned ground shield, which is an efficient solution to shield the substrate from the eddy current losses at microwave frequencies, turns to be detrimental in mmW because of their own losses [24]. One proposed workaround is to realize the inductors as stubs of slow-wave coplanar waveguides (S-CPW), whose Q-factor can be higher than 30 at mmW [25]. However, even if a custom inductor displays better Q-factor than a standard, planar inductor, the Q-factor of the resonator is still dominated by the varactors.

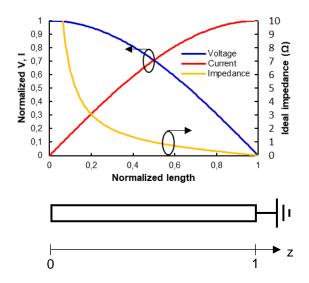

The use of standing-wave resonators instead of lumped inductor-capacitor tanks was proposed to improve the Q-factor of the resonator [26]. This kind of oscillator is called a standing-wave oscillator (SWO). In this kind of oscillator, the resonant frequency happens at frequencies where the electrical length of the transmission line equals odd multiples of  $\lambda/2$  for open-circuit-terminated stubs [27] [28] or odd multiples of  $\lambda/4$  for short-circuit-terminated stubs, with the

possibility of multi-mode, or multi-band oscillation by loading the stub to force a degenerate resonant mode [27] [29]. However, the main bottleneck still remains the low Q-factor of monolithic varactors. To avoid use of varactors inside the resonator, [30] proposes the use of digitally-controlled transmission lines acting as switched capacitors. The Q-factor is indeed improved thanks to a high-quality differential transmission line, but the frequency tuning is not continuous, which can be a limiting factor in some applications.

## 1.3.2.1 VCO Figures of Merit

The importance of a high-Q resonator is that the phase noise of an oscillator is inversely proportional to the Q-factor of its tank. Random noise in an oscillator loop will cause two types of perturbations in the output signal: amplitude noise, which is random fluctuation on the signal amplitude, and phase noise, random shifts in the signal phase. The feedback loop of an oscillator rejects amplitude noise, but there is no compensation mechanism for phase noise. The phasenoise can be expressed as shown by Leeson's phase noise equation:

$$L(\Delta\omega) = 10\log_{10}\left[\frac{2kT}{P_{sig}} \cdot \left(\frac{\omega_0}{2Q\Delta\omega}\right)^2\right] \tag{1}$$

where  $L(\Delta\omega)$  is the phase noise at a  $\Delta\omega$  offset from the fundamental, T is the absolute temperature, k is the Boltzmann constant,  $P_{sig}$  is the signal power available at the feedback amplifier's input,  $\omega_0$  is the oscillating frequency, and Q is the loaded Q-factor of the resonator. This equation helps offer insight into the phenomena that contribute to phase noise, rather than offering an accurate value for it. Phase noise is inversely proportional to  $P_{sig}$  and to Q. Thus, to reduce the phase noise, either the tank Q-factor or the  $P_{sig}$  need to be increased. Increasing  $P_{sig}$  will result in an increase in DC power consumption, which isn't always desirable. However, increasing the tank Q-factor will also have the effect of reducing the required DC power consumption to ensure oscillation startup, consequently increasing  $P_{sig}$ . In conclusion, the design of a high-Q resonator is very important for a high-performance VCO.

The phase noise is quantified as the power relative to the carrier frequency on a bandwidth  $\Delta f$  around the carrier, measured in dBc/Hz. For mmW VCOs, a

phase noise below -100 dBc/Hz at  $\Delta f = 1$  MHz is desirable.

One metric used to quantify the performance of an oscillator is the classical figure of merit (FOM), which is defined as:

$$FOM = PN - 20 \cdot log\left(\frac{F_{osc}}{\Delta f} + \frac{FTR}{10}\right) + 10 \cdot log\left(\frac{P_{diss}}{1mW}\right)$$

(2)

where PN is the best-case phase noise in dBc/Hz,  $F_{osc}$  is the center oscillation frequency,  $\Delta f$  is the frequency offset where the phase noise is measured, FTR is the frequency tuning range in percent and  $P_{diss}$  is the DC power consumption of the VCO core. The smaller this FOM is, the better the VCO.

Another way of characterizing the VCO is by calculating its DC to RF efficiency. To keep the comparison fair, the efficiency calculated in this work will consider all DC power dissipation, both from the VCO core and from the buffers. The DC to RF efficiency is calculated, then, as:

$$Eff = \frac{10^{\frac{Pout+3dB}{10}}}{V_{DD} \cdot (I_{total})} \tag{3}$$

where V<sub>DD</sub> is the supply voltage, I<sub>total</sub> is the total current consumption of the VCO (i.e., core consumption plus helper circuits such as buffers) and P<sub>out</sub> is the single-ended power output in dBm. Since a CCP VCO is a differential circuit by nature, and because both outputs are symmetrical, the total differential output power is the double of the single-ended output power, which translates to adding 3 dBm to P<sub>out</sub>.

#### 1.3.2.2 State-of-the-art

Table 1 contains the state-of-the-art of monolithic, CMOS-based VCOs. This revision focuses on continuously-tunable VCOs, or in VCOs that have some mechanism of band-switching to widen its tuning range. The VCOs contained in this state-of-the-art employ the same basic topology, that is, a resonating tank fed back by a negative resistance cell. Thus, excluding techniques such as injection locking or coupled resonators.

Table 1 - Monolithic CMOS VCO state-of-the-art.

| Ref.   | Tech.       | Fosc  | Cont.<br>FTR | $P_{DC}^{\#}$ | <i>PN</i> @<br>10 MHz | FOM@<br>10 MHz | P <sub>out</sub> ## |

|--------|-------------|-------|--------------|---------------|-----------------------|----------------|---------------------|

|        |             | (GHz) | (%)          | (mW)          | (dBc/Hz)              | (dBc/Hz)       | (dBm)               |

| [25]   | 65-nm CMOS  | 76.5  | 6.27         | 14.3          | -109                  | 175.1          | -1.5                |

| [31]   | 65-nm CMOS  | 73.8  | N/A          | 8.4           | -112.2                | -180           | -17                 |

| [32]   | 65-nm CMOS  | 81.5  | 14           | 33            | -97.3*                | -179.7*        | N/A                 |

| [33]   | 90-nm CMOS  | 56.7  | 16           | 8.7           | -118.7                | -184.3         | -3.6                |

| [34]   | 130-nm CMOS | 91    | 0.5          | 46            | -86.2*                | -169.6*        | +4.5                |

| [35]   | 65-nm CMOS  | 70.2  | N/A          | 7.7           | -112                  | -180.4         | N/A                 |

| [36]-1 | 65-nm CMOS  | 75.9  | N/A          | 12            | -109.4                | -176.2         | N/A                 |

| [36]-2 | 65-nm CMOS  | 89.4  | N/A          | 11            | -108.3                | -176.9         | N/A                 |

| [37]   | 65-nm CMOS  | 64    | 7            | 5             | -113.7                | -182.8         | -17                 |

| [38]   | 40-nm CMOS  | 86.2  | 5.8          | 28.4          | -118.8                | -183.2         | N/A                 |

| [39]   | 65-nm CMOS  | 105   | 9.5          | 54            | -92.8*                | -175.5*        | +4.5                |

| [40]   | 65-nm CMOS  | 62.8  | N/A          | 21.5          | -114.95               | -177.6         | -10                 |

| [41]   | 65-nm CMOS  | 59    | 5.4          | 16.5          | -112                  | -175.5         | -0.9                |

| [42]   | 55-nm CMOS  | 77.3  | 3.25         | 15.1          | -115.1                | -181           | -1.12               |

| [53]   | 55-nm CMOS  | 77.1  | 4.79         | 5.69          | -115                  | -185.0         | -4.5                |

<sup>\*</sup>PN and FOM at 1MHz offset; #whenever available, core power is presented; ##Pout generally requires extra DC power (not necessarily shown) due to buffers. Furthermore, if single-ended power is reported, we add 3 dB to the reported value

## 2 MNM TECHNOLOGY PHASE SHIFTERS

This chapter will present all the passive components designed, fabricated and characterized on the Metallic nanowire Membrane (MnM) interposer technology, with the objective to build a mmW phase shifter. A short overview of the MnM technology platform will be presented, then the phase shifter will be presented in detail.

The Metallic nanowire Membrane interposer technology uses a thin membrane made of Anodic Aluminum Oxide (AAO) as substrate for mechanical integration of different devices and for passive RF structures and interconnections. The interposer technology has been in development for almost 10 years at the *Laboratório de Microeletrônica da Universidade de São Paulo* (LME-USP), and its fabrication processes and electrical characterization of the substrate are already mature.

The MnM interposer technology was already used to design innovative and high-performance passive devices in mmW, such as TSV transitions [43], 3D spiral inductors [44], slow-wave transmission lines and waveguides [45] [46] and antennas [47], showing its good performance as RF substrate and versatility as interposer technology. Table 2 shows the state-of-the art for interconnections on interposers at mmW, showing both the losses and sizes of through-substrate vias (TSV) and electrical parameters of transmission lines. The porous alumina used as substrate for the MnM interposer technology features results that rival, or excel, the state-of-the-art.

Table 2 - State-of-the-art of through-substrate vias and transmission lines on interposers for mmW.

|                       | ı                                         | /ia               |                    |        | Transmissio          | n Lines                       |                                |

|-----------------------|-------------------------------------------|-------------------|--------------------|--------|----------------------|-------------------------------|--------------------------------|

| Substrate<br>Material | Transmission loss of two transitions (dB) | Via size          | Via length<br>(μm) | Туре   | α (dB/mm)<br>@60 GHz | $oldsymbol{arepsilon}_{reff}$ | $Z_{\mathcal{C}}$ ( $\Omega$ ) |

| Glass                 | 0.07 @ 20 GHz                             | Ø 40 µm           | 64                 |        |                      |                               |                                |

| Glass                 | 0.68 @ 50 GHz                             | Ø 55 µm           | 366                |        |                      |                               |                                |

| LCP                   | 0.24 @ 40 GHz                             | Ø 105 µm          | 51                 | CPW    | 1.5                  | 1.5                           | 50                             |

| LCP                   | 2 @ 110 GHz                               | Ø 50 µm           | 51                 |        |                      |                               |                                |

| Si (HR)               | 0.06 @ 40 GHz                             | 190 μm x120<br>μm | 100                | CPW    | 0.5                  | 4.5                           | 50                             |

| Si (HR)               | 1.06 @ 75 GHZ                             | Ø 42 μm           | 250                |        |                      |                               |                                |

| Porous<br>Alumina     | 0.46 dB @ 110 GHz                         | 20 μm x 45 μm     | 50                 | CPW µS | < 0.4                | 5.2-3.8                       | 44-140                         |

| Porous<br>Alumina     | 0.2 dB @ 110 GHz                          | 50 μm x 32 μm     | 50                 | SW-µS  | 0.62-1.0             | 90-20                         | 10-43                          |

## 2.1 OVERVIEW OF THE MNM INTERPOSER TECHNOLOGY

AAO is a self-organized material with a honeycomb-like structure of high-density arrays of parallel nanopores. The nanopores are formed by anodization of aluminum in certain conditions that balance the local growth and dissolution of the aluminum oxide. The pore diameter can be controlled with great precision from a few nanometers up to a few hundred nanometers. The membrane is then detached from the aluminum electrode and its thickness is controlled as needed, with values ranging from a few nanometers up to hundreds of micrometers.

Alumina itself is an excellent substrate for microwaves and for mmW. It is characterized at mm-wave frequencies [48] and it displays low substrate losses throughout, thus enabling the fabrication of high-performance passive devices. One of the issues with alumina, however, is its hardness and chemical stability. This makes etching or drilling holes into the substrate, to form TSVs, for example, a very difficult process, which in turn tends to limit the minimum via diameter. The presence of nanopores through the substrate add flexibility to the substrate, because if the nanopores are filled with metal, they can serve as basis for high-performance, high form factor TSVs and for slow-wave microstrip lines. Thus, the need for making holes in the substrate is lifted.

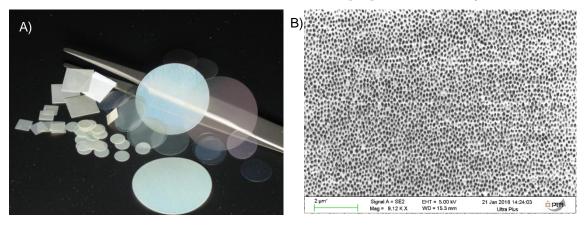

There are various AAO membrane manufacturers, which offer them in a wide range of different porosities, pore diameters and thicknesses. Figure 4 shows some membranes available from Inredox [49], and the nanopores in detail.

Figure 4 – A) AAO membranes in different diameters, thicknesses and pore diameters. B) Electron scan of a membrane showing the nanopores. Source: <a href="https://www.inredox.com/products/nanofab-toolbox/aao-wafers-packs/">https://www.inredox.com/products/nanofab-toolbox/aao-wafers-packs/</a> and author.

The MnM interposer technology uses 50 µm-thick AAO wafers with 40 nm of pore diameter. The wafer diameter is 1 inch, about 2.54 cm. The membranes

are annealed at 600 °C after fabrication by request of our research group to improve its electrical characteristics. The nanoporous membrane was characterized up until 67 GHz in previous works and its electrical characteristics are shown in Table 3.

Table 3 - Electrical characteristics of the AAO membrane used in the MnM interposer technology.

| Parameter            | Value     |  |

|----------------------|-----------|--|

| $\epsilon_r$         | 6.7       |  |

| $tan(\delta)$        | 0.015     |  |

| $\sigma_{Cu}$        | 4.17 MS/m |  |

| $\sigma_{NANOWIRES}$ | 100 kS/m  |  |

Every interposer technology is linked to a fabrication process, such as CMOS for Si-based interposers, or LTCC/HTCC for ceramic substrates. In the case of the MnM interposer technology, the fabrication process as well as the individual steps are developed and carried entirely at the facilities of the Laboratório de Microeletrônica da Universidade de São Paulo (LME-USP). The different steps depend on the exact devices being fabricated. They are: thin film deposition via magnetosputtering; wafer polishing; electroplating; damascene metal thickening; localized substrate corrosion; photolithography; sacrificial layer deposition, etc. For a more detailed description of the in-house fabrication process developed for the MnM devices, the reader is encouraged to read Júlio Pinheiro's doctoral thesis [50].

The MnM interposer technology will be used as basis for all passive devices described in this work.

#### 2.2 MNM PHASE SHIFTER

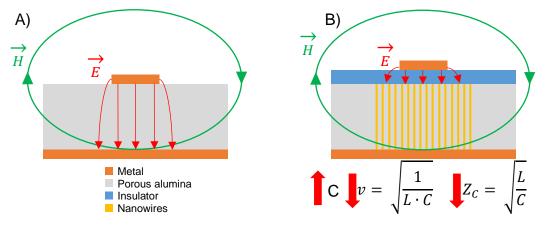

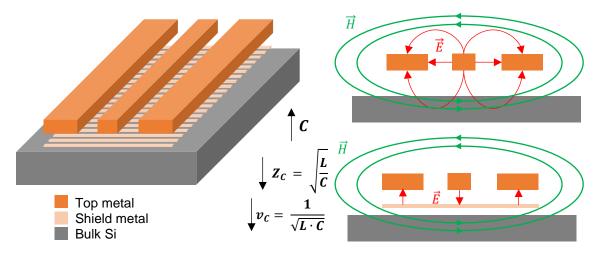

The phase shifter designed on the MnM interposer technology uses several different concepts to realize a compact, well-performing phase shifter working at mmW. The phase shifter itself is based on the MnM slow-wave microstrip lines. In short terms, the electric field is concentrated in the insulant material between the signal strip and the copper nanowires, increasing the unit length capacitance of the line while not disturbing the magnetic field distribution between the strip and the ground plane in a significant matter. Thus, the phase velocity decreases and with it the physical dimensions of the devices. It has the side effect of decreasing the characteristic impedance of the structure, but this leads to further

size reduction. Figure 5 illustrates this concept by comparing the electric and magnetic field distribution between a traditional, non-slow-wave microstrip line, and a slow-wave microstrip line.

Figure 5 - Slow-wave mechanism of the MnM slow-wave microstrip lines. A) shows the cross-section of a traditional microstrip line on the MnM substrate with the electric and magnetic fields sketched over the structure. B) shows the cross section of a slow-wave microstrip line, showing the confinement of the electric field and the consequent reduction in phase velocity and characteristic impedance. Source: author.

Taking this concept as the core for the MnM phase shifter, the phase velocity, thus the electrical length, can be controlled by varying the unit length capacitance of the slow-wave microstrip line. This can be achieved by two means: either by changing the dielectric constant of the insulator material, or changing the distance between the strip and the nanowires. If an air cavity is created between the strip and the nanowires, and such cavity is filled with an electrically-tunable material, both tuning methods can be achieved. The novel suspended microstrip line topology developed in this thesis enables both tuning methods and is, thus, the core of the MnM phase shifter.

Next, the main elements of the MnM phase shifter will be presented and explained in detail, starting by the suspended microstrip lines.

#### 2.2.1 SUSPENDED MICROSTRIP LINES

The suspended microstrip lines are based on the slow-wave microstrip lines presented above, but the strip is elevated from the nanowires on the substrate and the gap between strip and nanowires is filled with air. This way, the device retains some electric field containment at the benefit of decreased propagation losses because of the absence of losses in air, with the side effect of increasing the characteristic impedance of the transmission line when compared to a slow-

wave microstrip line with the same dimensions.

This section presents the structure of the device and its equivalent model, which will be used to design some devices for characterization. Then, the measurement results will be presented and compared to EM simulations.

#### 2.2.1.1 Structure

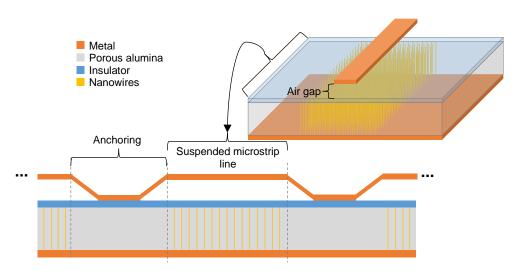

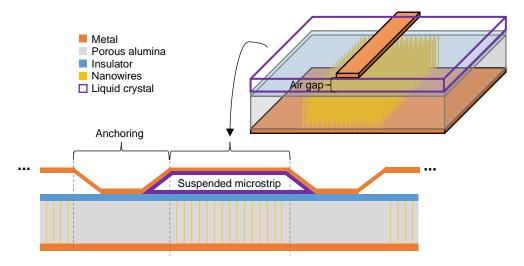

The strip has to be periodically anchored to the substrate, because long suspended sections are more prone to stiction because of static charges or surface tensions of solvents used during the fabrication process. Naturally the anchoring will add some parasitic effects that will interfere with the functioning of the desired, suspended strip, so the electrical length of the anchoring has to be kept as small as the fabrication process allows. The final structure, thus, is a periodic series of long, suspended sections with short anchoring sections between them. Figure 6 shows a simplified 3D view of the suspended microstrip line section and a longitudinal cross-section that shows both the suspended regions as well as the anchoring.

Figure 6 – Simplified structure of the suspended microstrip lines containing a 3D view and a longitudinal cross-section showing the periodoc anchorings necessary to keep the strip from sticking to the substrate during fabrication. Source: author.

#### 2.2.1.2 Model

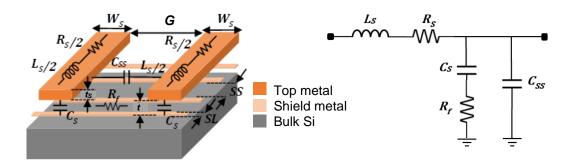

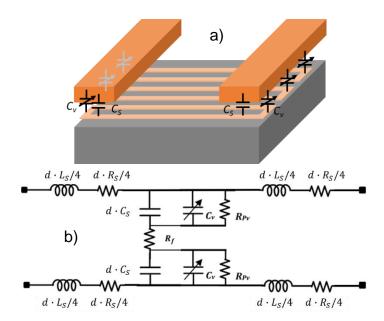

The equivalent electrical model for the suspended microstrip line reflects the periodic nature of the device itself, and so it will be divided into its building blocks: the suspended slow-wave microstrip section, and the anchoring section.

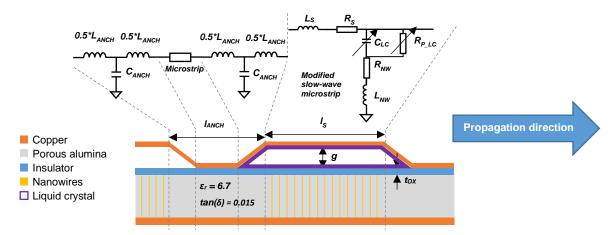

Figure 7 shows the longitudinal cross-section of the suspended microstrip line plus its anchoring and the equivalent electrical model of every section and the relevant lengths of the device. The suspended microstrip is modelled as a slow-wave microstrip line, whose modelling is explained in [51], where insulator capacitance is modified to include the gap height (g) in its calculation  $(C_{GAP})$ , thus the gap is calculated as g plus the oxide thickness  $(t_{OX})$ . Aside from this modification, the nanowire inductance and resistance  $(L_{NW})$  and  $(L_{S})$  and strip inductance  $(L_{S})$  are calculated the same way as in a slow-wave microstrip line, as described in [52]. All variables are per unit length and should be multiplied by the suspended strip length  $(l_{S})$  whenever applicable.

The anchoring section is comprised of a short length of traditional microstrip line plus two transitions: one coming from the previous suspended section and another leading to the following suspended section.

The transitions are modeled as a T-network comprising a series anchoring inductance and shunt capacitance ( $L_{ANCH}$  and  $C_{ANCH}$ ). The microstrip line on the substrate is modelled by the standard microstrip line model. The anchoring length ( $l_{ANCH}$ ) comprises both transition and the anchoring microstrip.

The model for the whole transmission line is simply a series concatenation of anchoring and suspended microstrip line sections. This way the anchoring parasitics are incorporated into the desired, suspended microstrip line response, as the anchoring is an integral part of this device.

Figure 7 – Longitudinal cross-section of the suspended microstrip line showing its most important physical dimensions and the equivalent electrical model of each section (anchoring and suspended microstrip line). Source: author.

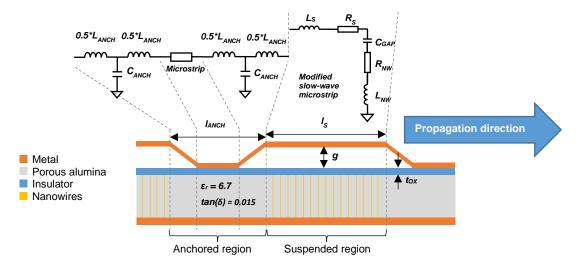

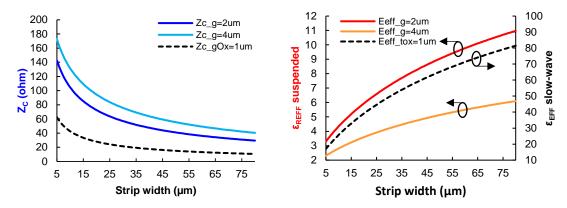

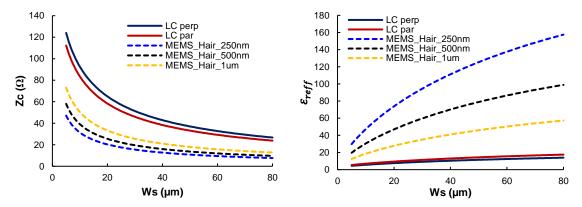

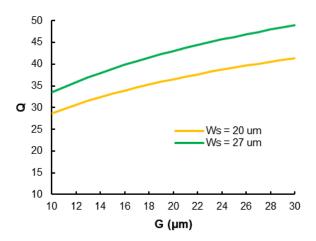

The design for a suspended microstrip line starts by defining the desired suspended line characteristics and then accounting for the anchoring parasitics. The suspended microstrip line characteristic impedance  $(Z_C)$  and effective dielectric constant  $(\varepsilon_{reff})$  are a function of g and of the strip width  $(W_S)$ . Figure 8 presents the  $Z_C$  and the  $\varepsilon_{reff}$  for the suspended microstrip line versus strip width for  $g=2~\mu m$  and  $g=4~\mu m$ , and also the  $Z_C$  and  $\varepsilon_{reff}$  for a slow-wave microstrip line with  $t_{OX}=1~\mu m$  for reference, with Si dioxide for insulator.

Figure 8 – Characteristic impedance and effective deielctric constant of the suspended microstrip line and slow-wave microstrip line in function of the strip width. Two gap heights are considered for the suspended lines: 2  $\mu$ m and 4  $\mu$ m. For the slow-wave microstrip lines, the insulator thickness is 1  $\mu$ m. Source: author.

The  $Z_C$  increases with g and diminishes with  $W_S$  and can be as high as 175  $\Omega$  for  $W_S=5$   $\mu m$  and g=4  $\mu m$  and as low as 30  $\Omega$  for  $W_S=80$   $\mu m$  and g=2  $\mu m$ .  $\varepsilon_{reff}$  follows the inverse of this rule, diminishing with g and increasing with  $W_S$ , being as low as 2.3 for  $W_S=5$   $\mu m$  and g=4  $\mu m$  and as high as 10.9 for  $W_S=80$   $\mu m$  and g=2  $\mu m$ . On another hand, the slow-wave microstrip lines show  $W_S=80$   $W_S=80$  W

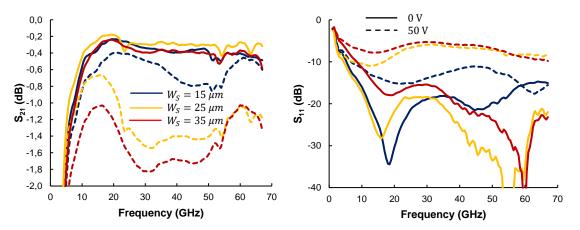

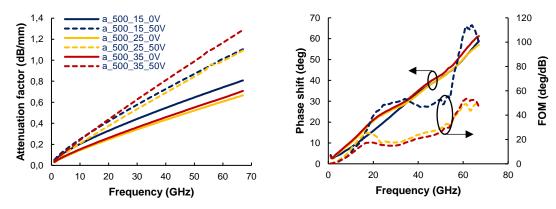

To validate the accuracy of the model and the performance of the suspended microstrip lines, three different structures were designed and fabricated with  $W_S = 15 \mu m$ , 25  $\mu m$  and 35  $\mu m$ , respectively. The g was fixed at 4  $\mu m$  because of fabrication constraints at the time these devices were fabricated.

#### 2.2.1.3 Fabrication and measurements

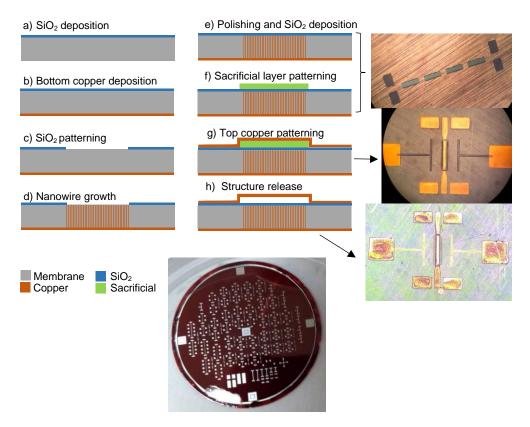

The fabrication process for the suspended microstrip lines and RF pads happened as follows, and is illustrated in Figure 9. Starting with a bare AAO membrane, SiO<sub>2</sub> with 200 nm is deposited on the top side, by magnetron sputtering (Figure 9a). On the bottom side, a thin copper layer of approximately 30 nm is also deposited by sputtering (Figure 9b). The top SiO<sub>2</sub> is then patterned (Figure 9c) and used as mask for the selective copper nanowire growth (Figure 9d). Nanowires are grown by electrodeposition using MacDermid Enthone's MacuSpec PPR 100 acid copper plating process. After 1.5 hours of copper deposition using Periodic Pulse Reverse (PPR), a solid copper film is formed on the top side of the membrane. To expose the nanowires and remove this solid film, the top side is polished.

Another 300nm-thick SiO $_2$  film is deposited on the top side to serve as mask for the nanowire TSVs and to seal the still open nanopores (Figure 9e). The photoresist AZ9260 was deposited and patterned to be used as sacrificial material (Figure 9f) to form an air gap of ~4  $\mu$ m. Figure 9g illustrates the deposition and definition of the top copper layer. For that, another thin copper layer was deposited by sputtering to be used as seed layer for the electrodeposition of copper using the same solution used for the nanowires. Photoresist was used to mask regions where the copper was not to be electrodeposited. On the exposed areas: microstrip with the suspended regions; anchors; and RF pads, the copper is thickened to 3  $\mu$ m. Later, the copper seed is removed. The final step, illustrated in Figure 9h, is the release of the suspended line. The sample is submerged in acetone at 40°C for 1 hour, then for 5 minutes in isopropanol at 40°C.

Figure 9 – Fabrication process used to fabricate the suspended microstrip lines on the MnM substrate and a photo of the completed membrane wafer. Source: author.

It is known from experience that the AZ9260 patterning process causes thickness variations across the length of the patterned region, being thicker close to the edges and thinner at the center. To verify the impact this variation has on the performance, lines with two different values of  $L_S$  were fabricated: 250 µm and 500 µm. In total, six different devices were fabricated. Their dimensions, number of suspended segments ( $N_S$ ), as well as their ideal  $Z_C$ , are shown in Table 4. In all structures, the  $l_{ANCH}$  is 100 µm: 50 µm for the anchoring and 25 µm for each transition.

Table 4 - Ws, Ls, number of segments, total length and characteristic impedance of the fabricated suspended microstrip lines.

| $W_S$ ( $\mu$ m) | $Z_{\mathcal{C}}$ ( $\Omega$ )<br>( $g$ = 4<br>$\mu$ m) | $L_S$ ( $\mu$ m) | Ns | Total<br>length<br>(µm) |

|------------------|---------------------------------------------------------|------------------|----|-------------------------|

| 15               | 109                                                     | 250              | 4  | 1450                    |

| 13               | 109                                                     | 500              | 2  | 1250                    |

| 25               | 0.4                                                     | 250              | 4  | 1450                    |

| 25               | 84                                                      | 500              | 2  | 1250                    |

| 35               | 62                                                      | 250              | 4  | 1450                    |

|                  | 63                                                      | 500              | 2  | 1250                    |

The suspended microstrip lines were characterized up to 67 GHz using

ground-signal-ground (GSG) probes (MPI Titan probes with 100 µm-pitch) in a manual probe station and a Keysight PNA N5227B vector network analyzer. A LRRM calibration was done. Unfortunately, due to process variations, no TRL calibration was possible. The raw S-parameter data of the DUTs plus accesses was de-embedded in ADS to enable the extraction of the DUT characteristics. The GSG pads were simulated in ADS momentum and then its S-parameter matrix was used for de-embedding. However, the de-embedded data contains imprecisions at frequencies below 20 GHz, due to the variation of the shunt capacitance between the GSG ground and the nanowires underneath.

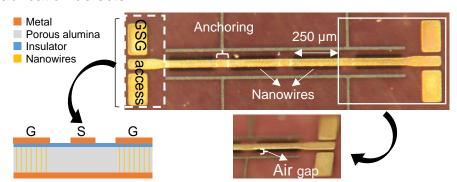

Figure 10 shows a picture of the fabrication result of a suspended line with four suspended segments, whose  $L_S = 250 \,\mu\text{m}$  and  $W_S = 25 \,\mu\text{m}$ . The air gap, nanowire-filled regions and the profile of the GSG pads are shown in detail. No stiction was observed in any of the devices and a visual inspection revealed no obvious fabrication defects.

Figure 10 – Photo of a fabricated suspended microstrip line with  $W_S$  = 25 µm, 4 segments and  $L_S$  = 250 µm showing the RF pads, the regions filled with nanowires and the air gap between the substrate and the signal strip. Source: author.

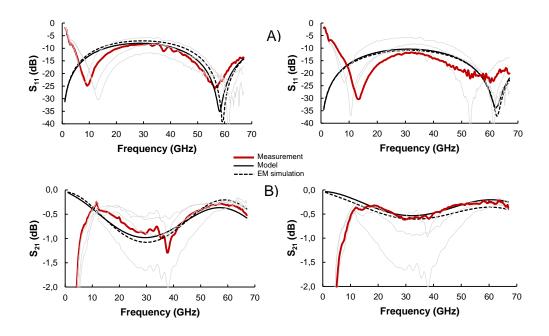

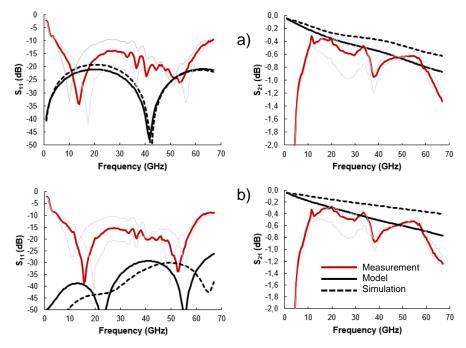

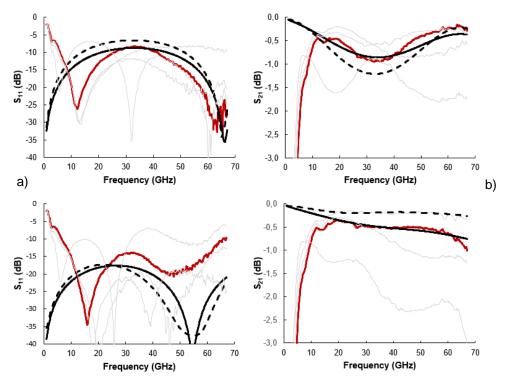

Figure 11 shows the measured return loss and insertion loss of all fabricated devices. Also, it shows the comparison between two different devices and their respective EM simulation results, and the fitting from the model presented in Figure 7 and Figure 8.

Figure 11 - Measured S-parameters of all fabricated suspended microstrip lines (light grey). In detail (red), the measurement is compared against the EM simulation (dashed black) and the proposed model (black). A) Comparison of return for 4 segments,  $W_S=25~\mu m$  and  $L_S=250~\mu m$  (left column) and for 2 segments,  $W_S=35~\mu m$  and  $L_S=500~\mu m$  (right column). B) Comparison of the insertion loss for the same devices. Source: author.

The model response was obtained by conducting a manual parametric fit using the measurement curves as template. It can be seen that the correlation between simulation, model and measurement is very good above 20 GHz, thus confirming the validity of the proposed model.

Table 5 contains the  $\varepsilon_{reff}$ ,  $Z_{C}$  and attenuation constant ( $\alpha$ ) fitted for the slow-wave microstrip line of the two devices shown in detail in Figure 11 for both measurement and EM simulation. The values outside parenthesis are for the suspended segments only, and they are compared against the values given by the slow-wave microstrip line model shown in Figure 8. The values inside parenthesis, where applicable, refer to the suspended segments plus anchoring parasitics.

Table 5 – Characteristic impedance, effective dielectric constant and attenuation constant of the suspended microstrip line segments extracted from measurement and compared against EM simulations. Values in parenthesis are for suspended lines plus anchoring parasitics

| •                                                   | •                      | •                         | 0.1              |  |

|-----------------------------------------------------|------------------------|---------------------------|------------------|--|

|                                                     | 4 segments, $L_S = 25$ | $0 \mu m, W_S = 25 \mu m$ | 1                |  |

|                                                     | Measurement            | Simulation                | Model (Figure 8) |  |

| <b>Ζ</b> <sub>C</sub> (Ω) 82 (75)                   |                        | 88 (81)                   | 84               |  |

| $\varepsilon_{reff}$ 4.0 (4.8)                      |                        | 3.8 (4.6)                 | 3.9              |  |

| lpha (dB/mm<br>@60GHz)                              | 0.252                  | 0.163                     |                  |  |

| 2 segments, $L_S$ = 500 $\mu$ m, $W_S$ = 35 $\mu$ m |                        |                           |                  |  |

|                                                     | Measurement            | Simulation                | Model (Figure 8) |  |

| $Z_{\mathcal{C}}\left(\Omega\right)$                | 69 (66)                | 70 (68.6)                 | 69.1             |  |

| $arepsilon_{reff}$                                  | 4.6 (5)                | 4.7 (4.95)                | 4.7              |  |

| lpha (@60GHz)                                       | 0.292                  | 0.168                     |                  |  |

|                                                     | Anchoring p            | parasitics                |                  |  |

|                                                     | L <sub>ANCH</sub>      | $C_{ANCH}$                |                  |  |

| $W_S$ = 15 $\mu m$                                  | 3.58 pH                | 1.78 fF                   |                  |  |

| $W_S = 25 \; \mu \text{m}$                          | 2.53 pH                | 2.82 fF                   |                  |  |

| $W_S = 35  \mu m$                                   | 2.41 pH                | 2.68 fF                   |                  |  |

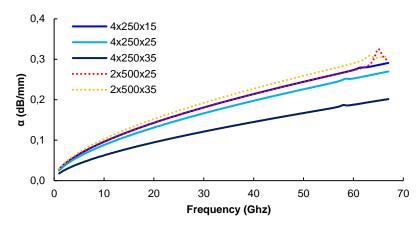

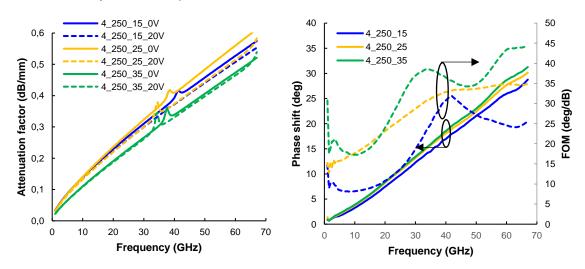

The anchoring indeed affects the propagation characteristics of the suspended microstrip line by increasing the equivalent shunt capacitance to ground, which reflects in increasing  $\varepsilon_{reff}$  and reducing  $Z_{C}$ . It can also be noted that the fabricated lines present more insertion loss than predicted by simulations. Figure 12 shows the attenuation constant  $\alpha$  for all measured devices. The average  $\alpha$  for these transmission lines at 60 GHz is 0.27 dB/mm.

Figure 12 – Attenuation constant for the measured suspended microstrip lines. Source – author.

Next the transmission lines were compared against traditional microstrip lines, fabricated on the MnM substrate with no copper nanowires underneath

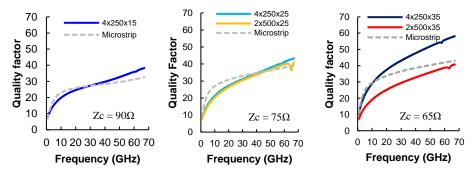

them. Figure 13 shows the Q-factor for the measured suspended microstrip lines compared against traditional microstrip lines of the same  $Z_c$ . It can be seen that the suspended microstrip lines perform as well as standard microstrip lines, outperforming them at frequencies above 30 GHz.

Because of the slow-wave effect, the suspended microstrip lines are very sensitive to the electrical characteristics of the gap material. Air, having no dielectric loss, make so that the main loss mechanism for the suspended microstrip lines is conductor loss from the signal strip and from the nanowires.

Figure 13 – Comparison of the quality factor between the measured suspended microstrip lines and traditional microstrip lines designed on the MnM substrate. Source – author.

## 2.2.1.4 Partial conclusions

The suspended microstrip lines were presented, as well as their equivalent electrical model. The suspended microstrip lines were fabricated, measured and these data were compared against EM simulations and against the parametric fit using the proposed electrical model. The correlation is very good, thus confirming the accuracy of the model. The suspended microstrip lines themselves have good RF performance and are a suitable element for high- $Z_C$  interconnections.

#### 2.2.2 LIQUID CRYSTAL MNM PHASE-SHIFTER

Having presented and discussed the suspended microstrip lines, now the MnM phase shifter is presented in this section. Figure 14 shows the basic structure of the MnM-LC phase shifter. It comprises a suspended microstrip line whose air cavity is filled by a LC solution.

Figure 14 - Basic structure of the MnM liquid crystal phase shifter, showing a 3D-view of the suspended region and a cross-section of the anchoring plus suspended regions. Source: author.

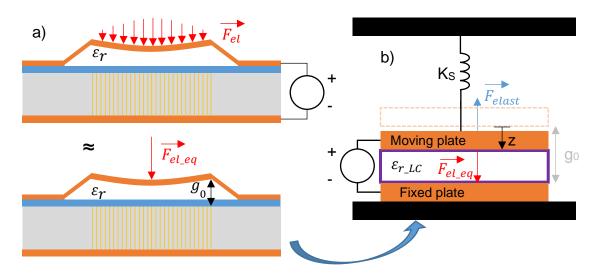

The MnM phase shifter achieves phase velocity variation by changing  $\mathcal{C}_{GAP}$  in two different ways. The first is by changing the gap distance, by applying a biasing potential higher than the pull-in voltage for the suspended line, so the line switches like a MEMS switch. The second is by modifying the  $\varepsilon_r$  of the gap material by adding an electrically-tunable material between the signal strip and the nanowires.

Liquid crystal (LC) solutions are the material of choice to be added to the gap because of two main reasons: the first being that LC loss tangent decreases with frequency; the second being that the LC reduces the pull-in voltage for the MEMS switching by an amount equal to  $\varepsilon_r$  and, being a liquid, won't impede the electrostatic switching from happening.

## 2.2.2.1 Overview of liquid crystals

LCs are a state of matter whose physical properties are between those of a liquid and of a solid: even though it may flow like a liquid, its molecules show some degree of large-scale ordering like a crystal. There are many different phases, or states, in LC substances, the most important for the needs of this work is the nematic phase. In the nematic phase, even though the LC molecules' distribution may be randomized, they display large-scale self-orientation because of their shape. When these molecules have a dominant dimension, they can be approximated as being rod-like. A LC substance whose molecules are rod-shaped is called a calamitic LC. Thus, a nematic calamitic LC has its rod-shaped

molecules self-oriented in a thread-like, large-scale structure. Even though they have capacity of self-alignment, LC molecules in a nematic calamitic LC can be re-oriented by external coercive forces in the form of electric or magnetic fields. In this work only the purely electric biasing will be used.

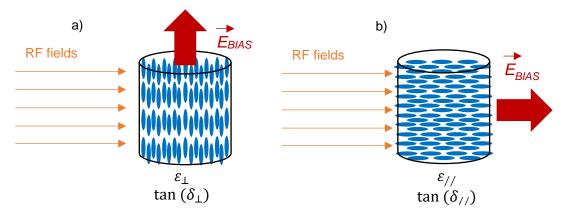

Nematic calamitic LCs show anisotropic electric and optical characteristics depending on the angle to the axis of orientation of the molecules, and this characteristic is what gives it their electric tunability. The two extreme states are when the rod-shaped molecules are oriented parallel to the RF fields and when they are orthogonal to the RF fields. The transition between these two states is continuous and is a function of the angle between the molecules and the external RF fields. Figure 15 exemplifies this phenomenon. The LC molecules, shown as elongated blue ellipsoids, are aligned to an external electric field ( $E_{bias}$ ) and, being subjected to external RF fields, display different electric properties: Figure 15 A) the fields are orthogonal to the molecules, and the LC is characterized by  $\varepsilon_{\perp}$  and  $tan(\delta)_{\perp}$ . In Figure 15 B) the fields are parallel to the molecules, and the LC is characterized by  $\varepsilon_{//}$  and  $tan(\delta)_{//}$ . If the angle between the LC molecules and the RF fields is between 0° and 90°, the equivalent electrical characteristics of the LC will be an intermediate value between these two extremes and proportional to the dot product between the RF fields and the dominant axis of orientation of the LC molecules.

Figure 15 – Illustration of liquid crystal electric anisotropy towards external RF fields. The liquid crystal molecules are presented as light-blue ellipsoids. Source: author.

Table 6 shows the electrical characteristics of two different LC solutions at 19 GHz. BL111 is an older type of LC solution developed for LC display applications, however more recently new LC solutions were developed aimed specifically for microwave and mm-wave applications. These newer solutions,

such as GT3-23001 from Merck KGaA, Darmstadt, Germany, have lower losses and wider electric tunability,  $T_{\epsilon}$ .

Table 6 – Electric characteristic of BL111 and GT3-23001 liquid crystal solutions at 19 GHz. Source: [53]

| LC solution | $oldsymbol{arepsilon}_{//}$ | $tan(\delta_{//})$ | $oldsymbol{arepsilon}_{\perp}$ | $tan(\delta_{\perp})$ | $T_{\varepsilon}$ (%) |

|-------------|-----------------------------|--------------------|--------------------------------|-----------------------|-----------------------|

| BL111       | 3.25                        | 0.0084             | 2.64                           | 0.0218                | 18.77                 |

| GT3-23001   | 3.19                        | 0.0035             | 2.41                           | 0.0143                | 25.2                  |

#### 2.2.2.2 Phase shift mechanisms

The core structure for this LC phase shifter is the suspended microstrip line, where the LC is injected in the gap between the signal strip and the nanowires. The presence of the LC acts as the insulator material in the slow-wave microstrips presented in Figure 5.

Under no bias the LC molecules will rest parallel to the substrate, guided by the substrate surface. If, then, a positive voltage is applied between the signal strip and the grounded nanowires, the LC molecules will start to reorient themselves parallel to the biasing electric field. The electric field creates torque on the LC molecules, which is proportional to the field intensity. If the voltage is above a certain threshold, called the *Freedericksz threshold* ( $V_{FTH}$ ) [54], the torque from the electric force will overcome the restoring torque and the LC molecules will start to reorient themselves parallel to the electric field. The angle between the LC molecules and the electric field will follow a continuous relation until the biasing voltage is high enough so the LC molecules are completely parallel to the electric fields. This translates to a change in the suspended microstrip  $\varepsilon_{reff}$  and, thus, in phase velocity. The change in phase velocity creates the phase shift.

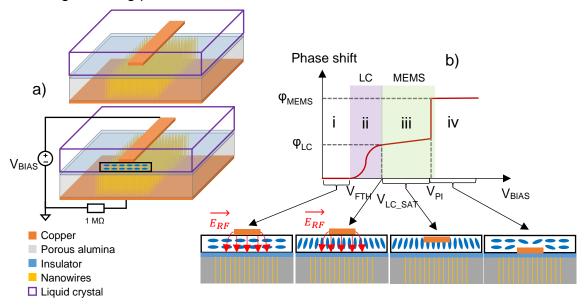

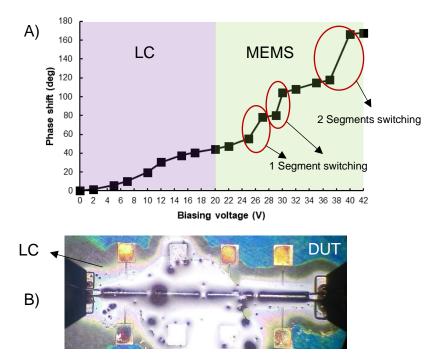

Now, if the voltage is above another, higher threshold, which is the pull-in voltage for the suspended strip, the strip will switch, collapsing towards the nanowires like a MEMS switch. This will dramatically reduce the distance between the strip and the nanowires, strongly increasing  $C_{GAP}$  and, thus, decreasing the phase velocity. The LC will lower the pull-in voltage of the strip because of its relative dielectric constant. This mechanism creates strong phase shift in a binary way.

Figure 16 a) shows the 3D view of the suspended microstrip lines with LC injected around it, as well as a simplistic representation of the biasing

mechanism: a biasing voltage  $V_{bias}$  is applied between the suspended strip and the grounded nanowires below, superimposing the biasing electric field to the RF field of the suspended microstrip. The 1 M $\Omega$  resistor acts as current limiter in the event of dielectric breakdown to protect the devices and the RF probes.

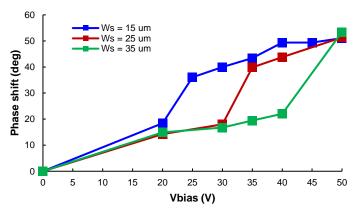

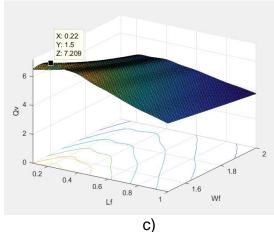

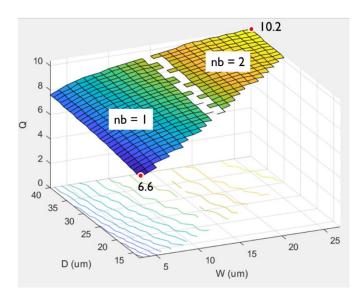

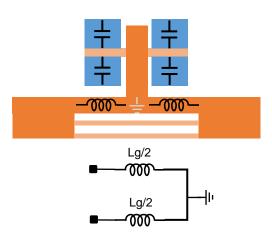

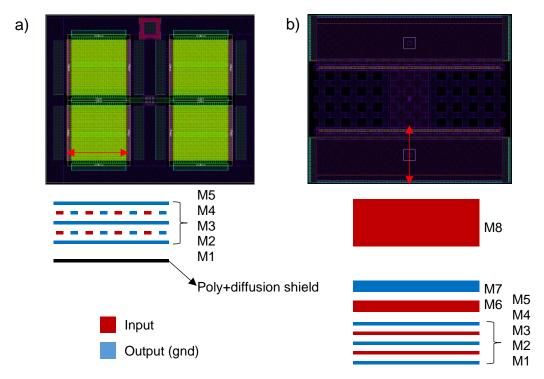

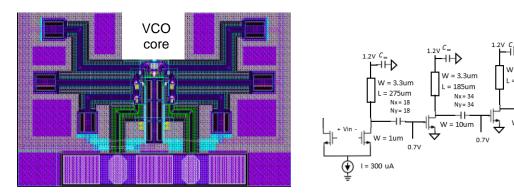

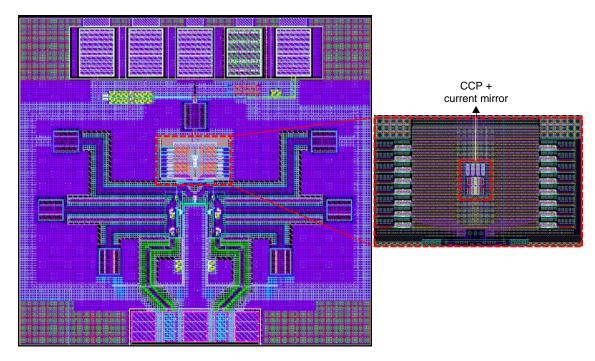

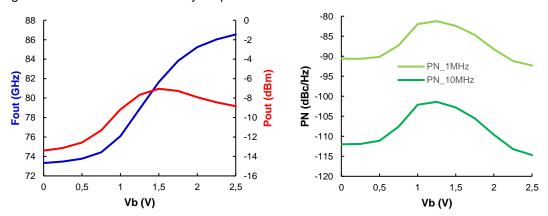

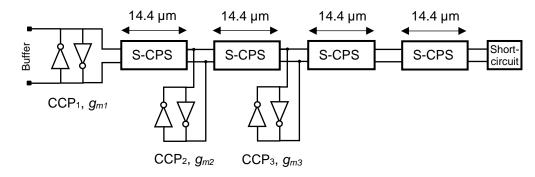

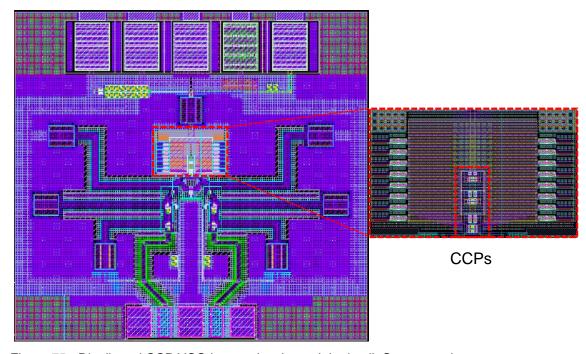

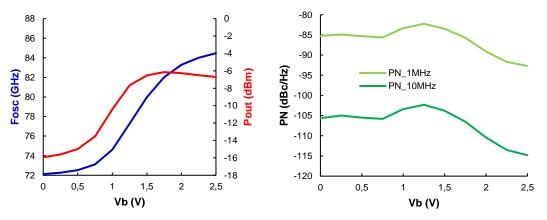

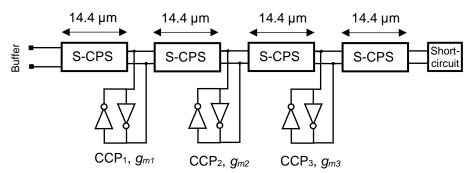

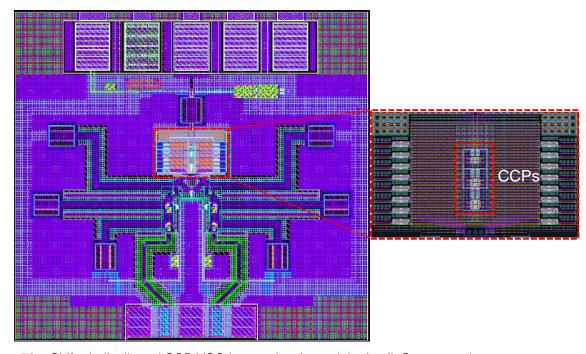

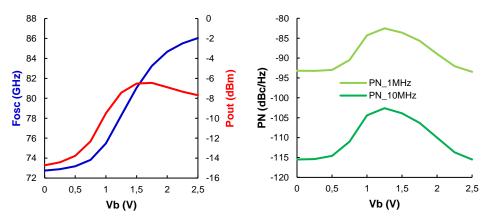

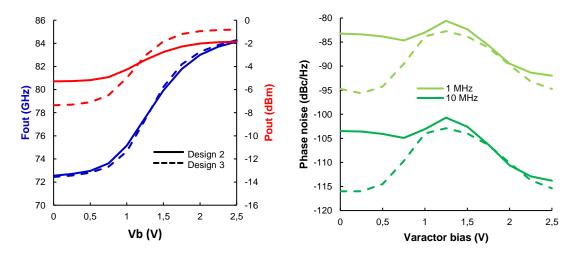

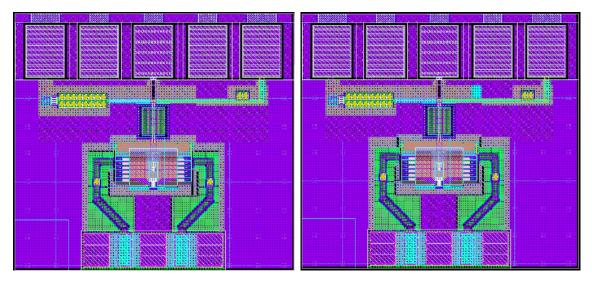

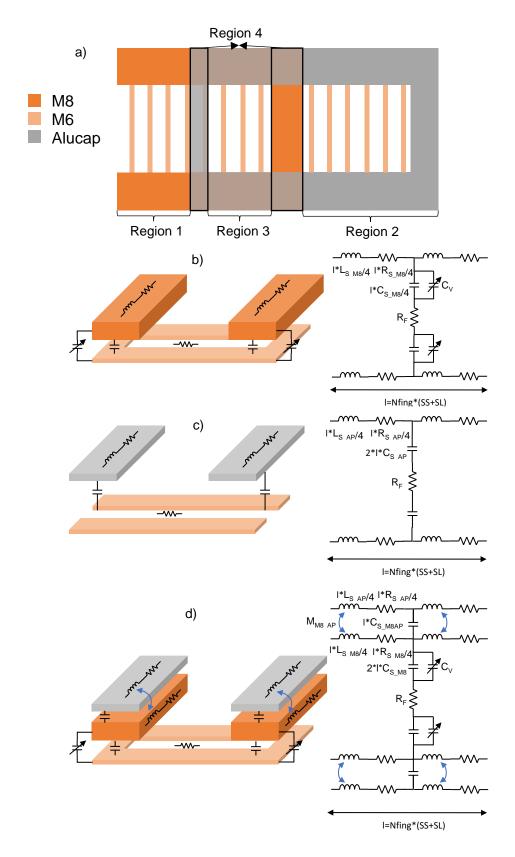

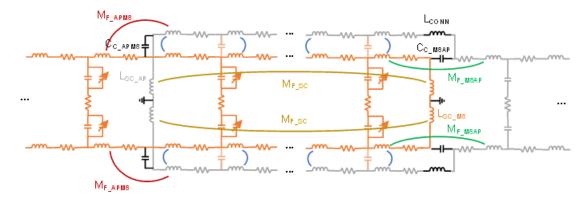

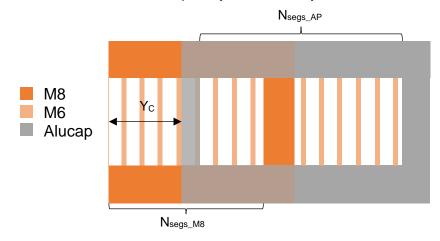

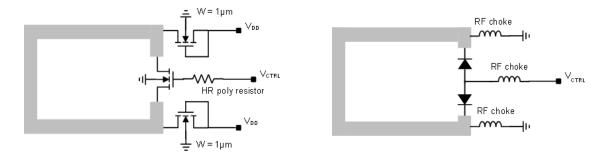

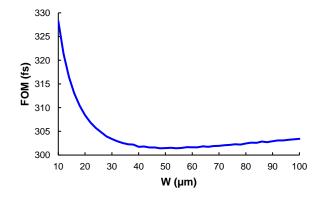

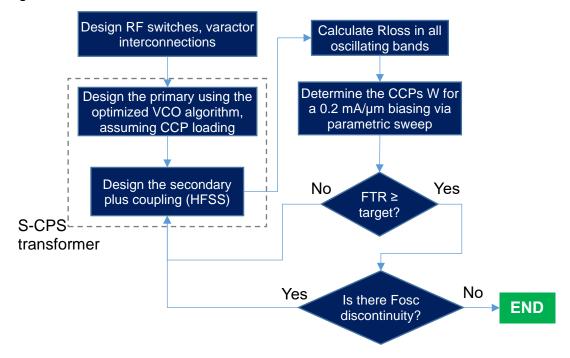

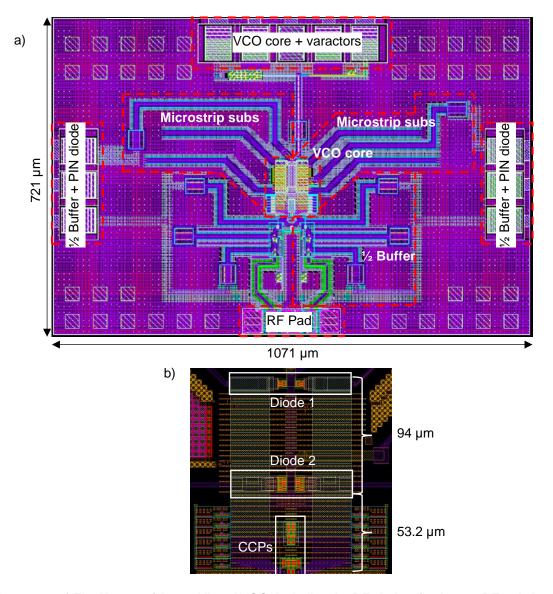

Figure 16 b) shows a representation of the phase shift in function of  $V_{bias}$ : (i) for  $V_{bias}$  smaller than the  $V_{FTH}$ , the phase shift is zero because the molecules are not disturbed, the resultant force being the restorative elastic forces; (ii) for  $V_{bias}$  higher than  $V_{FTH}$ , the LC molecules start aligning themselves to the biasing field and  $V_{bias}$  has direct control over the phase shift; (iii) when  $V_{bias}$  reaches a saturation voltage ( $V_{LC\_sat}$ ), the LC molecules are fully parallel to the RF fields and the LC does not contribute to the phase shift, however, the electrostatic forces on the suspended strip may cause it to sag, reducing the gap distance a little and causing some phase shift; (iv) however, when  $V_{bias}$  reaches the pull-in voltage ( $V_{PI}$ ), the suspended line switches and the gap distance is drastically reduced, resulting in strong phase shift.