## ARTHUR LOMBARDI CAMPOS

### Design of a low-power 10-bit 12-MS/s asynchronous SAR ADC

**Revised Version**

Dissertation presented to the University of São Paulo at São Carlos School of Engineering in partial fulfillment of the requirements for obtaining the degree of Master of Science in Electrical Engineering.

Area of concentration: Signal processing and instrumentation.

Advisor: Prof. Maximiliam Luppe, PhD.

São Carlos

2020

I AUTHORIZE THE TOTAL OR PARTIAL REPRODUCTION OF THIS WORK, THROUGH ANY CONVENTIONAL OR ELECTRONIC MEANS, FOR STUDY AND RESEARCH PURPOSES, SINCE THE SOURCE IS CITED.

#### Catalog card prepared by Patron Service at "Prof. Dr. Sergio Rodrigues Fontes" Library at EESC/USP

| C198d | Campos, Arthur Lombardi<br>Design of a low-power 10-bit 12-MS/s asynchronous SAR<br>ADC / Arthur Lombardi Campos; Thesis directed by<br>Maximiliam Luppe São Carlos, 2020.                           |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Master (Thesis) Graduate Program in Electrical<br>Engineering and Research Area in Signal Processing and<br>Instrumentation - São Carlos School of Engineering,<br>at University of São Paulo, 2020. |

|       | 1. Integrated circuits. 2. Analog-to-digital<br>converter. 3. Low power consumption. 4. Receives<br>asynchronous. 5. SAR ADC. 6. Internet of things. I. Title.                                       |

## ARTHUR LOMBARDI CAMPOS

# Projeto de um SAR ADC assíncrono de 10 bits a 12MS/s para baixo consumo

Versão Corrigida

Dissertação apresentada à Escola de Engenharia de São Carlos da Universidade de São Paulo como pré-requisito para a obtenção do título de Mestre em Ciências, programa de Engenharia Elétrica.

Área de concentração: Processamento de sinais e instrumentação.

Orientador: Prof. Dr. Maximiliam Luppe.

São Carlos

2020

#### AUTORIZO A REPRODUÇÃO TOTAL OU PARCIAL DESTE TRABALHO, POR QUALQUER MEIO CONVENCIONAL OU ELETRÔNICO, PARA FINS DE ESTUDO E PESQUISA, DESDE QUE CITADA A FONTE.

Ficha catalográfica elaborada pela Biblioteca Prof. Dr. Sérgio Rodrigues Fontes da EESC/USP com os dados inseridos pelo(a) autor(a).

Campos, Arthur Lombardi

Design of a low-power 10-bit 12-MS/s asynchronous

SAR ADC / Arthur Lombardi Campos; orientador Maximiliam

Luppe. São Carlos, 2020.

Dissertação (Mestrado) - Programa de

Pós-Graduação em Engenharia Elétrica e Área de

Concentração em Processamento de Sinais e

Instrumentação -- Escola de Engenharia de São Carlos da

Universidade de São Paulo, 2020.

Circuitos Integrados. 2. Conversor

Analógico-Digital. 3. Baixo consumo de energia. 4. SAR

ADC assíncrono. 5. Receptores. 6. Internet das coisas.

I. Título.

Eduardo Graziosi Silva - CRB - 8/8907

#### FOLHA DE JULGAMENTO

#### Candidato: Engenheiro ARTHUR LOMBARDI CAMPOS.

Título da dissertação: "Projeto de um SAR ADC assíncrono de 10 bits a 12MS/s para baixo consumo".

Data da defesa: 15/09/2020

#### Comissão Julgadora:

Prof. Dr. Maximiliam Luppe (Orientador) (Escola de Engenharia de São Carlos – EESC/USP)

Dr. Eduardo Rodrigues de Lima (Instituto de Pesquisa Eldorado)

Prof. Dr. Hugo Daniel Hernandez Herrera (Universidade Federal de Minas Gerais/UFMG) <u>Resultado</u>

Approvado

<u>Aprovedo</u> <u>Aprovedo</u>

Coordenador do Programa de Pós-Graduação em Engenharia Elétrica: Prof. Titular Ivan Nunes da Silva

Presidente da Comissão de Pós-Graduação: Prof. Titular Murilo Araujo Romero

$To\ my\ parents\ and\ brothers,\ with\ love\ and\ gratitude.$

## Acknowledgements

I would like to express my gratitude to the people and organizations that have directly or indirectly contributed to this work. First, I would like to thank Professor João Navarro Soares Júnior for the rich contributions and discussions throughout the development of this work, besides the in-depth revision of this document, and Professor Maximiliam Luppe for the opportunity of participating in this research project.

I would like to thank the colleagues at the Eldorado Institute of Research, specially Eduardo de Lima, for the opportunity to fabricate the chip, and Julián Herrera, for the layout and fabrication of the test boards.

I am grateful to the collaborators that I have worked with and friends that I have made during my time at the CMOS-SOI and DMPSV groups of the LSI-USP, in special to Professor João Martino, for his guidance at the beginning of my masters, and to Professor Wilhelmus van Noije, for previous collaborations in other projects and for kindly providing the infrastructure for the development of this work.

I would like to thank all my friends at the LSI-TEC Design House for always sharing knowledge and for the great moments of joy. A special thanks to my superiors Heiner Alarcón, Jake Choi and Professor Julio Saldaña for the mentoring during my first steps as IC designer and firmware designer.

I would like to thank all my friends at the University Center of FEI, specially Professor Salvador Gimenez for his guidance on my first research project and for introducing me to the field of microelectronics.

I am grateful to MEC for the opportunity to study in the University Center of FEI with the Prouni grant. This program was essential for me to build a solid technical basis, having a direct impact on my life.

I am also grateful to MCTIC for the opportunity to study abroad in the University of Porto, through the CsF program, where I had access to excellent infrastructure and microelectronics classes. Moreover, I met friends for life, which I would like to thank for the amazing life experiences.

I would like to thank very much my longtime friends for the memorable times and for always being at my side, even during the turbulent moments. They have a big influence on my life.

Finally, I am grateful to all the members of my family, in special to my parents, Iranilton and Odete, and to my brothers, Edgard and Ulisses, whose love, education, companionship and patience are my big foundations.

# Abstract

CAMPOS, A. L. Design of a low-power 10-bit 12-MS/s asynchronous SAR ADC. 2020. 134p. Dissertation (masters) – São Carlos School of Engineering, University of São Paulo, São Carlos, 2020

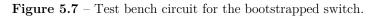

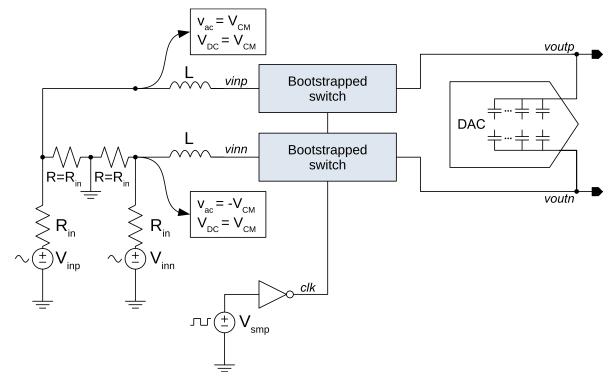

This work presents the design of a low-power 10-bit 12-MS/s Successive Approximation Register (SAR) Analog-to-Digital Converter (ADC) in 65-nm technology, suitable for IEEE 802.15.4g standard frontend receivers (low data rate and power consumption smart utility networks). By using the differential implementation with a pair of bootstrapped switches, the input signal is sampled with low distortion. The asynchronous implementation of the SAR circuit leads to an increased system flexibility because only a single clock source is required. To support the merged capacitor switching scheme (MCS), a three-level switch circuit was designed for the capacitor array. The simulated circuit achieved a 9.65 ENOB with 151.4  $\mu$ W of power consumption at 12 MS/s, leading to a FOM of 15.8 fJ/Conversion-step. Simulations have also shown that the ADC is efficient for sampling frequencies ranging from 10 kS/s up to 12 MS/s, extending its usability to low sampling frequency circuits.

Keywords: Integrated Circuits. Analog-to-Digital Converter. Low power consumption. Receivers. Asynchronous SAR ADC, Internet of Things.

## Resumo

**CAMPOS, A. L.** Projeto de um SAR ADC assíncrono de 10 bits a 12MS/s para baixo consumo. 2020. 134p. Dissertação (mestrado) – Escola de Engenharia de São Carlos, Universidade de São Paulo, São Carlos, 2020

Este trabalho apresenta o projeto de um Conversor Analógico-Digital (ADC) de 10 bits a 12 MS/s, de baixo consumo, do tipo Registrador de Aproximações Sucessivas (SAR) assíncrono. O circuito foi projetado em tecnologia de 65 nm e visa atender receptores desenvolvidos para o padrão IEEE 802.15.4g (redes inteligentes de baixo consumo e baixa taxa de transmissão de dados). Para reduzir a distorção durante amostragem de sinais, foi utilizado uma implementação diferencial com um par de chaves *bootstrap*. A implementação assíncrona do circuito SAR aumenta a flexibilidade do sistema porque apenas um sinal de relógio é necessário para seu funcionamento. Para suportar o esquema de chaveamento mesclado (MCS), uma chave de três níveis foi desenvolvida para a matriz de capacitores. Em simulações, o circuito atingiu um ENOB de 9.65 e um consumo de 151.4  $\mu$ W, a 12 MS/s, resultando em uma figura de mérito de 15.8 fJ/Conversion-step. Simulações também indicaram que o ADC é eficiente em frequências de amostragem variando de 10 kS/s a 12 MS/s, estendendo sua usabilidade para circuitos de baixa taxa de amostragem.

Palavras-chave: Circuitos Integrados. Conversor Analógico-Digital. Baixo consumo de energia. Receptores. SAR ADC assíncrono, Internet das coisas.

# List of figures

| Figure 1.1 – Block diagram of typical RF communication receiver                        |

|----------------------------------------------------------------------------------------|

| Figure 2.1 – ADC transfer curve considering no offset (a) and $-1/2$ LSB offset (b)35  |

| Figure 2.2 – A typical SAR ADC implementation                                          |

| Figure 2.3 – Flowchart of a typical binary search used in SAR ADCs                     |

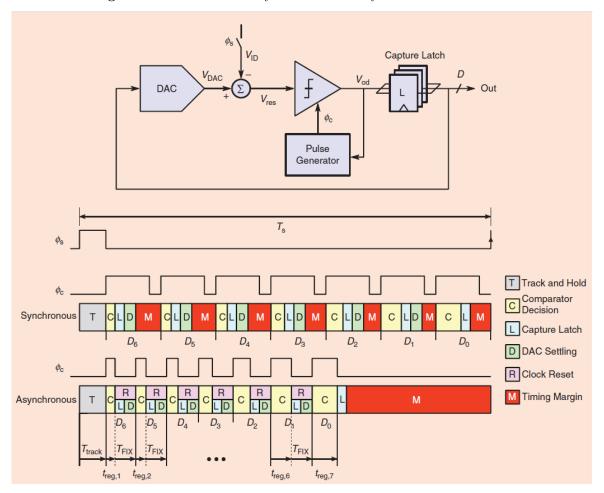

| Figure 2.4 – Time chart of synchronous and asynchronous SAR ADCs                       |

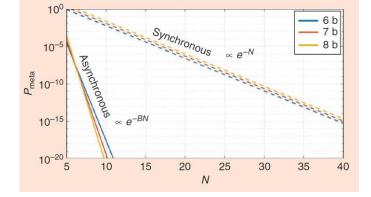

| Figure 2.5 – A graph of the probability of a metastable event, for different ADC       |

| resolutions                                                                            |

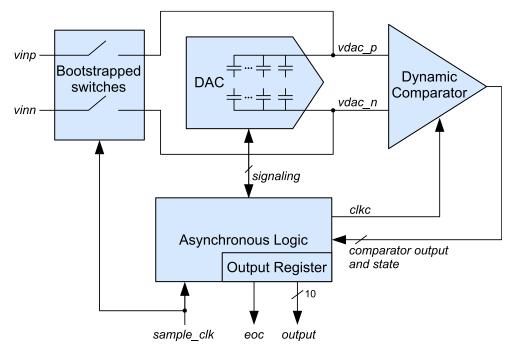

| Figure 2.6 – The ADC block diagram                                                     |

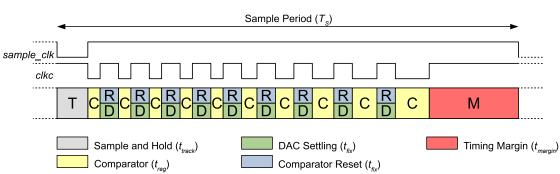

| Figure 2.7 – Timing diagram of the asynchronous SAR ADC                                |

| Figure 2.8 – Internal signal waveforms during the SAR procedure for the three least    |

| significant bits                                                                       |

| Figure 3.1 – Offset and gain errors in ADCs and DACs                                   |

| Figure 3.2 – DNL and INL errors in ADCs and DACs                                       |

| Figure 3.3 – An observation of quantization error                                      |

| Figure $3.4$ – Assumed error probability density function for the quantization error49 |

| Figure 3.5 – Frequency spectrum, in dB, and the measurement of the SFDR52              |

| Figure 3.6 – A basic sample and hold circuit                                           |

| Figure 3.7 – Bootstrapped switch concept, at sampling phase                            |

| Figure 3.8 – Switched capacitor for bootstrapped switch                                         | 7  |

|-------------------------------------------------------------------------------------------------|----|

| Figure 3.9 – Thermal noise of a resistor                                                        | 8  |

| Figure 3.10 – Noise spectrum shaping by a low pass filter                                       | 9  |

| Figure 3.11 – A simple RC circuit                                                               | 9  |

| Figure $3.12$ – (a) Sinewave having integral number of periods in the sample window. (b)        | )  |

| Sinewave having a non-integral number of periods in the sampling window                         | 1  |

| Figure 3.13 – Charge Redistribution Concept                                                     | 2  |

| Figure 3.14 – The binary-weighted capacitive DAC                                                | 4  |

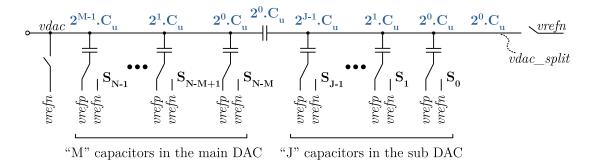

| Figure 3.15 – The split binary-weighted capacitive array                                        | 5  |

| Figure 3.16 – The modified split binary-weighted capacitive array. $\dots 6$                    | 5  |

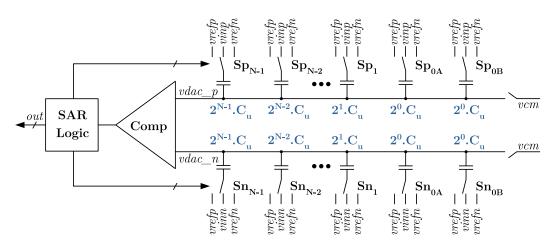

| Figure 3.17 – A conventional differential 10-bit SAR ADC                                        | 8  |

| Figure 3.18 – The Merged Capacitor Switching scheme (MCS)6                                      | 8  |

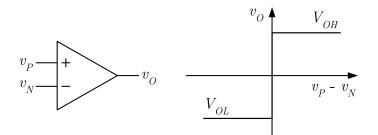

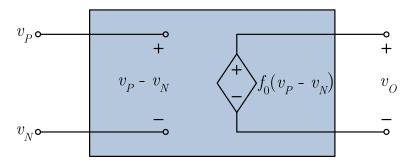

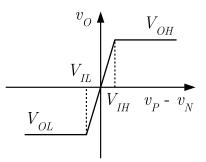

| Figure 3.19 – Comparator symbol and transfer function                                           | 0  |

| Figure 3.20 – A model for the ideal comparator                                                  | 0  |

| Figure 3.21 – The comparator transfer curve with finite gain                                    | '1 |

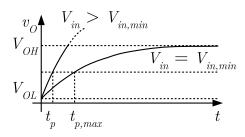

| Figure 3.22 – The small signal transient response for a step input in a comparator. $\dots 7$   | 2  |

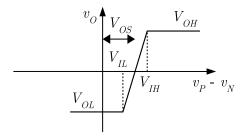

| Figure 3.23 – The comparator transfer curve, including the input-offset voltage                 | 3  |

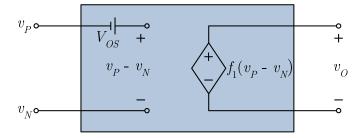

| Figure 3.24 – A model for the comparator, including the input-offset voltage                    | '4 |

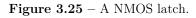

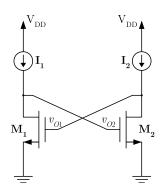

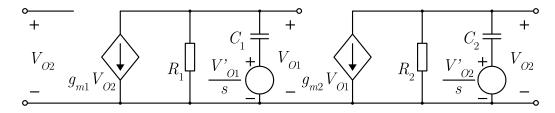

| Figure 3.25 – A NMOS latch                                                                      | 5  |

| Figure 3.26 – An equivalent model for the NMOS latch                                            | 5  |

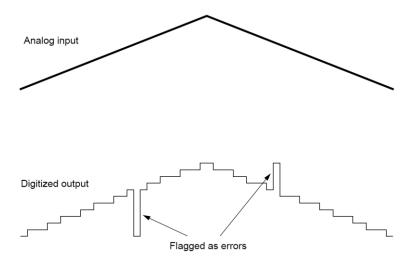

| Figure 3.27 – Typical metastability errors spotted in SAR ADCs                                  | 7  |

| Figure 3.28 – A plot of the differential input voltage of the comparator as a function $\alpha$ | of |

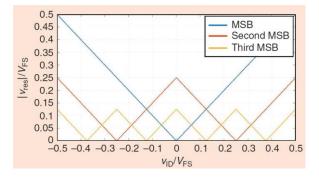

| the input voltage of a 3-bit SAR ADC, normalized to the full-scale voltage7                     | 8  |

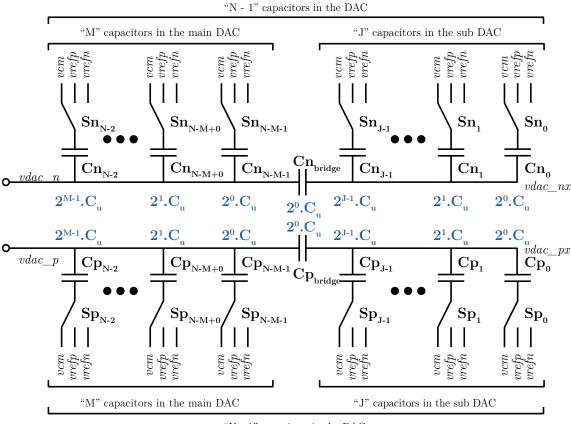

| Figure 4.1 – The capacitive DAC array                                                     |

|-------------------------------------------------------------------------------------------|

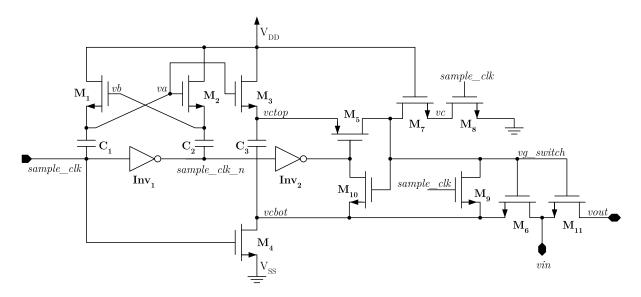

| Figure 4.2 – The bootstrapped switch schematic                                            |

| Figure 4.3 – The low kickback noise comparator                                            |

| Figure 4.4 – The SAR logic block diagram. Some signals are omitted for simplicity89       |

| Figure 4.5 – One Main Control circuit, for each bit90                                     |

| Figure 4.6 – One DAC Control circuit, for each bit90                                      |

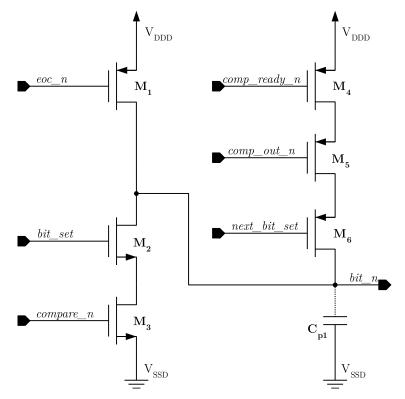

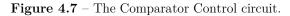

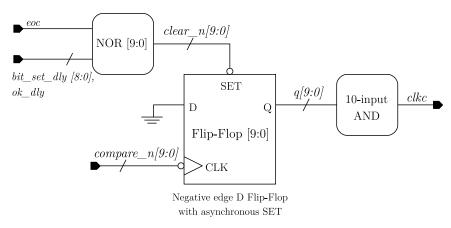

| Figure 4.7 – The Comparator Control circuit                                               |

| Figure 4.8 – One DAC Switch circuit, for each bit, with exception for the LSB one92       |

| Figure 4.9 – A model for voltage settling analysis of reference voltage sources           |

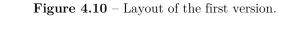

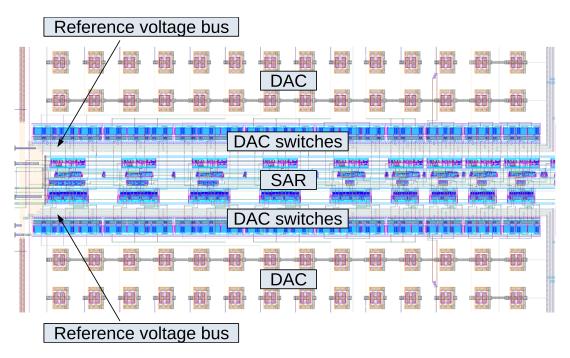

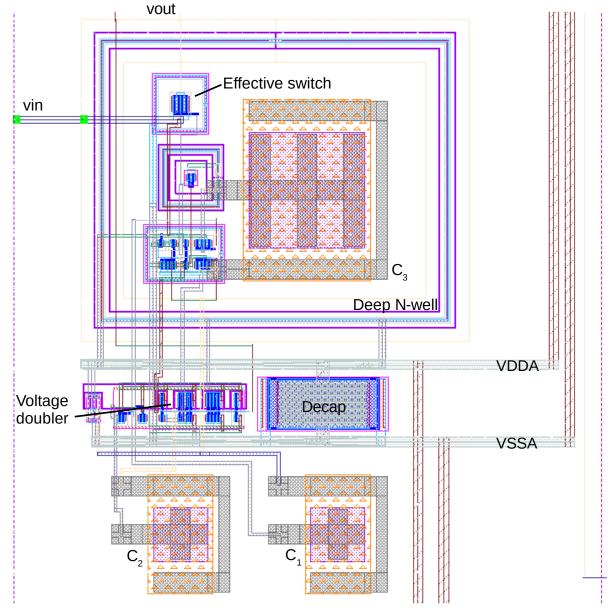

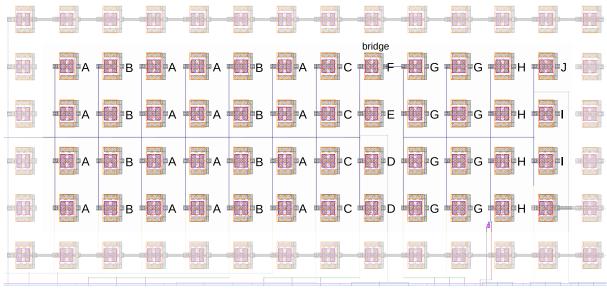

| Figure 4.10 – Layout of the first version                                                 |

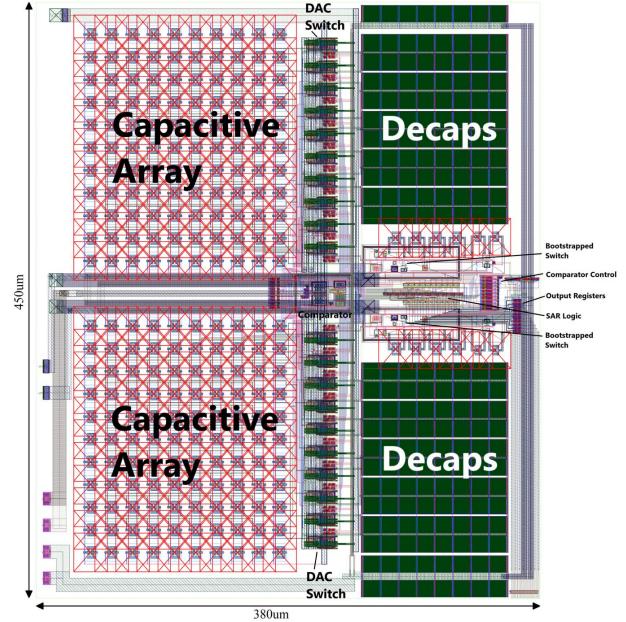

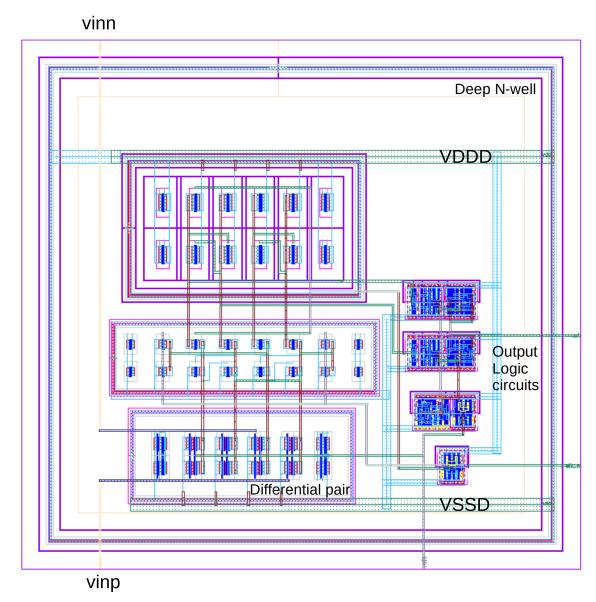

| Figure 4.11 – Layout of the second version                                                |

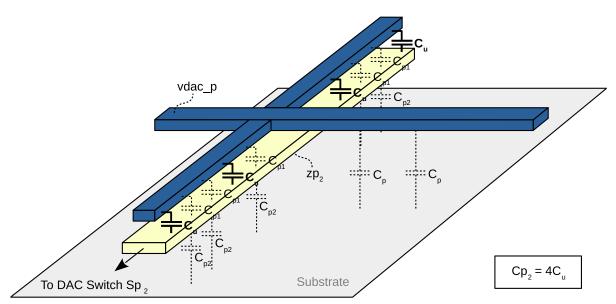

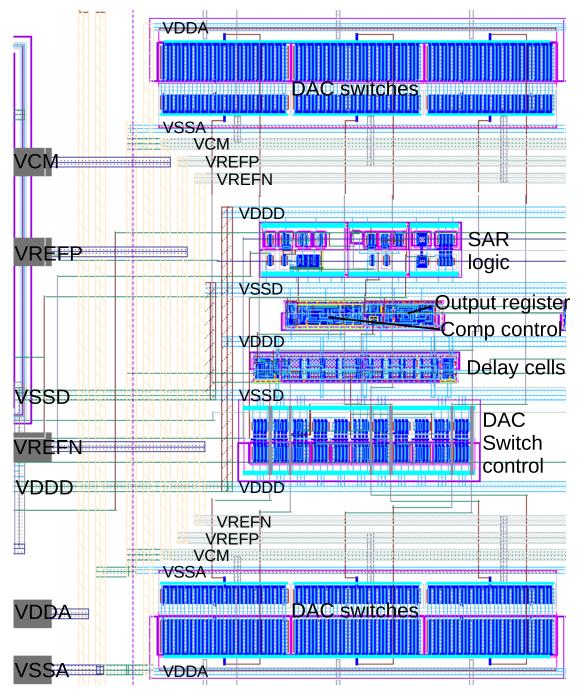

| Figure 4.12 – The top plate shielding in the capacitive DAC interconnections. $\dots 97$  |

| Figure 4.13 – Layout of the second version, zoomed at the digital circuitry and reference |

| voltages                                                                                  |

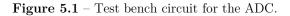

| Figure 5.1 – Test bench circuit for the ADC100                                            |

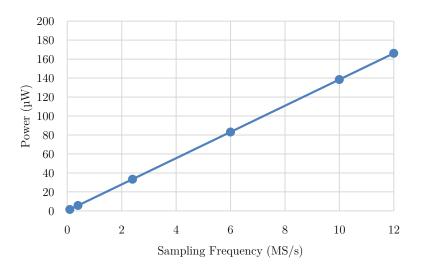

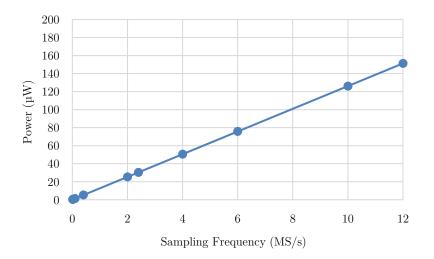

| Figure 5.2 – Simulated average power consumption vs. Sampling Frequency 102               |

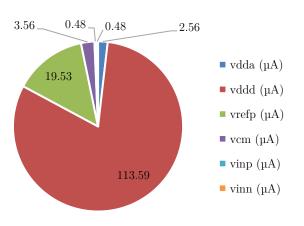

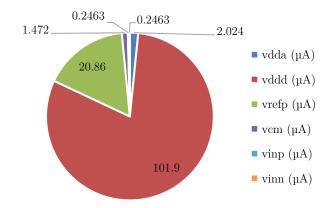

| Figure 5.3 – ADC average current consumption $@12MS/s.$                                   |

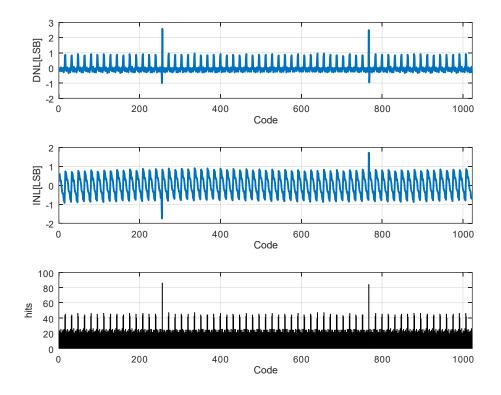

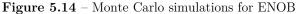

| Figure 5.4 – DNL, INL and histogram of the simulated ADC                                  |

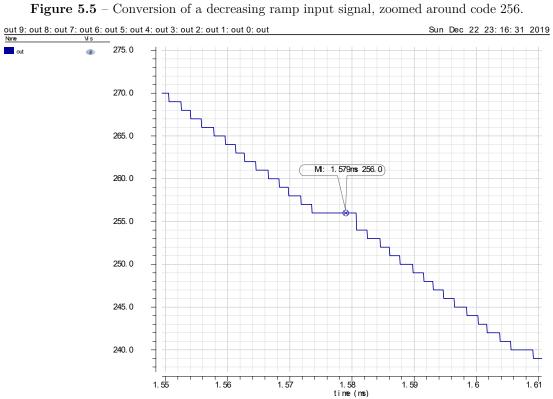

| Figure 5.5 – Conversion of a decreasing ramp input signal, zoomed around code $256.104$   |

| Figure 5.6 – Error for conversion to code 255105                                          |

| Figure 5.7 – Test bench circuit for the bootstrapped switch                               |

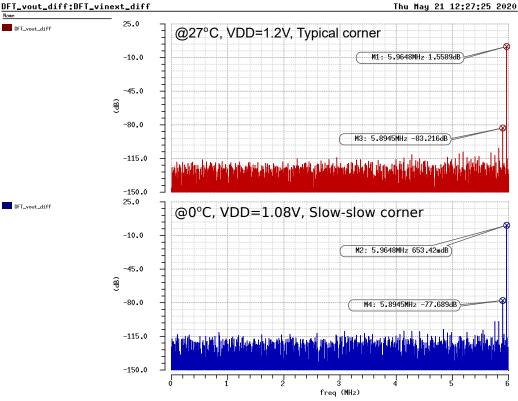

| Figure 5.8 – Computed DFT of the differential output signal of the bootstrapped switch.   |

|                                                                                           |

| 100                                                                                                 |

|-----------------------------------------------------------------------------------------------------|

| typical corner                                                                                      |

| Figure 5.10 – Computed DFT of the differential output signal of the bootstrapped switch.            |

|                                                                                                     |

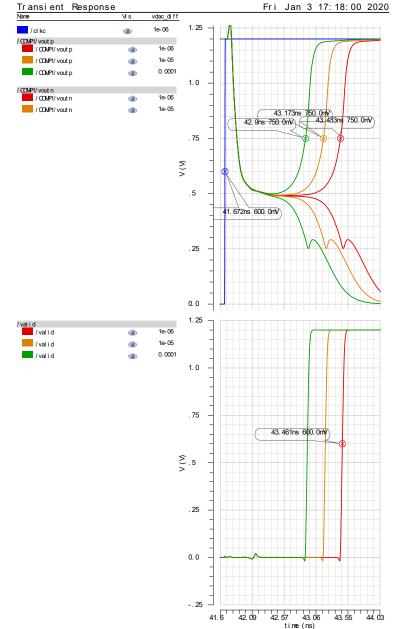

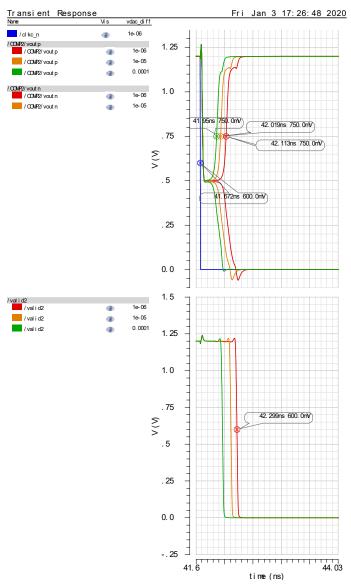

| Figure 5.11 – Comparator delay for different input voltages (1 $\mu V,$ 10 $\mu V$ and 100 $\mu V)$ |

| at typical corner                                                                                   |

| Figure 5.12 – Simulated average power consumption vs. Sampling Frequency 114                        |

| Figure 5.13 – ADC average current consumption @12MS/s 115                                           |

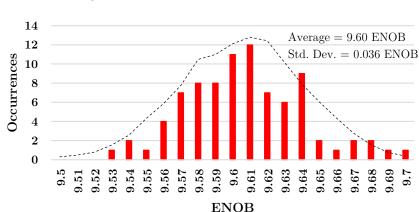

| Figure 5.14 – Monte Carlo simulations for ENOB 115                                                  |

| Figure 5.15 – DNL, INL and histogram of the simulated ADC 116                                       |

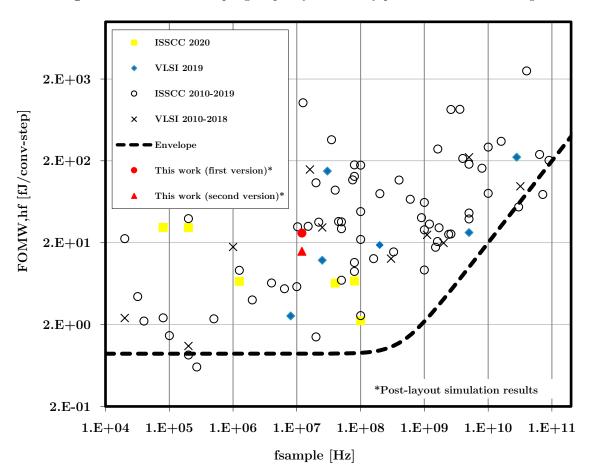

| Figure 6.1 – FOM vs. Sampling frequency for recently published SAR ADC designs. 120 $$              |

| Appendix Figure B.1 – Layout of the bootstrapped switch. 131                                        |

| Appendix Figure B.2 – Layout of the comparator. 132                                                 |

| Appendix Figure B.3 – Layout of the digital circuitry and DAC switches (zoom at the                 |

| MSB). 133                                                                                           |

| Appendix Figure B.4 – Layout of the differential capacitive DAC (one side). 134                     |

# List of tables

| Table $5.1$ – Simulated ADC dynamic parameters for different sampling frequencies (first |

|------------------------------------------------------------------------------------------|

| version)                                                                                 |

| Table 5.2 – Simulated ADC dynamic parameters for different sampling frequencies          |

| (second version)                                                                         |

| Table 6.1 – Performance comparison of similar SAR ADCs                                   |

| Appendix Table A.1 – The DAC capacitors                          | 127 |

|------------------------------------------------------------------|-----|

| Appendix Table A.2 – The DAC switch transistors, for bits 0 to 3 | 127 |

| Appendix Table A.3 – The DAC switch transistors, for bits 4 to 8 | 128 |

| Appendix Table A.4 – The bootstrapped switch transistors         | 128 |

| Appendix Table A.5 – The bootstrapped switch capacitors          | 128 |

| Appendix Table A.6 – The dynamic comparator transistors          | 129 |

| Appendix Table A.7 – The Main Control transistors                | 129 |

| Appendix Table A.8 – The DAC Control transistors                 | 129 |

# List of abbreviations and acronyms

| ADC  | Analog-to-Digital Converter                       |

|------|---------------------------------------------------|

| BER  | Bit Error Rate                                    |

| CER  | Conversion Error Rate                             |

| CMOS | Complementary Metal-Oxide-Semiconductor           |

| DAC  | Digital-to-Analog Converter                       |

| DC   | Direct Current                                    |

| DFT  | Discrete Fourier Transform                        |

| DNL  | Differential Nonlinearity                         |

| DTFT | Discrete-Time Fourier Transform                   |

| ENOB | Effective Number of Bits                          |

| ESR  | Equivalent Series Resistance                      |

| FOM  | Figure of Merit                                   |

| FS   | Full Scale                                        |

| IC   | Integrated Circuit                                |

| IEEE | Institute of Electrical and Electronics Engineers |

| IF   | Intermediate Frequency                            |

| INL  | Integral Nonlinearity                             |

| IoT  | Internet of Things                                |

| LSB  | Least Significant Bit                             |

| LTI  | Linear Time-Invariant                             |

| MCS  | Merged Capacitor Switching                        |

| MIM  | Metal-Insulator-Metal                             |

| MOS   | Metal-Oxide-Silicon                                |

|-------|----------------------------------------------------|

| MSB   | Most Significant Bit                               |

| NMOS  | N-type Metal-Oxide-Silicon Field-Effect Transistor |

| PHY   | Physical Layer                                     |

| PMOS  | P-type Metal-Oxide-Silicon Field-Effect Transistor |

| PSD   | Power Spectral Density                             |

| PVT   | Process-Voltage-Temperature                        |

| RF    | Radio Frequency                                    |

| RMS   | Root-Mean-Square                                   |

| SAR   | Successive Approximation Register                  |

| SFDR  | Spurious-Free Dynamic Range                        |

| SINAD | Signal-to-Noise-and-Distortion                     |

| SNR   | Signal-to-Noise Ratio                              |

| SR    | Slew-Rate                                          |

| THD   | Total Harmonic Distortion                          |

| TSMC  | Taiwan Semiconductor Manufacturing Company Limited |

# List of symbols

| $b_o$                | bit $o$ at the output of the ADC                                          |

|----------------------|---------------------------------------------------------------------------|

| dBc                  | Decibels relative to the carrier                                          |

| dBFS                 | Decibels relative to full scale                                           |

| $f_{in}$             | Fundamental frequency of the input signal                                 |

| $f_{sample}$         | Sampling frequency of the ADC                                             |

| $g_m$                | Transconductance of a MOS transistor                                      |

| i                    | Iteration number                                                          |

| k                    | Boltzman constant                                                         |

| $t_{\it fix}$        | Fixed time delay                                                          |

| $t_{margin}$         | Time margin                                                               |

| $t_p$                | Propagation time                                                          |

| $t_{pL}$             | Latch propagation time                                                    |

| $t_{reg}$            | Regeneration time of the comparator                                       |

| $t_{reg,hard}$       | Regeneration time of the comparator for the hardest decision              |

| $t_{track}$          | Time interval in which the ADC is sampling the input signal               |

| $v_N$                | Voltage at the negative input of the comparator                           |

| $v_P$                | Voltage at the positive input of the comparator                           |

| ζ                    | Damping ratio                                                             |

| $\mu_n$              | N-type charge-carrier effective mobility                                  |

| $\sigma(\Delta C/C)$ | Standard deviation of the difference of two identical capacitors, normal- |

|                      | ized to their absolute value, $C$                                         |

| $\sigma_u$           | Standard deviation of the mean capacitance value of $C_U$                 |

| $\sigma_{DNL,MAX}$              | Worst-case standard deviation of DNL                      |

|---------------------------------|-----------------------------------------------------------|

| ${	au}_c$                       | Time constant of the pole                                 |

| $	au_L$                         | Latch time constant                                       |

| $\omega_c$                      | Pole position                                             |

| $A_C$                           | Capacitor area                                            |

| $A_V(0)$                        | DC gain                                                   |

| $A_V(s)$                        | Transfer function in the $s$ -plane                       |

| $C_{bridge}$                    | Bridge capacitor                                          |

| $C_{f}$                         | Voltage scaling capacitor                                 |

| $C_{hld}$                       | The hold capacitor                                        |

| $C_{ox}$                        | Gate-oxide capacitance of a MOS transistor                |

| $C_p$                           | Parasitic capacitance                                     |

| $C_u$                           | Capacitance value of $C_U$                                |

| $C_{GD}$                        | Gate-drain capacitance of a MOS transistor                |

| $C_{GS}$                        | Gate-source capacitance of a MOS transistor               |

| $C_{\scriptscriptstyle OV}$     | Gate-drain/source overlap capacitance of a MOS transistor |

| $C_{\scriptscriptstyle U}$      | The unity capacitor                                       |

| Cn                              | Capacitor at the $n$ -side of the DAC                     |

| Cp                              | Capacitor at the $p$ -side of the DAC                     |

| $E_{gain(ADC)}$                 | Gain error of the ADC                                     |

| $E_{off(ADC)}$                  | Offset error of the ADC                                   |

| $E(D)_{\scriptscriptstyle DNL}$ | DNL error of the ADC, at the output code ${\cal D}$       |

| $E(D)_{\scriptscriptstyle INL}$ | INL error of the ADC, at the output code $D$              |

| H(f)                            | Transfer function                                         |

| J                               | Number of binary-weighted capacitors in the sub DAC       |

| $K_C$                           | Capacitor density                                         |

| $K_{\sigma}$                    | Capacitor matching coefficient                            |

|                                 |                                                           |

| L                | Channel length of a MOS transistor                                       |

|------------------|--------------------------------------------------------------------------|

| $L_{OV}$         | Gate-drain/source overlap length of a MOS transistor                     |

| M                | Number of binary-weighted capacitors in the main DAC                     |

| N                | ADC resolution                                                           |

| $N_{record}$     | Number of samples stored for DFT computation                             |

| $N_{\it window}$ | Number of cycles within the sampling window for DFT computation          |

| $P_{meta}$       | Probability of a metastability event to occur                            |

| $P_{noise,out}$  | Total noise power in the output                                          |

| $Q_{ch}$         | Channel charge of a MOS transistor                                       |

| $Q_{TOP}$        | Total charge on the top plate of the capacitors                          |

| $R_{ON}$         | On-resistance of a MOS transistor                                        |

| $S_{in}(f)$      | Power spectral density of the input signal                               |

| $S_{out}(f)$     | Power spectral density of the output signal                              |

| $S_v(f)$         | Power spectral density                                                   |

| Sn               | Switch at the $n$ -side of the DAC                                       |

| Sp               | Switch at the $p$ -side of the DAC                                       |

| Т                | Temperature, in Kelvin                                                   |

| $T_{easy}$       | Sum of all regeneration times during a conversion, excluding the hardest |

|                  | one                                                                      |

| $T_{FIX,TOT}$    | Sum of all fixed delays for the DAC settling                             |

| $T_S$            | Sampling period                                                          |

| $V_{e\!f\!f}$    | Effective gate-source voltage                                            |

| $V_h$            | Harmonic distortion of the ADC                                           |

| $V_{in}$         | Input voltage                                                            |

| $V_n^{\ 2}$      | Noise power density (voltage squared)                                    |

| $V_{out}$        | Output voltage                                                           |

| $V_{DAC}$        | DAC output voltage                                                       |

| $V_{DD}$         | Power supply voltage                       |

|------------------|--------------------------------------------|

| $V_{DDA}$        | Analog power supply voltage                |

| $V_{DDD}$        | Digital power supply voltage               |

| $V_{FS}$         | Full-scale voltage                         |

| $V_{GS}$         | Gate-Source voltage of a MOS transistor    |

| $V_{IH}$         | Input high logic level                     |

| $V_{IL}$         | Input low logic level                      |

| $V_{LSB}$        | 1 LSB equivalent voltage                   |

| $V_{OH}$         | Output high logic level                    |

| $V_{OL}$         | Output low logic level                     |

| $V_{OS}$         | Offset voltage                             |

| $V_Q$            | Quantization error of the ADC              |

| $V_{REF}$        | ADC reference voltage                      |

| $V_{SS}$         | Ground                                     |

| $V_{SSA}$        | Analog Ground                              |

| $V_{SSD}$        | Digital Ground                             |

| $V_{TH}$         | Threshold voltage of a MOS transistor      |

| $V_{TOP}$        | Voltage on the top plate of the capacitors |

| W                | Channel width of a MOS transistor          |

| $\Delta f$       | Frequency band                             |

| $arDelta V_{in}$ | Differential input voltage                 |

| $\Delta V_o$     | Differential output voltage                |

# Summary

| Acknowledgements                       |  |  |  |  |

|----------------------------------------|--|--|--|--|

| Abstract11                             |  |  |  |  |

| Resumo13                               |  |  |  |  |

| List of figures                        |  |  |  |  |

| List of tables                         |  |  |  |  |

| List of abbreviations and acronyms     |  |  |  |  |

| List of symbols                        |  |  |  |  |

| Summary                                |  |  |  |  |

| 1. Introduction                        |  |  |  |  |

| 1.1. Objectives                        |  |  |  |  |

| 1.2. Organization                      |  |  |  |  |

| 2. The ADC architecture                |  |  |  |  |

| 2.1. Input-output characteristics      |  |  |  |  |

| 2.2. The SAR ADC operation             |  |  |  |  |

| 2.3. Asynchronous SAR ADCs             |  |  |  |  |

| 2.4. An overview of the designed ADC40 |  |  |  |  |

| 3. System level considerations         |  |  |  |  |

| 3.1.              | The | ADC specifications                      | 15 |

|-------------------|-----|-----------------------------------------|----|

| 3.1               | L.1 | Offset and gain error                   | 15 |

| 3.1.2 DNL and INL |     | DNL and INL                             | 17 |

| 3.1               | 1.3 | Quantization noise and SNR              | 18 |

| 3.1               | 1.4 | SINAD and ENOB                          | 50 |

| 3.1               | 1.5 | Spurious-Free Dynamic Range             | 51 |

| 3.1               | 1.6 | Bit Error Rate and Converter Error Rate | 52 |

| 3.1               | L.7 | Figure of Merit                         | 53 |

| 3.2.              | The | e sample and hold circuit               | 53 |

| 3.2               | 2.1 | Switch-induced error                    | 54 |

| 3.2               | 2.2 | The bootstrapped switch                 | 55 |

| 3.2               | 2.3 | Thermal noise                           | 57 |

| 3.2               | 2.4 | Track bandwidth                         | 59 |

| 3.2               | 2.5 | Coherent sampling                       | 30 |

| 3.3.              | The | e capacitor array6                      | 32 |

| 3.3               | 3.1 | Charge redistribution                   | 32 |

| 3.3               | 3.2 | Split binary-weighted capacitive array  | 33 |

| 3.3               | 3.3 | The merged capacitor switching scheme   | 37 |

| 3.4.              | Con | nparators                               | 39 |

| 3.4               | 4.1 | Dynamic characteristics                 | 71 |

| 3.4               | 1.2 | Offset                                  | 73 |

| 3.4               | 1.3 | The regenerative comparator             | 74 |

|    | 3.4.4  | 4 Metastability                           | 77  |

|----|--------|-------------------------------------------|-----|

| 4. | The    | e SAR ADC design                          | 79  |

| 4  | 1.1. J | The capacitive DAC                        | 79  |

| 4  | 1.2. J | The sampling circuit                      |     |

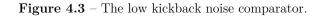

| 4  | 1.3. J | The dynamic comparator                    | 85  |

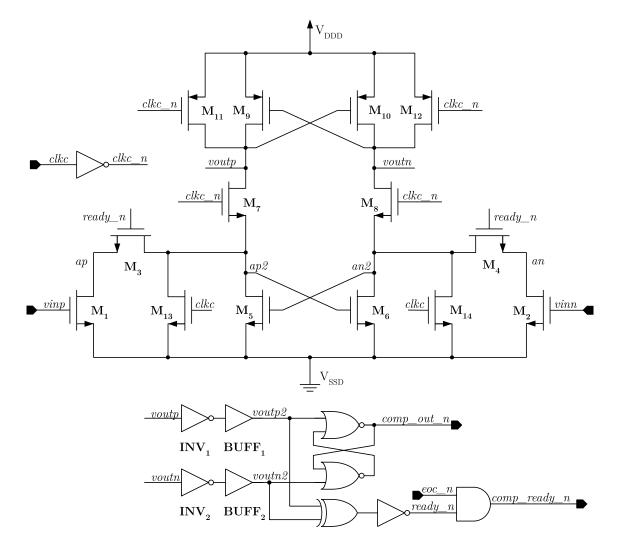

| 4  | 1.4. J | The asynchronous SAR logic                |     |

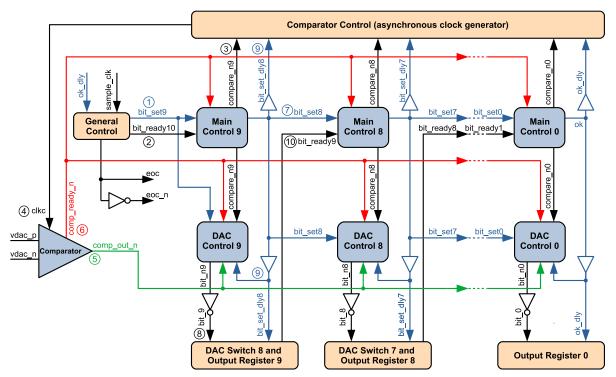

| 4  | 4.5. S | Supply and reference voltages             | 93  |

| 4  | 4.6. I | Layout                                    | 95  |

| 5. | Resu   | ults                                      | 99  |

| [  | 5.1. ] | The first version                         | 99  |

|    | 5.1.1  | 1 Power consumption and ENOB              | 99  |

|    | 5.1.2  | 2 DNL and INL                             | 102 |

|    | 5.1.3  | 3 The bootstrapped switch                 | 105 |

|    | 5.1.4  | 4 The comparator                          | 107 |

|    | 5.1.5  | 5 Metastability                           | 109 |

|    | 5.2. Т | The second version                        | 109 |

|    | 5.2.1  | 1 The redesign of the bootstrapped switch | 110 |

|    | 5.2.2  | 2 The redesign of the comparator          | 111 |

|    | 5.2.3  | 3 The redesign of the DAC switches        | 113 |

|    | 5.2.4  | 4 Power consumption and ENOB              | 113 |

|    | 5.2.5  | 5 DNL, INL, offset and gain errors        | 116 |

|    | 5.2.6  | 6 Metastability                           | 116 |

| 6. | Conclusions and future work 119 |                  |  |

|----|---------------------------------|------------------|--|

| 7. | 7. References                   |                  |  |

|    | Appendix A.                     | Devices list 127 |  |

|    | Appendix B.                     | Layout           |  |

## 1. Introduction

The adoption of internet of things (IoT) solutions for a wide range of applications, such as transportation, manufacturing, and consumer electronics, has increased over the past few years due to its potential of reducing costs and improving processes (COLUMBUS, 2018). Although the demand for software development is predominant in the IoT field, the hardware must also evolve, otherwise it could be a bottleneck for the electronic systems. For example, in low-power applications, efficient algorithms and protocols may not achieve their purpose if the hardware was not optimized for low power consumption.

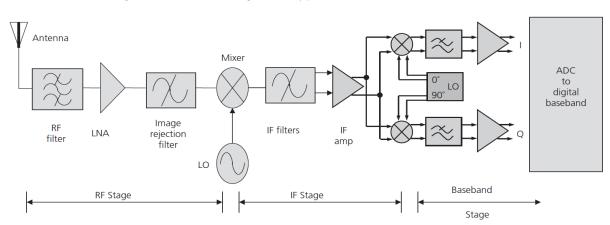

When it comes to wireless smart utility networks, like smart grid, some hardware developers are adopting the Radio Frequency (RF) transceivers described by IEEE 802.15.4g, which is an amendment of the IEEE 802.15.4 standard (low data rate and long battery life). As reference, a typical block diagram of RF receivers is shown in Figure 1.1. In this scheme, the received RF signal is filtered, amplified, and mixed down to an Intermediate Frequency (IF). At the IF stage, the signal is one more time filtered and amplified before being mixed down again to the baseband stage. In the next stage, the signal (presenting a bandwidth of just a few MHz) must be digitized by an analogto-digital converter (ADC) before demodulation at the digital circuitry.

For low power applications, the blocks that compose such complex system must present a low power consumption. Although the digital circuitry of such electronic systems benefit from the size reduction of transistors, reducing area and power consumption, their analog and mixed-signal counterparts do not necessarily benefit from new technological nodes (VAN DE PLASSCHE, 2003), being it an opportunity for researchers to innovate and propose new design techniques for low-power ADCs.

Figure 1.1 – Block diagram of typical RF communication receiver.

Source: (BOWICK, BLYLER and AJLUNI, 2008).

### 1.1. Objectives

This work aims to design an ADC using state-of-art techniques to reduce power consumption and silicon area. The ADC will be employed in the receiver circuit of an Integrated Circuit (IC) that implements the Physical Layer (PHY) for an IEEE 802.15.4g standard modem, in development by the Eldorado Research Institute, in collaboration with The University of São Paulo and The University of Campinas.

The converter must present a flexible sampling frequency, from few kS/s up to 12 MS/s. This feature allows the circuit designed in this work to be reused in a wide spectrum of low-power systems and subsystems, such as neural signal recorders and modems for different IEEE 802.15.4 standards, such as Zigbee and Thread.

For increased reliability and yield, the circuit must be designed considering fabrication process variations. Also, it should be able to support power supply variation of  $\pm$  10 % and temperature variation, ranging from 0 °C up to 85 °C.

## 1.2. Organization

This dissertation is organized as follows. After the introduction, chapter 2 presents an overview of the characteristics of a typical ADC, a quick review of the binary-search algorithm and an overview of the designed ADC. Chapter 3 revises the theoretical framework for better understanding of this work. Chapter 4 shows in details the design and layout of the ADC, along the proposed implementation of DAC switches and the top plate shielding in the layout view. The results and conclusions are shown in chapters 5 and 6.

# 2. The ADC architecture

In this chapter, an overview of the characteristics of a typical ADC and a quick review of the binary-search algorithm are presented.

### 2.1. Input-output characteristics

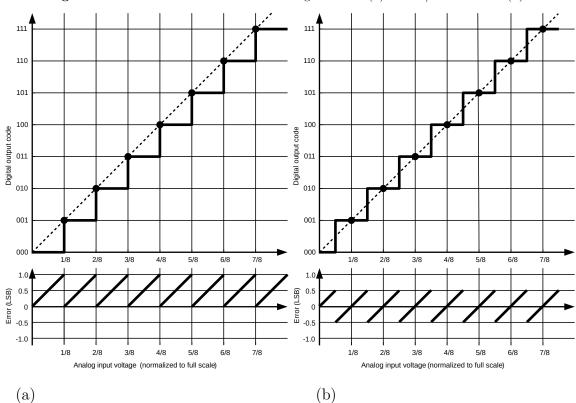

The transfer curve (or characteristic curve) of an ADC is a plot that presents the expected digital output code of the ADC according to its analog input signal. Take a 3-bit ADC as an example. The transfer curve is created by plotting the ADC output code for each input voltage, ranging from zero up to  $V_{REF}$  (the maximum input voltage) as shown in Figure 2.1(a).

Figure 2.1 – ADC transfer curve considering no offset (a) and -1/2 LSB offset (b).

Source: Author, adapted from (STALLER, 2005).

Note that for an ideal N-bit ADC this line has the shape of a "staircase", presenting  $2^N$  "levels" of 1 Least Significant Bit (LSB) width, where the LSB width is  $V_{LSB} = V_{REF}/2^N$ . Considering that an hypothetical ideal infinite resolution ADC presents a transfer function given by a straight line (the dashed line in Figure 2.1(a)), we can state that a real N resolution ADC presents a conversion error, for a determined input voltage, given by the difference between the real ADC transfer curve and the infinite resolution ADC transfer curve at the input voltage. The conversion error is also known as quantization error. From Figure 2.1(a), the maximum quantization varies from 0 (dots) to +1 LSB.

An alternative view of the input-output characteristic is created by shifting the transfer function to the left by 1/2 LSB, as shown in Figure 2.1(b). This new graph presents a quantization error ranging from -1/2 LSB to +1/2 LSB, which is a particularly useful approach for the quantization error analysis.

### 2.2. The SAR ADC operation

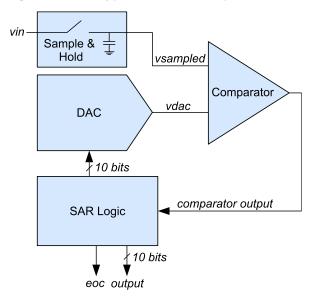

The Successive Approximation Register (SAR) ADC topology makes use of a binary search algorithm to perform the analog-to-digital conversion. This topology presents a fast operation, while keeping a moderate circuit complexity (JOHNS and MARTIN, 1997), and is well suited for moderate resolutions and low-to-medium data rate applications (FREDENBURG and FLYNN, 2015). It is composed by a sample and hold circuit, a Digital-to-Analog Converter (DAC), a comparator, and a digital circuitry to execute a binary search procedure and to store the conversion result. Figure 2.2 illustrates a typical implementation of the SAR ADC.

During the binary search procedure, successive digital words for the internal DAC are produced, and its output voltage,  $V_{DAC}$ , will increasingly approach the sampled  $V_{in}$ . At the end of the search procedure, a final digital word is found, which is composed by a vector of bits ranging from  $b_0$  up to  $b_{N-1}$ , where N is the resolution of the ADC.

Figure 2.2 – A typical SAR ADC implementation.

Source: Author.

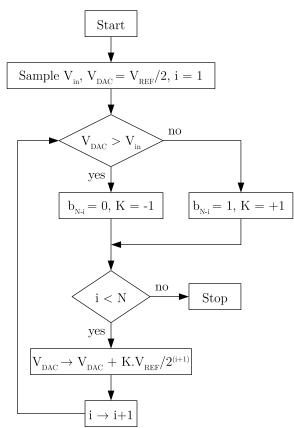

#### The flowchart of Figure 2.3 describes the binary search algorithm of a SAR ADC.

Figure 2.3 – Flowchart of a typical binary search used in SAR ADCs.

Source: Author, adapted from (JOHNS and MARTIN, 1997).

First, the converter samples  $V_{in}$ , sets *i* (the iteration number) to 1 and sets,

through application of the appropriated digital word, the  $V_{DAC}$  to  $V_{REF}/2$ . Next, N iterations are executed. For each iteration, the  $V_{DAC}$  is compared to  $V_{in}$ . If the  $V_{DAC}$  is smaller than  $V_{in}$ ,  $b_{N-i}$  is set to 1 and  $V_{DAC}$  will increase by  $V_{REF}/2^{i+1}$  before the next iteration, otherwise  $b_{N-i}$  is set to 0 and  $V_{DAC}$  will decrease by  $V_{REF}/2^{i+1}$  before the next iteration. Finally, *i* is increased by 1. This compare and set procedure is repeated until all bits are resolved.

For an ideal ADC,  $V_{DAC}$  will differ from  $V_{in}$  by no more than  $V_{REF}/2^{N+1}$  after the  $N^{\text{th}}$  iteration, meaning the current values in the vector of bits at the DAC are the converted output code.

# 2.3. Asynchronous SAR ADCs

Typical SAR ADCs make use of two clock sources: one to control the sampling (the sampling clock) and other to control the iterations of the binary search algorithm (the SAR clock). Since each iteration in the SAR procedure is synchronized to the SAR clock, this converter is classified as synchronous. On the other hand, there are SAR ADCs, like the ones presented in (CHEN and BRODERSEN, 2006) and (HARPE, ZHOU, *et al.*, 2010), that need only one clock signal, which is responsible for controlling the data sampling. In this case, the iterations of the search algorithm are controlled by a set of combinational digital circuits, delay cells and registers. Since these circuits are not synchronized by any clock source, these types of SAR ADCs are categorized as asynchronous.

The requirement of only one clock source in asynchronous implementations is advantageous since it relaxes the specifications of any frontend circuits responsible for providing clock signals to ADCs working in different sampling rates, attending specifications of diverse smart utility networks.

Another notable advantage of the asynchronous implementation, compared to the synchronous one, is the increased robustness to metastability problems. As analyzed in (YU, BANKMAN, *et al.*, 2019), and shown in Figure 2.4, the synchronous implementation allocates an individual time budget for each iteration to finish the comparison and set the DAC with the new code value. The remaining time margin (M, highlighted in red) is available to be used by the comparator during a hard decision comparison, i.e., when a small voltage is applied to its input, significantly increasing the comparison time (C, highlighted in yellow). Since there will be only one hard decision among the N iterations of the binary search procedure, the time margin available for the remaining N-1iterations are unused and these time margins are wasted.

Figure 2.4 – Time chart of synchronous and asynchronous SAR ADCs.

On the other hand, in the asynchronous implementation, each iteration is triggered as soon as the previous one is finished, giving no timing margin between them, resulting in a single timing margin at the end of the last iteration. This continuous timing

Source: (YU, BANKMAN, et al., 2019).

margin can be interpreted as a much bigger headroom available for the comparator, during the hard decision, to quit the metastable state, whichever iteration it is in. This time margin is further increased, as shown in Figure 2.5, when the resolution of the ADC is also increased, because there are more time margins to be "borrowed" from unused bit decisions. As a result, medium/high resolution asynchronous SAR ADCs are expected to present an extremely smaller probability of entering in a metastable event than its synchronous counterpart.

Figure 2.5 – A graph of the probability of a metastable event, for different ADC resolutions.

Source: (YU, BANKMAN, et al., 2019).

# 2.4. An overview of the designed ADC

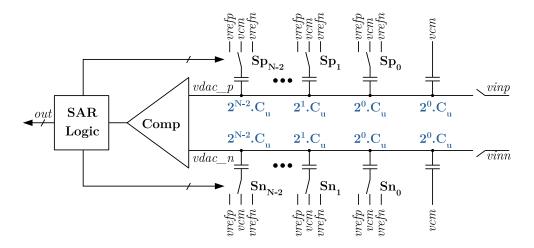

In this work an asynchronous SAR ADC was implemented. As mentioned in the previous sub-section, this kind of converter requires only one clock source, relaxing the clock distribution requirements. A block diagram of the designed circuit is shown in Figure 2.6 and present a differential architecture. Differential circuits can greatly minimize the effects of common-mode noise and even order harmonics distortion (VAN DE PLASSCHE, 2003). In the block diagram of Figure 2.2, *vsampled* and *vdac* are periodically compared. It is intuitive that, since they are generated by different circuits and present different metal traces, both nodes pick up noise differently, affecting the comparison result, especially when *vsampled* and *vdac* present similar voltage values during a hard decision. Conversely, in Figure 2.6, both signals at the input of the comparator are

provided by identical sub circuits with symmetrical routing, meaning they will ideally pick up noise evenly and the subtraction procedure of the comparator will intrinsically cancel it out (or at least minimize it).

Figure 2.6 – The ADC block diagram.

Source: Author.

The ADC implemented in this work is composed by: 1) a pair of input switches, implemented using the bootstrapped technique to improve linearity; 2) a pair of capacitor arrays (capacitive DAC); 3) a dynamic comparator; 4) an asynchronous logic; and 5) output registers. A sampling clock (*sample\_clk*) controls the bootstrapped switches and the asynchronous logic circuit that sets the ADC to either sampling or conversion phase. When the sampling clock is set to low (sampling phase), the bootstrapped switches turn on and the capacitor array of the DAC is charged according to the differential input signal. In this phase, the power consumption of the ADC is quite low because there is no digital circuit activity and the analog circuits present low current consumption.

When the sampling clock is set to high (conversion phase), the bootstrapped switches are turned off and the SAR procedure is triggered, starting the binary search procedure, which takes N iterations, where N is the resolution of the ADC. In the first iteration,  $vdac\_p$  and  $vdac\_n$  signals remain constant. From the second iteration on, the  $vdac\_p$  and  $vdac\_n$  signals themselves have their values modified by (N - 1) additions/subtractions of  $V_{FS}/2^i$ , where  $V_{FS}$  is the single full-scale voltage  $(V_{DD})$  and i is the iteration number, ranging from 2 up to N.

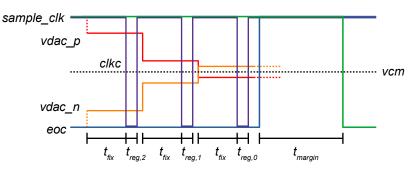

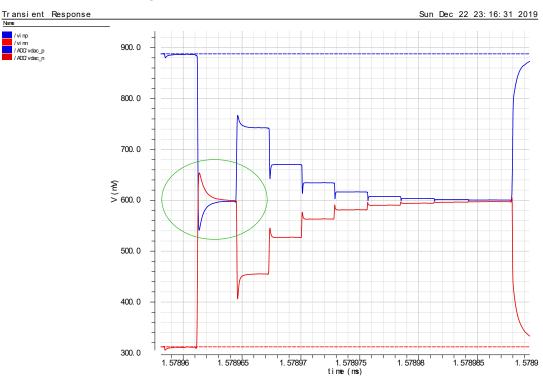

The timing diagram of the asynchronous SAR ADC is shown in Figure 2.7. In the diagram are pointed out the sampling clock (*sample\_clk*), the comparator asynchronous clock (*clkc*), and the time intervals at which the signal sampling ( $t_{track}$ ), the comparator regeneration ( $t_{reg}$ ), and the comparator reset/DAC charge redistribution ( $t_{fix}$ ) are performed. In Figure 2.8, the behavior of the *sample\_clk*, *clkc*, *vdac\_p*, *vdac\_n*, and the end-of-conversion flag (*eoc*) are shown with details during the evaluation of the three least significant bits.

Figure 2.7 – Timing diagram of the asynchronous SAR ADC.

Source: Author, adapted from (YU, BANKMAN, et al., 2019).

Figure 2.8 – Internal signal waveforms during the SAR procedure for the three least significant bits.

Source: Author.

For each of the iterations presented in Figure 2.8, the DAC charge redistribution

and the comparator reset are first triggered. After a fixed time interval  $t_{fix}$ , the *clkc* signal falls, indicating that a new differential input is provided for the comparator and that the comparator itself is ready. Next, a comparison (regeneration) is performed in a variable interval  $t_{reg}$  and, when the result is ready, a signal is sent to the asynchronous logic circuit, causing the rising of *clkc*. At the end of the iteration, the asynchronous logic commands the storage of the result and the start of a new iteration.

An end-of-conversion flag (*eoc*) will indicate that the SAR iterations were successfully performed, and the conversion result will be available at the output registers. The time delay between the beginning of the conversion phase and the rising of the *eoc* flag is mostly limited by the sum of comparator decision time during each iteration and the combinational circuits delay, due to its parasitic elements. For the iteration in which  $(vdac\_p - vdac\_n) = \Delta V_{in}$  is the smallest, the regeneration time,  $t_{reg,hard}$ , can be much higher than the regeneration time of the other iterations.

Note that most of the ADC energy consumption is observed to occur in the interval between the rising of the sampling clock signal (triggering of the asynchronous logic circuit) and the rising of the *eoc* flag. Since the size of this time interval and the amount of operations performed in it does not scale with the sampling frequency, it is expected an almost linear relation between power consumption and sampling frequency (HARPE, ZHOU, *et al.*, 2010). This relation is compromised for low sampling frequencies, once in this case the ADC power consumption will be dominated by the static power consumption.

# 3. System level considerations

In this chapter some data conversion concepts are reviewed for better understanding of the design and performance indicators of the ADC. Next, characteristics, physical effects and architectures of its sub-circuits are introduced.

# 3.1. The ADC specifications

The specifications of an electrical circuit are the designer's guide to choose appropriated design techniques, leading to a better use of resources like silicon area and power consumption. Some of the most important ADC specifications are shown in this section.

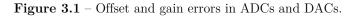

## 3.1.1 Offset and gain error

The ADC offset error is defined as the shift of the actual ADC transfer curve from the ideal one (section 2.1). It indicates how much the first transition point, between 0...00code to 0...01 code, is deviated from 1/2 LSB (JOHNS and MARTIN, 1997). It can be found mathematically as

$$E_{off(ADC)} = \frac{V_{0...01}}{V_{LSB}} - \frac{1}{2}LSB, \qquad (3.1)$$

where the  $E_{off(ADC)}$  is the offset error in units of LSBs and  $V_{0\dots01}$  is the input voltage which produces the first transition in the actual ADC.

The ADC gain error is defined as the deviation of the last step's midpoint of the actual ADC transfer curve from the last step's midpoint of the ideal one, when the offset error is reduced to zero (JOHNS and MARTIN, 1997). The gain error indicates how well the slope of both transfer curves match each other (MAXIM INTEGRATED, 2002). It

can be found mathematically as:

$$E_{gain(ADC)} = \left(\frac{V_{1..11}}{V_{LSB}} - \frac{V_{0..01}}{V_{LSB}}\right) \ - \ (2^N - 2), \tag{3.2}$$

where the  $E_{gain(ADC)}$  is the gain error and  $V_{1...11}$  is the input voltage which produces the last transition in the transfer curve. The offset and gain errors in ADCs and DACs are shown in Figure 3.1.

#### OFFSET ERROR

Source: (MAXIM INTEGRATED, 2002).

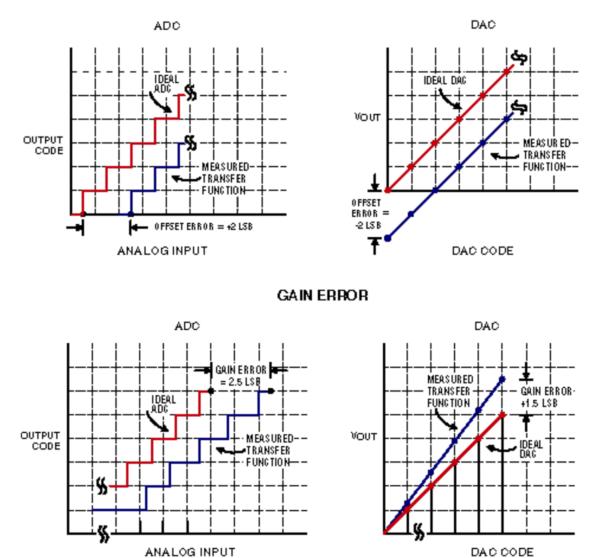

## 3.1.2 DNL and INL

If we look at the transfer curve of an ideal *N*-bit ADC (section 2.1), it can be observed that each level ideally presents a width of 1 LSB. The ADC Differential Nonlinearity (DNL) error refers to the deviation in the width of any of these levels from the ideal value of 1 LSB. The analysis in (VAN DE PLASSCHE, 2003) states that the DNL error at an output code D can be written as

$$E(D)_{DNL} = \left(\frac{V_{m+1} - V_m}{V_{LSB}}\right) - 1LSB, \quad 0 < D < 2^N - 2.$$

(3.3)

The  $V_m$  and  $V_{m+1}$  are two adjacent input voltages which produce, respectively, the transitions (D-1) to D and D to (D+1) in the transfer curve, once the offset and gain errors are removed.

The ADC Integral Nonlinearity (INL) is the deviation of the actual transfer curve from an imaginary straight line that passes through the middle points of all steps (JOHNS and MARTIN, 1997). The INL at the output code D can be computed as the sum of the DNLs from code 1 up to code D. The INL calculation is also performed after offset and gain errors have been compensated and can be found as

$$E(D)_{INL} = \left(\frac{V_{m,ideal} - V_{m,actual}}{V_{LSB}}\right).$$

(3.4)

The DNL and INL errors in ADCs and DACs are shown in Figure 3.2. Note that if the maximum DNL error is less than 1 LSB and the maximum INL error is less than 0.5 LSB, the ADC is guaranteed to not present any missing codes in its transfer function (JOHNS and MARTIN, 1997). Also, unless otherwise stated, the literature often considers the DNL/INL error as the maximum DNL/INL error found in the full transfer function span.

DNL

## 3.1.3 Quantization noise and SNR

ADC INPUT

Quantization is a process of dividing a quantity in a discrete number of small parts (GRAY and NEUHOFF, 1998). In data converters, this process is unavoidable and introduces error (quantization error) even in ideal circuits (JOHNS and MARTIN, 1997), as shown in section 2.1.

= I DEAL DAC

= MEASURED TRANSFER FUNCTION

DAC CODE

The stochastic analysis, presented in (JOHNS and MARTIN, 1997), can be used to better understand the impact of this error in the performance of the ADC. First, we consider the circuit shown in Figure 3.3, composed by two N-bits ideal converters, where the quantization noise signal,  $V_Q$ , is modeled as the quantized signal,  $V_1$ , minus the input signal,  $V_{in}$ .

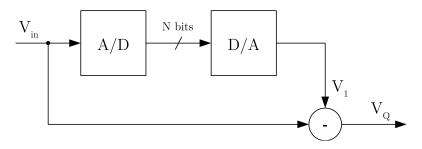

Figure 3.3 – An observation of quantization error.

Source: Author, adapted from (JOHNS and MARTIN, 1997).

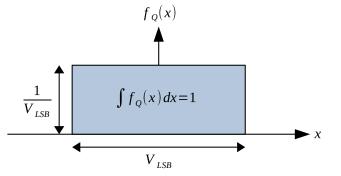

In this analysis,  $V_Q$  is considered to present a uniform distribution in the range from  $-V_{LSB}/2$  up to  $+V_{LSB}/2$ , as shown in Figure 3.4, where  $f_Q(x)$  is the error probability density and x is the quantization error.

$Figure \ 3.4 - {\rm Assumed \ error \ probability \ density \ function \ for \ the \ quantization \ error.}$

Source: Author, adapted from (JOHNS and MARTIN, 1997).

The Root-Mean-Square (RMS) value of the error  $V_Q$  can be calculated as

$$V_{Q(rms)} = \left[\frac{1}{V_{LSB}} \left(\int_{\frac{-V_{LSB}}{2}}^{\frac{V_{LSB}}{2}} x^2 \, dx\right)\right]^{1/2} = \frac{V_{LSB}}{\sqrt{12}}.$$

(3.5)

Now, the RMS value of  $V_Q$  can be used to determine the Signal-to-Noise Ratio (SNR) of an ideal ADC. The SNR is the most important ADC specification and is a good indication of its dynamic performance (VAN DE PLASSCHE, 2003). It is used to analyze how much noise was added into the original signal by the ADC after a conversion. The

SNR of an ideal *N*-bit ADC due to quantization error is calculated by taking the logarithm of the ratio between the power of a full-scale sinusoidal input, with amplitude of  $2^{N-1} \cdot V_{LSB}$ , and the estimated power of the quantization error,  $V_Q$ , leading to

$$SNR = 20 \log \left(\frac{\frac{V_{LSB} \cdot 2^{N-1}}{\sqrt{2}}}{\frac{V_{LSB}}{\sqrt{12}}}\right) = 6.02N + 1.76dB.$$

(3.6)

Therefore, an ideal 10-bit ADC will present a SNR of 61.96 dB, meaning that this is the maximum theorical SNR value for a 10-bit ADC. Non-ideal ADCs present a degraded SNR because the non-ideal characteristic curve and the other sources of noise will increase  $V_Q$  in the denominator of equation 3.6.

Note that equation 3.6 is a simplified estimative of the SNR. Although there are more accurate deductions of the SNR for converters with resolutions above 3 bits, equation 3.6 is a general accepted formula (VAN DE PLASSCHE, 2003).

## 3.1.4 SINAD and ENOB

The Signal-to-Noise-and-Distortion (SINAD) parameter indicates how much noise and distortion were added into the original signal after the analog-to-digital conversion. It is an important specification because its calculation includes the SNR and the Total Harmonic Distortion (THD) as components that degrade the performance of the ADC. The SINAD relation is (ANALOG DEVICES, 2005):

$$SINAD = 20 \log \frac{V_{in(RMS)}}{\sqrt{V_{Q(RMS)}^2 + V_{h(RMS)}^2}},$$

(3.7)

where  $V_{h(RMS)}$  is the RMS of the harmonic distortion.

The SINAD can be estimated by first applying a sinusoidal signal in the input of the ADC, turning the circuit on during a predefined number of conversions and saving the outputs into a vector of binary codes. Next, the binary codes are converted to analog values and the Discrete-Time Fourier Transform (DTFT) is applied to generate the frequency spectrum of the converted signal. The computation of the DTFT requires a high computational power, so, in practice, it is taken the Discrete Fourier Transform (DFT) (OPPENHEIM and SCHAFER, 1999).

Finally, the SINAD is calculated by taking the RMS value of the base frequency component and dividing by the root-sum-square of all other spectral components, including harmonics and excluding the Direct Current voltage (DC) level component (ANALOG DEVICES, 2009).

For ADC testing and characterization this parameter is usually converted to Effective Number of Bits (ENOB). To find the ENOB, one replaces the SNR in equation 3.6 by the measured circuit SINAD, leading to a non-ideal value for N, that express the effective resolution:

$$ENOB = \frac{SINAD - 1.76dB}{6.02}.$$

(3.8)

Measuring the ENOB, however, can lead to errors if the input signal approaches full scale because the output codes can saturate at codes 0 or  $2^{N} - 1$ , significantly degrading the DFT spectrum. A practical method for better ENOB measurement is to use a reduced input signal level and apply a correction factor in equation 3.8 (ANALOG DEVICES, 2009) leading to the new expression

$$ENOB = \frac{SINAD - 1.76dB + 20\log(\frac{Fullscale Amplitude}{Input Amplitude})}{6.02}.$$

(3.9)

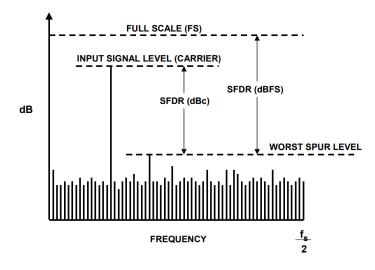

#### 3.1.5 Spurious-Free Dynamic Range

The Spurious-Free Dynamic Range (SFDR) is a specification that indicates how much is the difference between the maximum, or fundamental, carrier component and the largest distortion component in the frequency spectrum of the converted output signal (VAN DE PLASSCHE, 2003). The SFDR is calculated by dividing the input signal component by the largest distortion component. In Decibels relative to the carrier (dBc) scale, it can be easily extracted from the frequency spectrum graph by taking the input signal component and subtracting the largest distortion component, as shown in Figure 3.5. For practical converters, the predominant distortion components are the second and third harmonics.

Figure 3.5 – Frequency spectrum, in dB, and the measurement of the SFDR.

## 3.1.6 Bit Error Rate and Converter Error Rate

The Bit Error Rate (BER) of a digital system is the number of errors expected to be observed in data transmissions. The specification of the BER of a system is somewhat subjective and takes in account the desired average time between errors, which can vary significantly for different applications (VAN DE PLASSCHE, 2003). The Conversion Error Rate (CER) of an ADC is a figure that estimates the probability of a converted code to present an erroneous value.

Even though both parameters seems to be similar, their errors have different causes, as pointed out in (BEAVERS, 2014). For example, the determination of the BER of a digital system is straightforward because one can simply transmit a specific set of data and observe it at the receiver side. The difference between the received and expected data are counted as bit errors. On the other hand, the determination of the CER of an

Source: (ANALOG DEVICES, 2005).

ADC requires special attention because the cause of an erroneous data conversion could be from an intrinsic characteristic of the converter, like DNL, INL, offset and gain error, or could be a non-expected conversion error mainly due to noise and/or metastability problems. The CER of a SAR ADC is typically dominated by the probability of its comparator entering in a metastable state, which is introduced in sub-section 3.4.4

## 3.1.7 Figure of Merit

A well accepted index for comparison of different ADCs is the Figure of Merit (FOM) (VAN DE PLASSCHE, 2003) given by

$$FOM = \frac{Power}{2.f_{in}.2^{ENOB}},\tag{3.10}$$

where FOM is expressed in J/Conversion-steps,  $f_{in}$  is the fundamental frequency of the input signal, ENOB is the equivalent number of bits and *Power* is the power consumption. For Nyquist-rate ADCs, the applied input signal frequency should be slightly lower than half the sampling frequency.

## 3.2. The sample and hold circuit

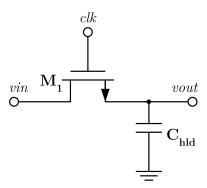

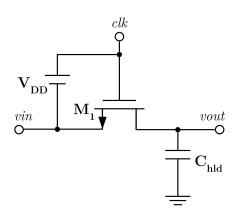

Sample and hold circuits are widely used in ADCs. They are responsible for sampling an analog signal and storing its value for some defined time for analysis. A simple example of such circuit is shown in Figure 3.6.

This sample and hold circuit is composed by a simple switch, the Metal-Oxide-Silicon (MOS) transistor  $M_1$ , and a storage element, the hold capacitor  $C_{hld}$ . As analyzed in (JOHNS and MARTIN, 1997) when *clk* is logical high, transistor  $M_1$  is on and *vout* follows *vin*. When *clk* goes low, transistor  $M_1$  is off and *vout* will remain ideally constant, having a value equal to *vin*. In practice, *vout* will present errors due to charge flow in and from  $C_{hld}$  and parasitic capacitances. Figure 3.6 – A basic sample and hold circuit.

Source: Author, adapted from (JOHNS and MARTIN, 1997).

## 3.2.1 Switch-induced error

The sample hold switches present two well-known error sources responsible by the so-called switch-induced error: the charge injection and the clock feedthrough. The charge injection error is caused by the transistor channel charge that goes to the capacitor when the transistor goes to off. The first-order analysis in (JOHNS and MARTIN, 1997) estimates the charge injection error by calculating the charge flow from the channel into  $C_{hld}$ . In Figure 3.6, considering the clock signal is fast enough, the channel charge ( $Q_{ch}$ ) is expected to flow evenly to both transistor terminals (source and drain) (SHIEH, PATIL and SHEU, 1987). The charge variation in  $C_{hld}$  is then given by

$$\Delta Q_{C_{hld}} = \frac{Q_{ch}}{2} = \frac{C_{ox}WLV_{eff}}{2},\tag{3.11}$$

where  $C_{ox}$  is the gate-oxide capacitance per area of the transistor, W and L are the width and length of the transistor, and  $V_{eff}$  is given by

$$V_{eff} = V_{GS1} - V_{TH} = V_{DD} - V_{TH} - vin, \qquad (3.12)$$

where  $V_{GS1}$  is given by the difference between the *clk* voltage at logical high ( $V_{DD}$ ) and the input voltage (*vin*), and  $V_{TH}$  is the threshold voltage of the transistor. We can find the voltage error due to charge injection,  $\Delta V'$ , by using the relationship Q = CV in equation 3.11, which results in

$$\Delta V' = -\frac{C_{ox}WL(V_{DD} - V_{TH} - vin)}{2C_{hld}}.$$

(3.13)

The clock feedthrough error is caused by the coupling between the clk and the vout signals. The coupling is due to the gate-drain/source overlap capacitances of the MOS transistor. Further analysis is performed in (JOHNS and MARTIN, 1997) to estimate the voltage error in vout due to the clock feedthrough. The gate overlap capacitance  $(C_{OV})$  of  $M_1$  forms a capacitor arrangement with  $C_{hld}$ . The charge variance in  $C_{OV}$ , due to the clk transition from high to low,  $Q_{OV} = C_{OV} (V_{DD} - V_{SS})$ , will cause in vout a voltage error,  $\Delta V''$ , whose value can be calculated by using the capacitor-divider formula

$$\Delta V'' = -\frac{(V_{DD} - V_{SS})C_{OV}}{C_{hld} + C_{OV}},\tag{3.14}$$

which can be approximated by

$$\Delta V^{\prime\prime} \cong -\frac{C_{ox}WL_{OV}(V_{DD} - V_{SS})}{C_{hld}},\tag{3.15}$$

where  $V_{SS}$  is the *clk* low logical level and  $L_{OV}$  is the gate-drain/source overlap length.

The effect described by equation 3.13 is called charge injection and its contribution to the total voltage error is more expressive that the one described in equation 3.15, which is known as clock feedthrough. Note that for differential sampling circuits, where two symmetrical switches are employed, the effects of clock feedthrough are minimized because both branches will present similar errors. However, the effect of charge injection will not cancel out because it is dependent on *vin*.

## 3.2.2 The bootstrapped switch

The design of high linear analog switches is essential when it comes to design of medium-to-high resolution ADCs. Say a *N*-bit SAR ADC must be designed. If the error added by the switch into the sampled signal is higher than half the  $V_{LSB}$ , the effective resolution of the converter will be degraded. Therefore, bootstrapped switches have been

widely used in SAR ADCs (DYACHENKO, 2012) (FIRLEJ, FIUTOWSKI, *et al.*, 2015), which present high linearity by keeping its on-resistance nearly constant even for a wide input swing (STEENSGAARD, 1999).

As stated in (RAZAVI, 2001), the on-resistance of a n-type MOS (NMOS) transistor in triode region depends on  $V_{eff}$  (equation 3.12) and is given by

$$R_{ON} = \frac{1}{\mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{TH})} = \frac{1}{\mu_n C_{ox} \frac{W}{L} V_{eff}},$$

(3.16)

where  $R_{ON}$  is the on-resistance of the transistor and  $\mu_n$  is the electron mobility. Equation 3.16 elucidates that basic switches, like the one implemented in the sample and hold circuit in Figure 3.6, suffer from a nonlinear behavior due to different input voltage levels, that induce distortions.

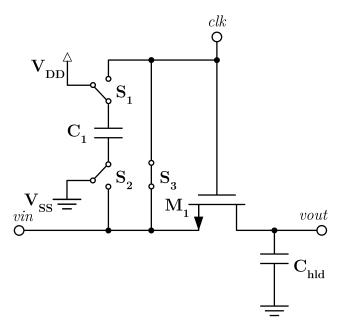

The bootstrapped switch can minimize this problem, as mentioned before, by maintaining  $V_{GS}$  constant over the entire input swing, although a small variation in  $V_{TH}$ will still be present. The circuit concept is illustrated in Figure 3.7. In this circuit,  $V_{GS1}$ is kept constant by mean of a voltage source. In general, the value of the voltage source is chosen to be equal to  $V_{DD}$ , which implies that the transistor gate voltage should go from  $V_{DD}$  to  $2V_{DD}$  when the input changes from  $V_{SS}$  to  $V_{DD}$ . A practical implementation of the voltage source makes use of a switched capacitor circuit to perform voltage doubling and is shown in Figure 3.8.

Figure 3.7 – Bootstrapped switch concept, at sampling phase.

Source: Author, adapted from (STEENSGAARD, 1999).

Figure 3.8 – Switched capacitor for bootstrapped switch.

Source: Author, adapted from (STEENSGAARD, 1999).

The switched capacitor circuit is composed by three switches and the capacitor  $C_1$ . Its operation is as follows: during the hold phase the  $C_1$  is charged to  $V_{DD}$  and the gate of  $M_1$  is shorted to its source. During the sample phase the gate and source of  $M_1$  are not shorted anymore and  $C_1$  is attached to them, producing a constant  $V_{GS1}$ .

## 3.2.3 Thermal noise

As shown in Figure 3.6, a basic sample and hold circuit is made of a switch and a hold capacitor. The switch analysis of (RAZAVI, 2001) estimates the noise due to random motion of electrons, which induces fluctuations in the voltage across a conductor. This noise is proportional to temperature and is known as thermal noise.

Prior the analysis of this circuit, the thermal noise of a resistor is introduced, since a non-ideal MOS switch, in triode region, has the behavior similar to that of a resistor. The Power Spectral Density (PSD),  $S_v(f)$ , of the thermal noise of a resistor R is

$$S_v(f) = 4kTR, \ f \ge 0, \tag{3.17}$$

where  $k = 1.38.10^{-23}$  J/K is the Boltzmann constant. The  $S_v(f)$ , expressed in V<sup>2</sup>/Hz, states

how much power the signal carries at each frequency (per 1Hz bandwidth).

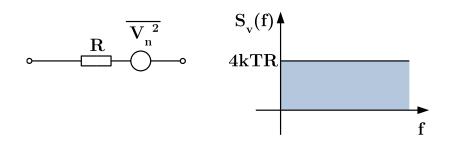

In circuit analysis, the thermal noise of a resistor can be modeled as a voltage source in series with the noiseless resistor, as shown in Figure 3.9.

Figure 3.9 – Thermal noise of a resistor.

Source: Author, adapted from (RAZAVI, 2001).

It is important to notice that noise is a random process, meaning that instantaneous values of voltages and currents cannot be predicted. The average power, though, is predictable in many cases and can be calculated from a long time scale waveform. So, the voltage source of Figure 3.9 indicates the average power (noise voltage squared). In fact,  $\overline{V_n}^2 = 4kTR\Delta f$ , where  $\Delta f$  is the frequency band of the measurement.

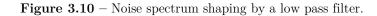

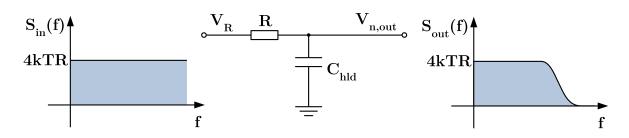

The model for the resistor thermal noise can be applied into the calculation of the noise generated by a simple RC low pass filter to proper estimate the noise introduced by the sample and hold circuit. As shown in Figure 3.10, the series voltage source that represents the noise of R,  $V_R$ , is used to compute the transfer function

$$\frac{V_{out}}{V_R}(s) = \frac{1}{RCs+1}.$$

(3.18)

In a Linear Time-Invariant (LTI) system, the PSD of the input signal,  $S_{in}(f)$ , and the PSD of the output signal,  $S_{out}(f)$ , are related by the following theorem (COUCH, 1993):

$$S_{out}(f) = S_{in}(f)|H(f)|^2, \qquad (3.19)$$

where H(f) is the transfer function of the LTI system.

Source: Author, adapted from (RAZAVI, 2001).

By combining equations 3.18 and 3.19 we obtain the expression of the PSD at the output of the sample and hold circuit, which can be integrated, in frequency domain, to provide the total noise power in the output, resulting in

$$P_{noise,out} = \frac{kT}{C_{hld}}.$$

(3.20)

The unit of  $P_{noise,out}$  is V<sup>2</sup> and we can take the square root of this expression to obtain the RMS noise, also known as KTC noise.

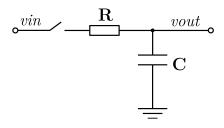

## 3.2.4 Track bandwidth

Switched-capacitor based sampling circuits have a limited capacity of charging/discharging its hold capacitor at high frequency operation. The maximum input signal frequency is limited by the RC nature of the circuit, which can be analyzed as a simple RC charging circuit, shown in Figure 3.11.

Figure 3.11 – A simple RC circuit.

Source: Author.

In the abovementioned circuit, the hold capacitor is initially discharged and the input voltage  $V_{in}$  is constant. When the switch is closed it will present the voltage settling

behavior given by the charging capacitor equation

$$V_{out}(t) = V_{in} \left[ 1 - e^{\frac{-t}{RC}} \right].$$

(3.21)

Considering the circuit has a 50% duty cycle, i.e., the switch is turned on during half of the sampling period, the voltage in the hold capacitor has this exact amount of time to settle to the input signal with some voltage error, according to specifications.

The maximum allowed voltage error for a 10-bit SAR ADC, with input swing of  $V_{in} = V_{DD}$ , is

$$\Delta V_e \le \frac{V_{LSB}}{2} = \frac{V_{DD}}{2^{N+1}},$$

(3.22)

where N is the ADC resolution.

Combining equations 3.21 and 3.22, the constraint for track bandwidth is

$$\frac{1}{2^{N+1}} \le e^{\frac{-0.5T_S}{RC}},\tag{3.23}$$

where  $T_s$  is the sampling period.

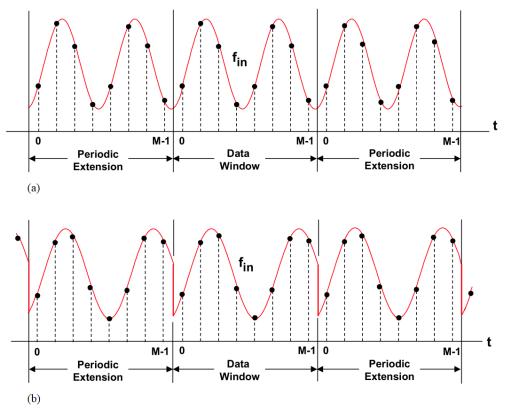

## 3.2.5 Coherent sampling

Coherent sampling is a relevant topic in characterization of ADCs. Suppose we need to plot the frequency spectrum of the output waveform of an ADC. One approach is to apply a sinusoidal signal in the input of the ADC, turn the circuit on during a predefined number of conversions (data window) and save the outputs into a vector of binary codes. Now, similarly to the process described in sub-section 3.1.4, each element of this vector is converted to uniformly-spaced samples of continuous values and the DFT of the resulting vector is performed to obtain the converted signal in the frequency domain.

Since the DFT supposes a periodic expansion of the signal in the time domain, the correct representation of the signal in the frequency domain is only achieved when the sample frequency is set to sample an integer number of periods in the sampling window (MAXIM INTEGRATED, 2002), as shown in Figure 3.12(a). If a non-integer number of periods is used to compute the DFT, the periodic expansion of the data window will present a discontinuity, as shown in Figure 3.12(b), and the frequency components of the signal will present incorrect magnitudes.

The sampled waveform discontinuity (spectral leakage) can be reduced if the following condition is true:

$$\frac{f_{in}}{f_{sample}} = \frac{N_{window}}{N_{record}},\tag{3.24}$$

where  $f_{in}$  is the periodic input signal,  $f_{sample}$  is the sampling frequency of the ADC,  $N_{window}$  is the integer number of cycles that the signal completes within the sampling window and  $N_{record}$  is the number of samples stored for the DFT computation.

Figure 3.12 – (a) Sinewave having integral number of periods in the sample window. (b) Sinewave having a non-integral number of periods in the sampling window.

Source: (ANALOG DEVICES, 2005).

Note that there are some restrictions on choosing  $N_{record}$  and  $N_{window}$ : for taking advantage of the numerical algorithms that implement the DFT,  $N_{record}$  must be a power of 2. Additionally, to ensure samples will not be repeated across any signal period, a prime number (except for 2) must be chosen for  $N_{window}$ .

## 3.3. The capacitor array

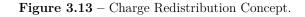

Low-power SAR ADCs that use capacitive DACs typically adopt the charge sharing or charge redistribution techniques (RABUSKE and FERNANDES, 2017). In this section, the charge redistribution technique is presented for proper introduction of the split array topology and the merged capacitor switching scheme.

## 3.3.1 Charge redistribution

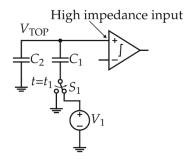

The charge redistribution technique has been largely employed in SAR ADCs during the last decades. By taking advantage of the constant charge in a capacitor network, one may switch the bottom plate of any number of its elements to different voltage levels in order to induce a defined voltage level at the top plate of the capacitors (common node). The example of Figure 3.13 illustrates this concept.

Source: (RABUSKE and FERNANDES, 2017).

In this example, as analyzed in (RABUSKE and FERNANDES, 2017), the voltage variation in  $V_{TOP}$  caused by switching  $S_1$  is derived as follows. When  $t=t_0$  the bottom plates of both capacitors are shorted to ground, and their total charge,  $Q_{TOP}$ , is given by

$$Q_{TOP}(t_0) = V_{TOP}(t_0)(C_2 + C_1). \tag{3.25}$$

Now, consider that at  $t=t_1$  the bottom plate of  $C_1$  is switched to  $V_1$  through  $S_1$ . After proper settling of  $V_{TOP}$  at  $t_2$ , where  $t_0 < t_1 < t_2$ , the charge in the top plates is given by

$$Q_{TOP}(t_2) = V_{TOP}(t_2)C_2 + (V_{TOP}(t_2) - V_1)C_1.$$

(3.26)

Since there is conservation of charge in the top plate, we can state that  $Q_{TOP}(t_0) = Q_{TOP}(t_2)$ , leading to

$$V_{TOP}(t_2) = V_{TOP}(t_0) + V_1 \frac{C_1}{C_1 + C_2}.$$

(3.27)

By extrapolating this concept, an increased number of capacitors can be used to define an increased number of possible voltage levels for  $V_{TOP}$ .

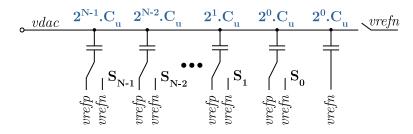

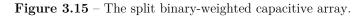

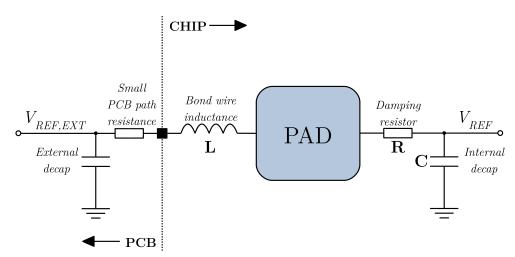

## 3.3.2 Split binary-weighted capacitive array