# INSTITUTO DE PESQUISAS ENERGÉTICAS E NUCLEARES Autarquia Associada à Universidade de São Paulo

Evaluation of impurities in the Brazilian solar grade silicon and LeTID investigations in p-type multi-Si

**DANIEL KNOB**

Tese apresentada como parte dos requisitos para obtenção do Grau de Doutor em Ciências na Área de Tecnologia Nuclear - Materiais

**Orientador:**

Prof. Dr. Humberto Gracher Riella

São Paulo 2019

# INSTITUTO DE PESQUISAS ENERGÉTICAS E NUCLEARES

# Autarquia Associada à Universidade De São Paulo

# Evaluation of impurities in the Brazilian solar grade silicon and LeTID investigations in p-type multi-Si

# **DANIEL KNOB**

Thesis presented as part of the requirements to obtain the Degree of Doctor of Science in the area of Nuclear Technology – Materials

Advisor: Prof. Dr. Humberto Gracher Riella

Versão Corrigida

São Paulo

2019

Autorizo a reprodução e divulgação total ou parcial deste trabalho, para fins de estudo e pesquisa, desde que citada a fonte

Como citar:

KNOB, D. *Evaluation of impurities in the Brazilian solar grade silicon and LeTID investigations in p-type multi-Si*. 2019. 150 p. Tese (Doutorado em Tecnologia Nuclear), Instituto de Pesquisas Energéticas e Nucleares, IPEN-CNEN/SP, São Paulo. Disponível em: (data de consulta no formato: dd/mm/aaaa)

Ficha catalográfica elaborada pelo Sistema de geração automática da Biblioteca IPEN/USP, com os dados fornecidos pelo(a) autor(a)

Knob, Daniel

Evaluation of impurities in the Brazilian solar grade

silicon and LeTID investigations in p-type multi-Si / Daniel

Knob; orientador Humberto Gracher Riella. -- São Paulo, 2019.

150 p.

Tese (Doutorado) - Programa de Pós-Graduação em Tecnologia

Nuclear (Materiais) -- Instituto de Pesquisas Energéticas e

Nucleares, São Paulo, 2019.

1. Solar Grade Silicon. 2. Multycrystalline Silicon. 3.

Solar PV. 4. LeTID. I. Gracher Riella, Humberto , orient. II.

Título.

Clara, minha filha, que este esforço seja por um mundo melhor.

Dedico a você e à Luciana.

À Cidinha, Paulo, Tiago, Júlia e bebê, primos e amigos. Aos meus avós. Miguel, Romilda, Osvaldo e Georgina, em memória.

## **ACKNOWLEDGMENT**

To Igor Martins, lab partner who provided indispensable support for the development of this work.

To Edvaldo Dal Vechio, whose technical support was essential to the thesis, in addition to the moral support.

To Elita F. Urano, for the endless help during the entire work.

To Bent Thomassen, Junjie Zhu from IFE, for the support on laboratory work.

To my father, Paulo José Knob, for the contribution in the work and overall incentive.

To Rune Søndenå, for the joint work and all shared knowledge.

To my Advisor, Humberto Gracher Riella, for the trust, shared knowledge and all the effort on the project.

To IFE (Institute for Energy Technology), for the opportunity of conducting the joint work and for providing lab structure.

To CCN (Centro de Combustível Nuclear) and IPEN for the opportunity and lab structure.

"It is under the greatest adversity that there exists the greatest potential for doing good, both for oneself and others."

Dalai Lama XIV

#### **ABSTRACT**

KNOB, D. *Evaluation of impurities of the Brazilian solar grade silicon and LeTID investigations in p-type multi-Si*. 2019. 119 p. Thesis (Doctorate in Nuclear Technology - Materials) – Instituto de Pesquisas Energéticas e Nucleares – IPEN – CNEN/SP. São Paulo

The cost reductions and the environmental benefits aligned with global concerns about climate change have made solar photovoltaic technology the most installed source of energy in the power sector worldwide. Brazil has the largest know reserves of silicon in the world. Therefore, there is a huge potential for developing a national technology for purifying and manufacturing silicon wafers within an increasingly competitive and efficient photovoltaic industry. The IPEN initiative of investigating the production of metallic silicon and metallurgical route purification required a characterization of samples in different stages of production from quartz to wafer and understanding the characterization methods for silicon wafers taking into account the main defect mechanisms such as light-induced degradation. Metalic silicon is produced in IPEN via magnesiothermal reduction through acid leaching to form a metallurgical grade silicon with relatively low impurities. One more acid leaching step resulted in a specific ultrametallurgical grade silicon. The same acid leaching was processed in a commercially available Brazilian-made metallurgical grade silicon produced via carbothermal reduction. All samples impurities was measured by ICP-OES. The result is a material with ultra-metallurgical grade silicon content with excess of B and P. While wafer characterization was studied, an extensive investigation was taken on LeTID, which causes remain unknown, at Institute for Energy Technology, Norway. Neighboring high performance mc-Si p-type wafers were tested in different firing process conditions. The effects was investigated in terms of defects activation and a corresponding lifetime degradation and recovery at illuminated annealing. A sample with almost fully suppressed LeTID is shown. A new method have been proposed to separate Boron Oxygen-Light Induced Degradation effects of LeTID, enabling to measure even where it was thought to be fully suppressed. New models for LeTID defect formation and suppression are proposed. Both silicon purification and light-induced degradation characterization in mc-Si studies shows a wide range of research on new production routes that may require tailored processes of crystallization and solar cell manufacturing such as gettering and firing.

**Keywords:** 1. Solar Grade Silicon. 2. Multycrystalline Silicon. 3. Solar PV. 4. LeTID.

#### **RESUMO**

KNOB, D. *Evaluation of impurities of the Brazilian solar grade silicon and LeTID investigations in p-type multi-Si*. 2019. 119 p. Thesis (Doctorate in Nuclear Technology - Materials) – Instituto de Pesquisas Energéticas e Nucleares – IPEN – CNEN/SP. São Paulo

As reduções de custos e benefícios ambientais alinhadas às preocupações globais com as mudanças climáticas tornaram a tecnologia solar fotovoltaica a fonte de energia mais instalada no setor de energia do mundo. O Brasil possui as maiores reservas conhecidas de silício. Portanto, existe um enorme potencial para o desenvolvimento de uma tecnologia nacional para purificação e fabricação de wafers de silício dentre a indústria fotovoltaica cada vez mais competitiva e eficiente. A iniciativa do IPEN de investigar a produção de silício metálico e a purificação de rotas metalúrgicas exigiu a caracterização de amostras em diferentes estágios de produção, do quartzo ao wafer e a compreensão dos métodos de caracterização dos wafers de silício, levando em consideração os principais mecanismos de defeitos, como a degradação induzida pela luz. O silício metálico é produzido no IPEN através da redução magnesiotérmica através da lixiviação ácida para formar um silício de grau metalúrgico com impurezas relativamente baixas. Mais uma etapa de lixiviação ácida resultou em um silício de grau ultra-metalúrgico específico. A mesma lixiviação foi feita em um silício de grau metalúrgico fabricado no Brasil, disponível comercialmente, produzido por redução carbotérmica. Todas as amostras foram medidas por ICP-OES. O resultado é um material com teores de silício de grau ultra-metalúrgico e excesso de B e P. Enquanto a caracterização do wafer foi estudada, uma extensa investigação foi realizada sobre o LeTID, que tem causas desconhecidas, no Institute for Energy Technology, Noruega. Os wafers vizinhos de mc-Si do tipo-p de alto desempenho foram testados em diferentes condições do processo de firing. Os efeitos foram investigados em termos de ativação de defeitos e uma correspondente degradação e recuperação no lifetime sob recozimento iluminado. Uma amostra com LeTID quase totalmente suprimido é mostrada. Um novo método foi proposto para separar os efeitos de Degradação Induzida por Luz relacionados ao Oxigênio e Boro do LeTID, permitindo até medir onde se pensava que estivesse totalmente suprimido. Novos modelos para formação e supressão de defeitos LeTID são propostos. Tanto a purificação de silício quanto a caracterização de degradação induzida pela luz nos estudos de mc-Si mostram uma ampla gama de pesquisas sobre novas rotas de produção que podem exigir processos personalizados de cristalização e fabricação de células solares, como gettering e firing.

Palavras-chave: 1. Silício Grau Solar. 2. Silício Multicristalino. 3. Solar FV. 4. LeTID.

# LISTO F TABLES

| Table 1 – Acceptable contamination (C) by impurities calculated for silicon feedstock, wafers and solar                    |

|----------------------------------------------------------------------------------------------------------------------------|

| cells36                                                                                                                    |

| Table 2 – Chemical specification for solar grade silicon. Data in ppm (weight), except the data followed                   |

| by (a), which indicates ppm (atomic)                                                                                       |

| Table 3 –Target impurity concentrations in UMG and SoG silicon (all values in ppmw)38                                      |

| Table 4 - Specification of the impurities contained in the solar grade silicon for the production of solar                 |

| cells according to SEMI PV 49-061339                                                                                       |

| $Table\ 5\ -\ Studies\ and\ data\ considered\ according\ to\ the\ manufacturing\ processes\ of\ multicrystalline\ silicon$ |

| by the metallurgical route61                                                                                               |

| Table 6 - Impurities data obtained by ICPOES; reference for metallurgical, ultra-metallurgical and solar                   |

| grade silicon68                                                                                                            |

| Table 7 - Impurities data obtained by ICPOES for: C - resulted magnesiumthermic silicon leached with                       |

| HCl (25%) + HF (5%) (50°C and 6 hours); D - the commercial carbothermic silicon leached with                               |

| HCl (25%) + HF (5%) (50°C and 6 hours); reference for ultra-metallurgical and solar grade silicon.                         |

| 69                                                                                                                         |

| Table 8 – Measured resistivity, reflectiveness, mass and calculated thickness of the produced wafers by                    |

| the different routes. Average lifetime was obtained with the PL equipment74                                                |

| Table 9 – Data from each firing profile and calculated maximum normalized BO-corrected degradation                         |

| (LeTID representative)                                                                                                     |

| Table 10 – Model B with LeTID triggering temperature for each firing profile, assuming when the                            |

| thermal budgets above 600°C value reached 50°C.s                                                                           |

| Table 11 – Calculated rate of defect formation and the rate of emptying of LeTID defects reservoir,                        |

| considered represented by the difference between maximum normalized BOcorrected lifetime                                   |

| degradations under illuminated annealing for each profile divided by the difference between thermal                        |

| 1 1 1 1 10000                                                                                                              |

| budgets above 600°C.                                                                                                       |

| Table 12 – Results for profiles #5 and SBS compared with results from literature                                           |

|                                                                                                                            |

# LIST OF FIGURES

| Figure 1 - A simple climate model to a pathway in which net CO <sub>2</sub> emissions (grey line) decline in a straight line from 2020 to reach net zero in 2055. The blue line is a response to a faster CO <sub>2</sub> emissions reduction, reaching net zero in 2040, reducing cumulative CO <sub>2</sub> emissions. The purple line shows the response to net CO <sub>2</sub> emissions declining to zero in 2055 with net non-CO <sub>2</sub> forcing remaining constant after 2030 [2]. |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2 - Evolutionary development of the electricity generation for the global energy transition from 2015 to 2050. The model is based on hourly resolution for an entire year, the world structured in 145 regions, high spatial resolution of the input RE resource data, and transition steps of 5-year                                                                                                                                                                                   |

| Period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 3 - Evolution of global total solar PV installed capacity 2000-2017                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 4 Seasonal global solar avarage radiation of Brazil                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 5 - Daytime generation curve of a summer day, of February 2019, including renewable generation curves of hydro, wind and solar sources, fossil thermal and nuclear. a) Real daytime generation curves; (b) daytime generation curves with the hydro generation subtracted by the actual solar PV generation multiplied by a factor of ten (c) daytime generation curves with the hydro generation                                                                                       |

| subtracted by the actual solar PV generation multiplied by a factor of thirty                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Figure 6 – Schematic of a carbothermal MG-silicon reactor                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Figure 7 - Metallurgical purification route from MG-Si to SoG-Si, the refining steps consists of a combination of metallurgical techniques                                                                                                                                                                                                                                                                                                                                                     |

| Figure 8- Schematic illustration of a directional solidification furnace                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Figure 9 – (a) polycrystalline silicon bricks (b) polycrystalline silicon wafers                                                                                                                                                                                                                                                                                                                                                                                                               |

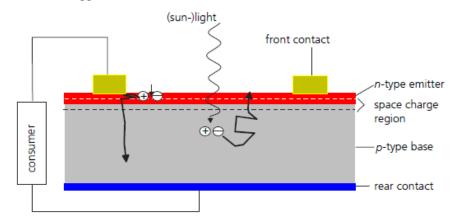

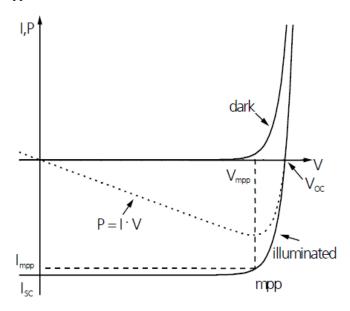

| Figure 10 – Schematic drawing of a simple solar cell. The absorbed light creates electron-hole pairs,                                                                                                                                                                                                                                                                                                                                                                                          |

| which are extracted at opposite the metal contacts30                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 11 – Schematic drawing of a simple solar cell. The absorbed light creates electron-hole pairs, which are extracted at opposite the metal contacts                                                                                                                                                                                                                                                                                                                                       |

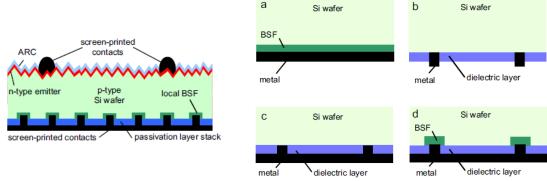

| Figure 12 – Left: Schematic design of a passivated emitter and rear cell (PERC); Right: Schematic design of different rear surface passivation of crystalline silicon solar cells: (a) large area back surface field (BSF), (b) dielectrically passivated bifacial structure, (c) passivated emitter and rear cell (PERC), and (d) passivated emitter, rear locally diffused (PERL)-type cell                                                                                                  |

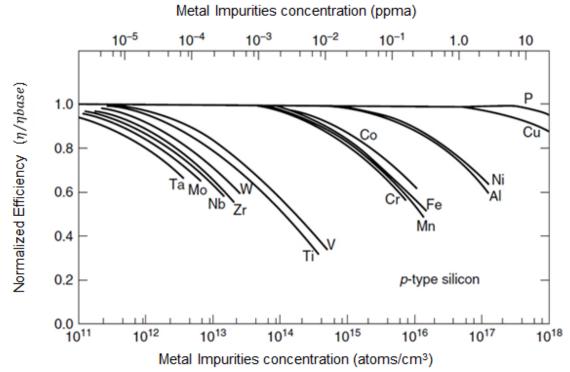

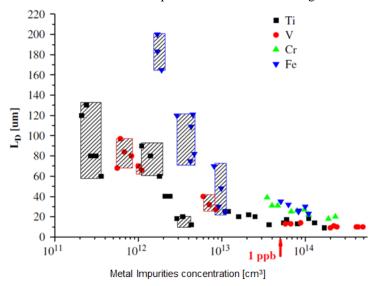

| Figure 13 – Efficiency of the solar cell related with concentration of impurities                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 14 – Influence of the concentration of impurities on the diffusion length of minority carriers34                                                                                                                                                                                                                                                                                                                                                                                        |

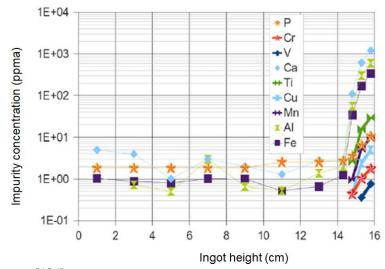

| Figure 15 – Metal impurities along the ingot produced by directional solidification                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 16 – The segregation of dopants and resistivity distribution in an ingot grown from compensated                                                                                                                                                                                                                                                                                                                                                                                         |

| silicon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

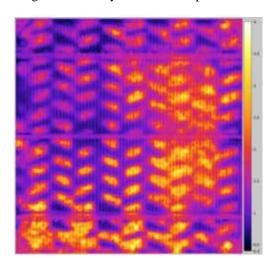

| Figure 17 – Series resistance image of a multicrystalline Si cell performed on a BT Imaging LIS-R144 Figure 18 – Effective Lifetime of minority carriers from a Photoluminescence Image of a passivated multicrystalline Silicon wafer                                                                                                                                                                                                                                                         |

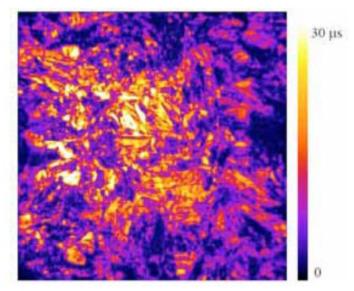

| Figure 19 – Bulk lifetimes of a multicrystalline silicon brick from a photoluminescence image                                                                                                                                                                                                                                                                                                                                                                                                  |

| normalized by doping and calibrated with QSSPC4                                                                                                                                                                                                                                                                                                                                                                                                                                                |

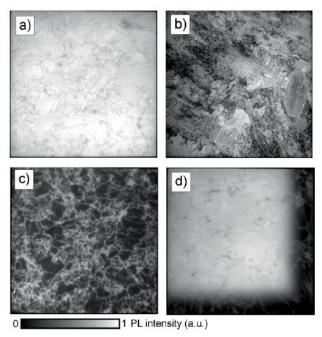

| Figure 20 – PL image taken on four as-cut mc-Si wafers: (a) a wafer from a center brick with few                                                                                                                                                                                                                                                                                                                                                                                               |

| dislocations, (b) a wafer from a center brick with high dislocation density, (c) a wafer from the                                                                                                                                                                                                                                                                                                                                                                                              |

| impurity rich area at the bottom and (d) a wafer from a corner brick with low dislocation density4                                                                                                                                                                                                                                                                                                                                                                                             |

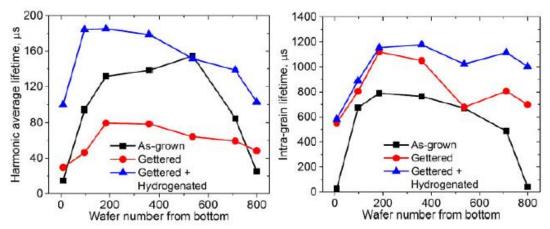

| Figure 21 – Left: average lifetime of intra-grain regions extracted from photoluminescence images in HPMC-Si wafers before and after gettering and firing. Right: harmonic average lifetime extracted                                                                                                                                                                                                                                                                                          |

| from photoluminescence images of the same wafers                                                                                                                                                                                                                                                                                                                                                                                                                                               |

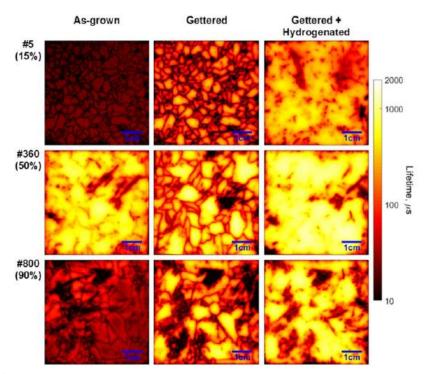

| Figure 22 – Photoluminescence images of various mc-Si wafers selected before and after gettering and                                                                                                                                                                                                                                                                                                                                                                                           |

| hydrogenation. The samples were double sided passivated. A logarithmic color scale is used in the figure. The wafer number of the bottom of the ingot and the corresponding fraction of the height of                                                                                                                                                                                                                                                                                          |

| the ingot, based on the height of the ingot, are shown in the left column                                                                                                                                                                                                                                                                                                                                                                                                                      |

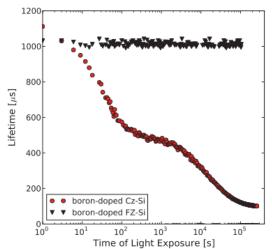

| -1 iguio 25 - Enomino as a function of right exposure for a-start passivated botton doped C2-st and F2-st 50                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 24 - Kersten et al [31] data, illuminated annealing (300W.m <sup>-2</sup> ) in mc-PERC cells at 50°C and                                                                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 95°C; Voc and Isc mode56                                                                                                                                                                                                                                                                                  |

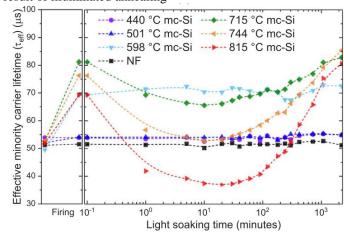

| Figure 25 - Absolute change in effective minority carrier lifetime of mc-Si samples fired at various                                                                                                                                                                                                      |

| temperatures as the result of illuminated annealing                                                                                                                                                                                                                                                       |

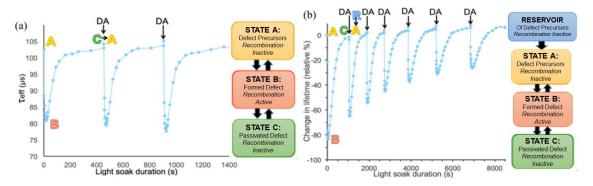

| Figure 26 – Left: BO-LID dark anneal and accelerated light soaking cycles with three state model,                                                                                                                                                                                                         |

| observed in Cz-Si. Right: LeTID in mc-si dark anneal and accelerated light soaking cycles with state model including reservoir                                                                                                                                                                            |

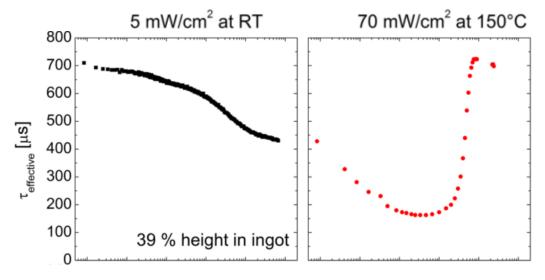

| Figure 27 – Sequential lifetime degradation curves in gettered and fired wafers from 39% height in the ingot. The BO-LID and the LeTID contributions to the total degradation are shown on the left and the right side, respectively                                                                      |

|                                                                                                                                                                                                                                                                                                           |

| Figure 28 - purification route for carbothermic and magnesiumthermic silicon for this study                                                                                                                                                                                                               |

| Figure 29 - Process flow diagram investigating the effects of different Firing Furnace Conditions on                                                                                                                                                                                                      |

| LeTID. Wafers was separated in eight groups.                                                                                                                                                                                                                                                              |

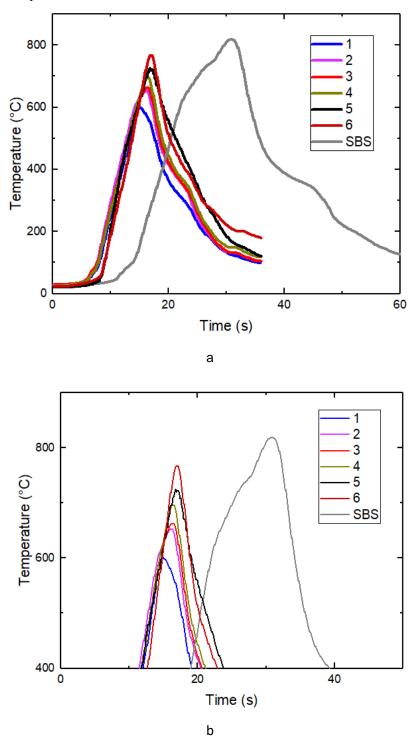

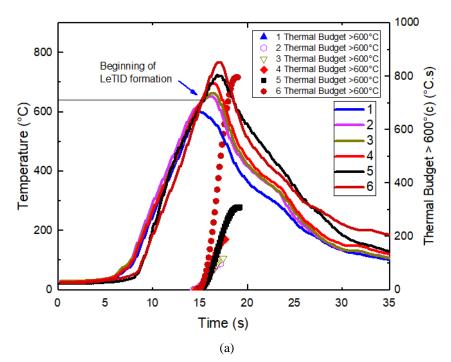

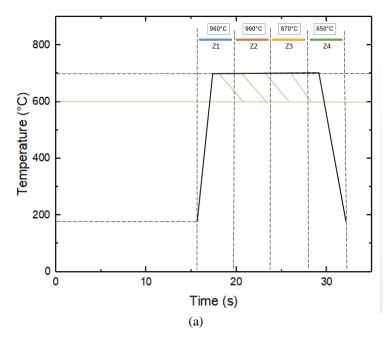

| Figure 30 – (a) Firing temperatures profiles resulted for the seven groups of wafers that went through                                                                                                                                                                                                    |

| firing. (b) Peak temperature zoom in                                                                                                                                                                                                                                                                      |

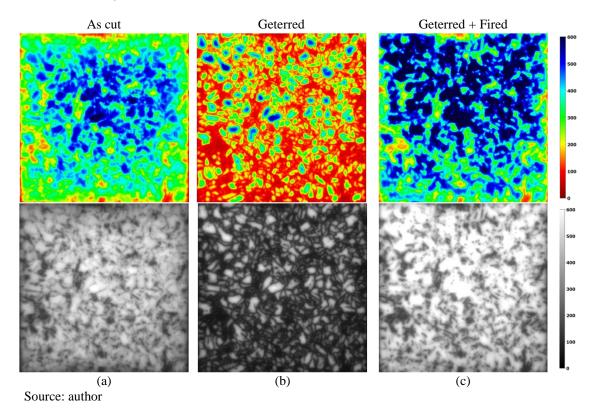

| Figure 31 - PL images of as-cut, gettered and gettered + fired wafers with colored and gray lifetime scales                                                                                                                                                                                               |

| from 0-600μs                                                                                                                                                                                                                                                                                              |

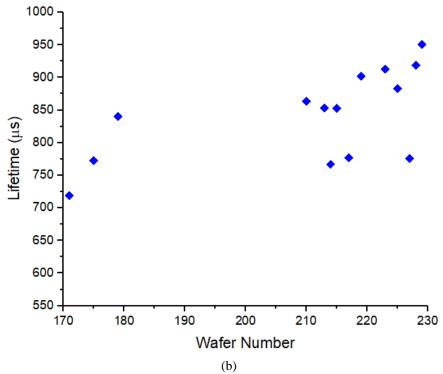

| Figure 32 – Average measured lifetimes with the PL equipment with calibrated by QssPC in as-cut,                                                                                                                                                                                                          |

| gettered and gettered + fired wafers. Colored scale PL images shows a selected wafer                                                                                                                                                                                                                      |

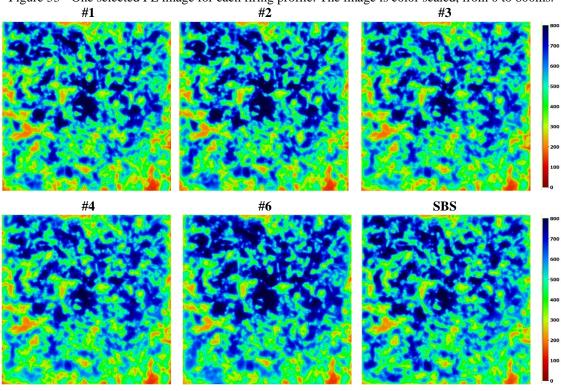

| Figure 33 - One selected PL image for each firing profile. The image is color scaled, from 0 to 800ms75                                                                                                                                                                                                   |

| Figure 34 – Average lifetime measured with the PL equipment with calibrated by QssPC for each wafer                                                                                                                                                                                                       |

| and according to the firing profile. Colored scale PL images shows a selected wafer                                                                                                                                                                                                                       |

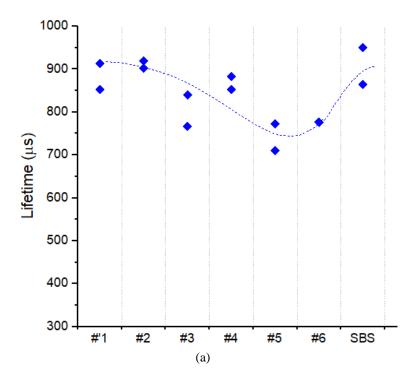

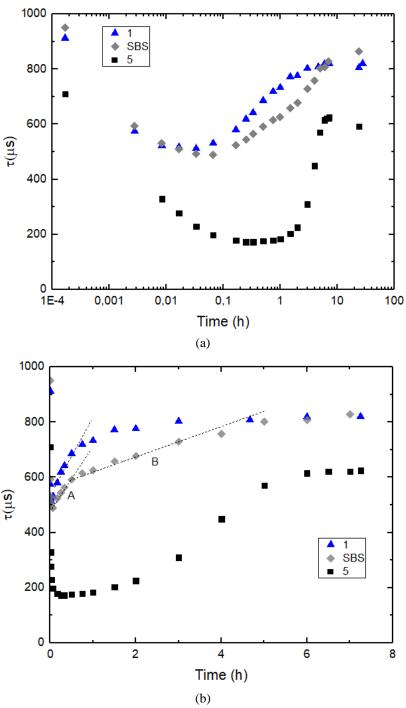

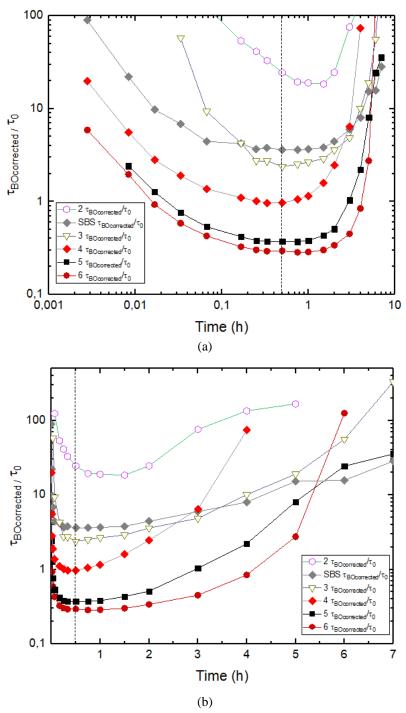

| Figure 35 – (a) Measured lifetimes for the firing profiles from #1 to #6 and SBS. A blue dash line, serving                                                                                                                                                                                               |

| as a guide for the eye; (b) QssPC lifetime measurements after a 20 minutes dark annealing related                                                                                                                                                                                                         |

| with increasing wafer number                                                                                                                                                                                                                                                                              |

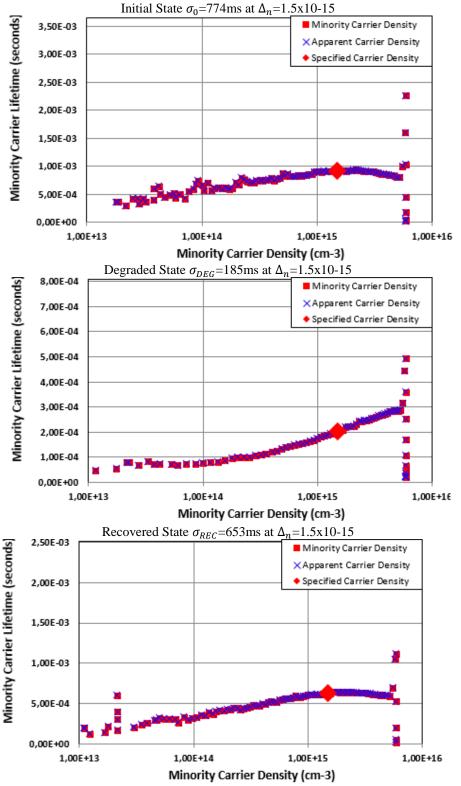

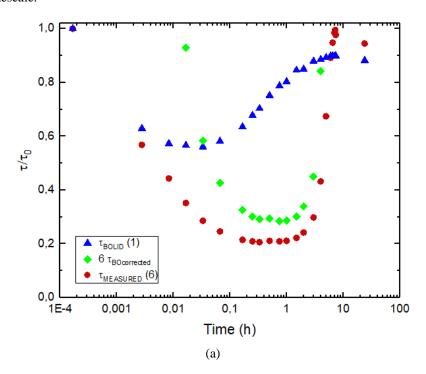

| Figure $36 - a$ ) ASC and firing process #5 illuminated annealing curves at $150^{\circ}$ C, $80 \text{mW/cm}^2$ , logarithmic                                                                                                                                                                            |

| timescale; b) same as (a) but linear timescale                                                                                                                                                                                                                                                            |

| Figure 37 - Injection dependent lifetime curves, from a wafer from the firing profile #5 at different states                                                                                                                                                                                              |

| using Sinton lifetime tester WCT-120TS                                                                                                                                                                                                                                                                    |

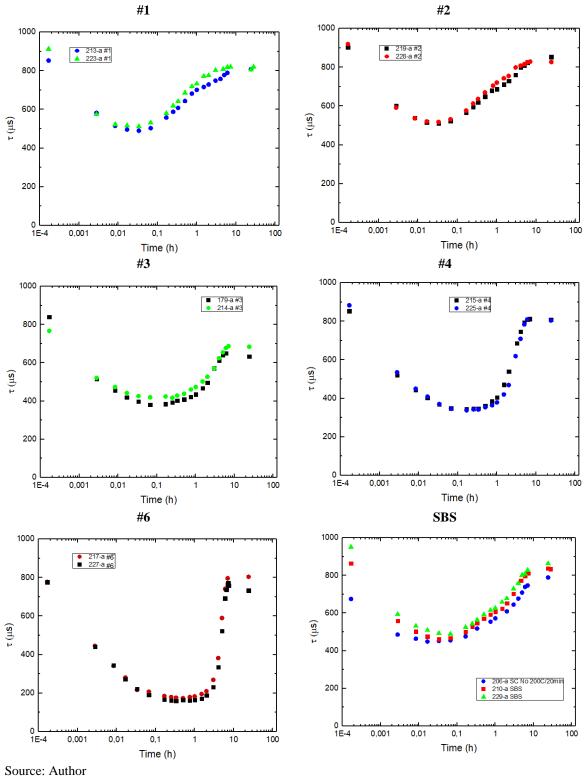

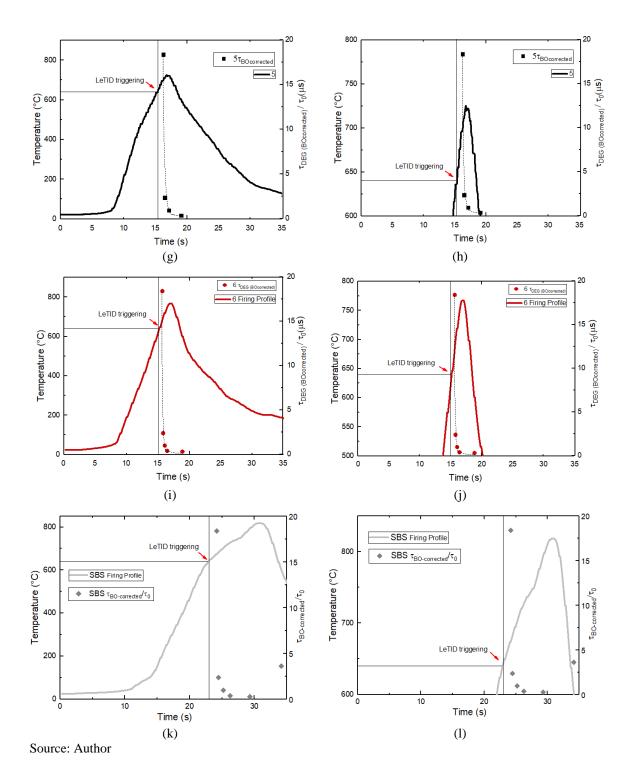

| Figure 38 - Degradation and recovery curves under illuminated annealing at 80 mW/cm² and 150°C on                                                                                                                                                                                                         |

| wafers fired with profiles #1, #2. #3. #4, #6 and SBS. Repeatability of the measurements is                                                                                                                                                                                                               |

| evaluated and wafer number is shown – "a" is the selected area of the wafer                                                                                                                                                                                                                               |

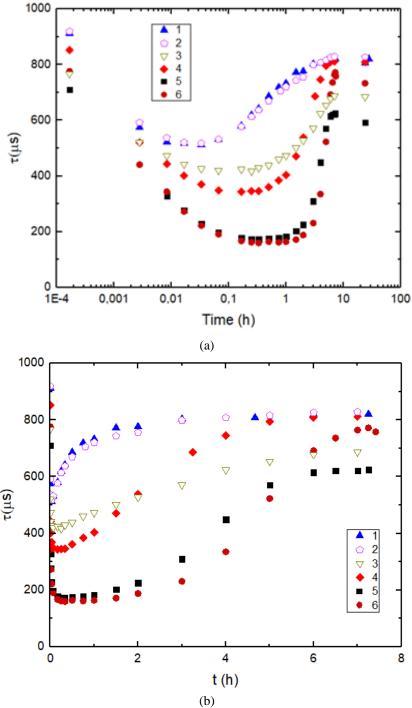

| Figure 39 – (a) Lower temperatures firing processes (#1, #2, #3, #4) and high temperature firing process (#6) illuminated annealing curves at 150°C, 80mW/cm², logarithmic timescale, compared with #5; (b) Lower temperatures firing processes (#1, #2, #3, #4) and high temperature firing process (#6) |

| illuminated annealing curves at 150°C, 80mW/cm², linear timescale, compared with #585                                                                                                                                                                                                                     |

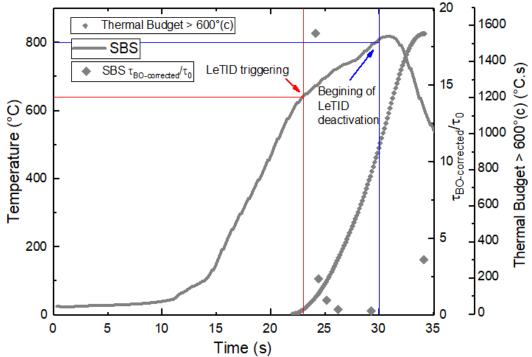

| Figure 40 - (a) Slow Belt Speed illuminated annealing curve at 150°C, 80mW/cm², logarithmic timescale,                                                                                                                                                                                                    |

| compared with #1 and #5; (b) Same as (a), but linear timescale; letters "A" and "B" indicates two                                                                                                                                                                                                         |

| different recovery rates in the SBS curve.                                                                                                                                                                                                                                                                |

| Figure 41 - (a) Normalized τ/τ0 SBS, #1, ASC and #6 illuminated annealing curves at 150°C, 80mw/m²;                                                                                                                                                                                                       |

| SBS; (b) same as (a) but linear timescale.                                                                                                                                                                                                                                                                |

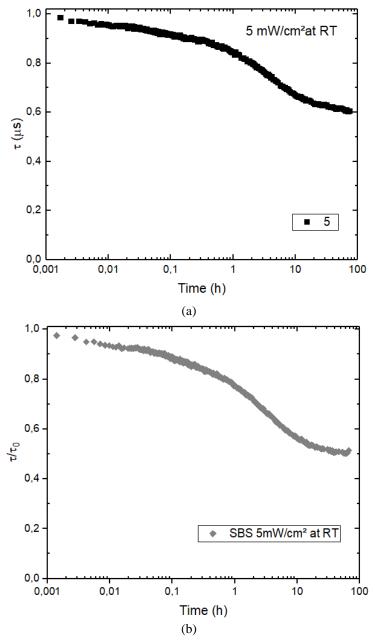

| Figure 42 - Low light intensity (5 mW/cm²) illuminated annealing curve at room temperature for 72 hours for BO-LID performed on a #5 sample (a) and on a SBS sample (b); the lifetime was approximately 60% and 51% of initial lifetime after 72 hours, respectively                                      |

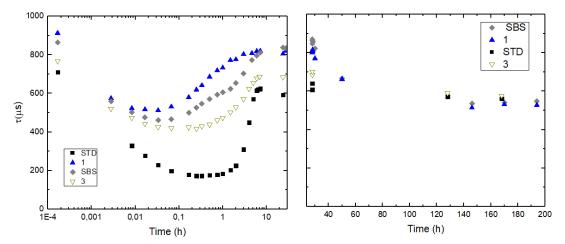

| Figure 43 – Lifetime stability in 200 hours measurements in samples from SBS, #1, #5 and #3. In the first                                                                                                                                                                                                 |

| 24 hours, samples are under illuminated annealing at 150°C, 80mw/m². After 24 hours, the samples                                                                                                                                                                                                          |

| were subjected to the same illumination of 80mW.cm <sup>-2</sup> , but at room temperature92                                                                                                                                                                                                              |

| Figure 44 – Lifetime stability in 1000 hours measurements in samples from SBS and #6. In the first 24 hours, samples are under illuminated annealing at 150°C, 80mw/m². After 24 hours, the samples                                                                                                       |

| were subjected to the same illumination of 80mW.cm-2, but at room temperature93                                                                                                                                                                                                                           |

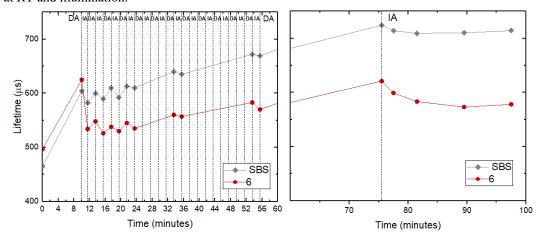

| Figure 45 – Lifetime evolution after dark annealing (DA - 150°C) and illuminated annealing (IA – 150°C,                                                                                                                                                                                                   |

| 3.5 suns). SBS and #5 samples previously went through 24 hours at illuminated annealing and 1000                                                                                                                                                                                                          |

| hours at RT and illumination94                                                                                                                                                                                                                                                                            |

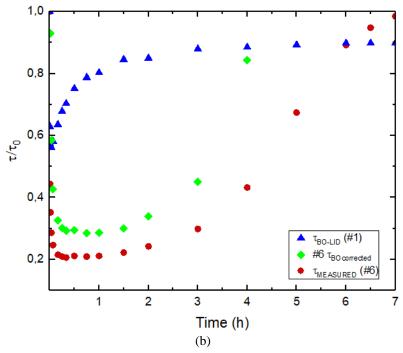

| Figure 46 – (a) Normalized curves for <b>τBOLID</b> considered as normalized #1 curve values (BOLID                                                                                                                                                                                                       |

| representative); <b>tmeasured</b> as #6 normalized curve values; and corresponding calculated #6                                                                                                                                                                                                          |

| <b>τBOcorrected</b> (considered LeTID representative) at 150°C, 80mw/m² illuminated annealing; (b) same as (a) but linear timescale95 |

|---------------------------------------------------------------------------------------------------------------------------------------|

| Figure 47 – (a) Normalized curves for calculated $\tau BO corrected$ for the groups #2, #3, #4, #5, #6 and                            |

| SBS at 150°C, 80mw/m² illuminated annealing; maximum <b>TBOcorrected</b> degradation occurred at                                      |

| around 30 minutes for all presented groups; #5 and #6 minimum <b>TBOcorrected</b> were 0,4 and 0,3;                                   |

| #4 minimum <b>TBOcorrected</b> were 1; #2 and SBS minimum <b>TBOcorrected</b> were 2 and 4; (b)                                       |

|                                                                                                                                       |

| same as (a) but linear timescale.                                                                                                     |

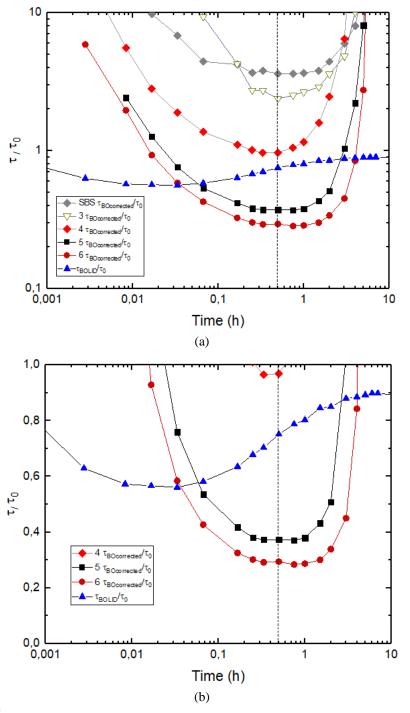

| Figure 48 – (a) Normalized curves for calculated <b>TBOcorrected</b> for the groups #2, #3, #4, #5, #6 and                            |

| SBS at 150°C, 80mw/m <sup>2</sup> illuminated annealing compared with normalized <b>τBOLID</b> ; (b) same as (a)                      |

| but with a normalized scale from 0 to 1                                                                                               |

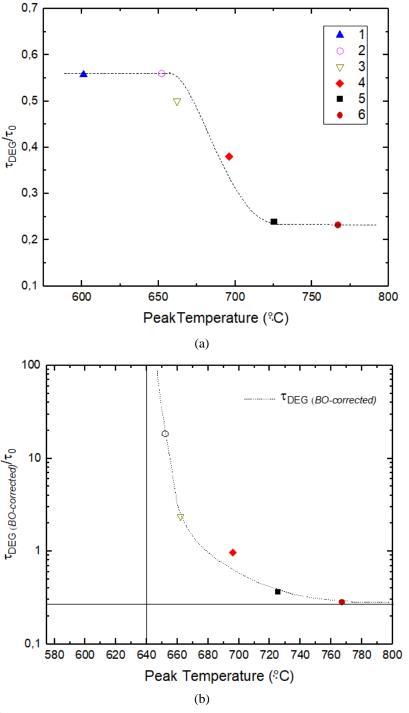

| Figure 49 – (a) Normalized maximum degradation $\tau DEG(measured)$ under illuminated annealing for                                   |

| each group of samples related with peak temperature in firing process b) Normalized maximum                                           |

| degradation $\tau DEG$ ( $BO - CORRECTED$ ) for each group of samples under illuminated annealing                                     |

| related with peak temperature in firing process                                                                                       |

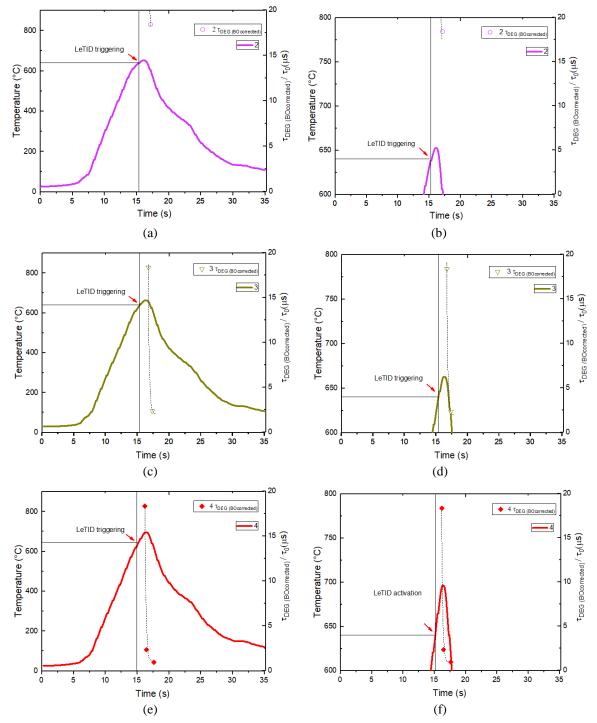

| Figure 50 – Firing profiles from #1 to #6. Beginning of LeTID defects formation is signed with the blue                               |

| arrow. The triggering temperature of 640°C is considered                                                                              |

| Figure 51 – (a) Firing profiles from #1 to #6. Beginning of LeTID defects formation is signed with the                                |

| blue arrow. The triggering temperature of 640°C is considered103                                                                      |

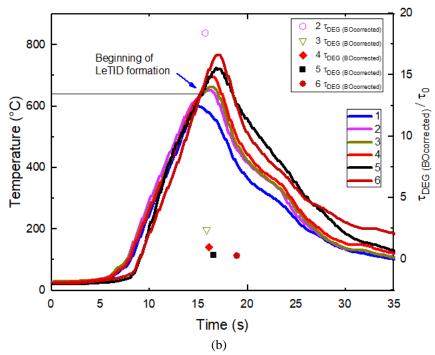

| Figure 52 – (a) Thermal budget for temperatures above 600°C for firing profiles from 1# to #6, the time                               |

| scale is the time when temperature is higher then 600°C; (b) same as (a), including SBS profile105                                    |

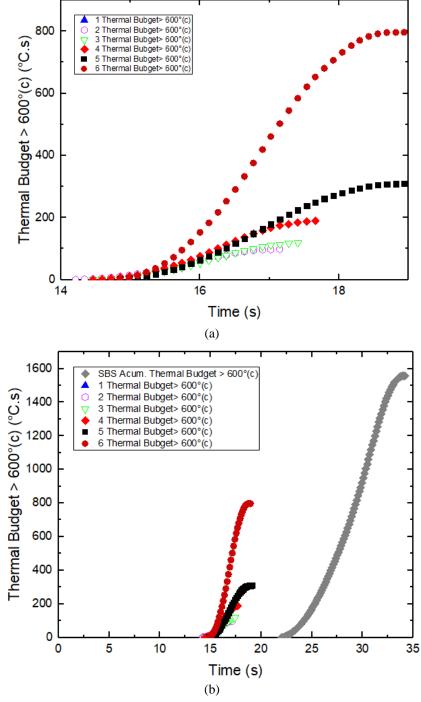

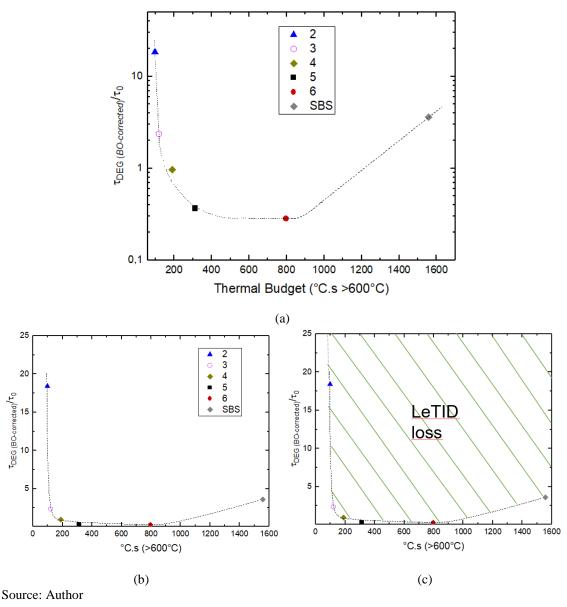

| Figure 53 – (a) Normalized maximum degradation $\tau DEG$ (BO – CORRECTED) for each group of                                          |

| samples under illuminated annealing related with the calculated thermal budget in firing processes                                    |

| above 500°C; (b) Same as (a) but for thermal budget above 600°C; (c) same as (b) but linear scales;                                   |

| (d) same as (c) with a hatched area indicating the loss that the LeTID defect introduces in the                                       |

| material in a firing process with increased thermal budget                                                                            |

| Figure 54 - Firing profiles from #2 to #6 related with the maximum normalized BO-corrected lifetime                                   |

| degradation, plotted in time. In this proposed Model A is considered that the thermal budget above                                    |

| 600°C is responsible for the increased formation of the defect and that the triggering temperature of                                 |

| the LeTID is fixed at 640°C                                                                                                           |

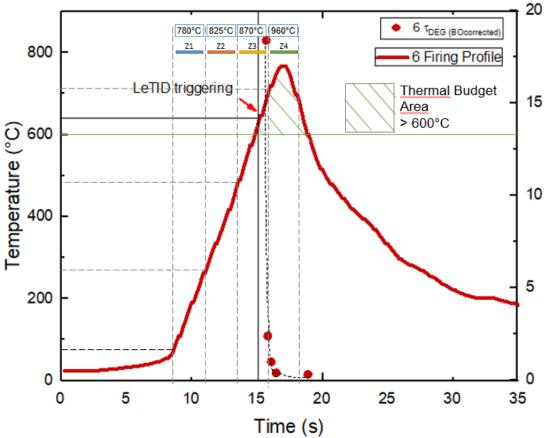

| Figure 55 –Model A for the formation of the LeTID inside the firing furnace. Firing profile #6 is related                             |

| with the maximum normalized BO-corrected lifetime degradation. The LeTID trigerring point is at                                       |

| fixed 640°C, the thermal budget above 600°C is signed with the hatched area and the firing zones as                                   |

| · · · · · · · · · · · · · · · · · · ·                                                                                                 |

| Z1, Z2, Z3 and Z4 are indicated with different colors and different set temperatures                                                  |

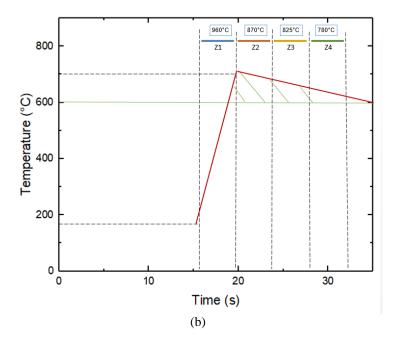

| Figure 56 - Model B for the formation of LeTID defects inside the firing furnace fro profiles #2, #3, #4,                             |

| #5, #6 and SBS. Triggering temperature related to a thermal budget above 600°C of 50°C.s114                                           |

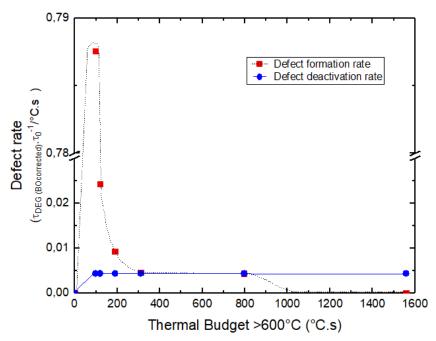

| Figure 57 – Calculated rate of defect formation, considered represented by the difference between                                     |

| maximum normalized BOcorrected lifetime degradations under illuminated annealing for each                                             |

| profile divided by the difference between thermal budgets above 600°C, using data from Table 9.                                       |

| Rate of emptying of LeTID defects reservoir is considered equal to the rate between #5 and SBS.                                       |

|                                                                                                                                       |

| Figure 58 – Model 1 for the emptying of the LeTID defects reservoir inside the firing furnace, considered                             |

| as a function of the thermal budget above 600°C119                                                                                    |

| Figure 59 – Model 2 for the emptying of the LeTID defects reservoir inside the firing furnace, considered                             |

| as begging after the cooling ramp pass through the LeTID triggering temperature121                                                    |

| Figure 60 – Simulated firing profiles according to the applicability of model 1 (a) or model 2 (b). As the                            |

| zones of the firing furnace are fixed, to reach the proposed parameters for the firing profile, the                                   |

| speed of the belt is close to that of the SBS profile, of 260 cm.min <sup>-1</sup> . Set temperatures for each zone                   |

| of furnace are proposed values. The real repercussion of these temperatures in the profile are not                                    |

| regarded                                                                                                                              |

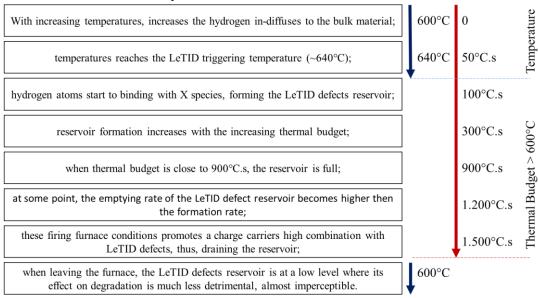

| Figure 61 – Summary for the overall proposed LeTID defect mechanism for formation and emptying                                        |

| reservoir for the studied SBS sample                                                                                                  |

| •                                                                                                                                     |

# **SUMMARY**

| 1 INTRODUCTION                                                             | 1  |

|----------------------------------------------------------------------------|----|

| 1.1 Objectives                                                             | 11 |

| 2 BIBLIOGRAPHIC REVIEW                                                     | 12 |

| 2.1 From silica to solar modules                                           | 12 |

| 2.1.1 From Quartz to Metallurgical grade Silicon                           | 12 |

| 2.1.2 From Metallurgical to Solar Grade Silicon                            | 16 |

| 2.1.2.1 Silicon purification routes                                        | 16 |

| 2.1.2.1 Ingot production                                                   | 19 |

| 2.1.3 From Ingot to Modules                                                | 22 |

| 2.2 Photovoltaic Basics, Fundamentals and Solar Cell Structures            | 26 |

| 2.2.1 Photovoltaic effect                                                  | 26 |

| 2.2.2 Solar cell concept                                                   | 26 |

| 2.2.3 Charge carrier lifetime                                              | 27 |

| 2.2.4 Solar cells designs                                                  | 30 |

| 2.3 Impurities, characterization of c-Si and recombination sources         | 33 |

| 2.3.1 Impurities effects on c-Si solar cell performance                    | 33 |

| 2.3.2 Characterization of solar grade Silicon                              | 35 |

| 2.3.3 Characterization of impurities in c-Si ingots                        | 40 |

| 2.3.4 Characterization techniques for c-Si ingots and wafers               | 41 |

| 2.3.4.1 QssPC Lifetime measurements                                        | 42 |

| 2.3.4.2 Photoluminescence Images                                           | 43 |

| 2.3.4.3 Series resistance measurements with PL                             | 44 |

| 2.3.4.4 Lifetime measurements with PL                                      | 44 |

| 2.3.4.5 PL Calibration with QssPC                                          | 45 |

| 2.3.4.6 PL characterization of mc-Si Ingots and Wafers                     | 46 |

| 2.3.5 Recombination Sources on mc-Si                                       | 48 |

| 2.4 Light Induced Degradation on silicon                                   | 53 |

| 2.4.1 BO-LID in P-type Cz-Si                                               | 54 |

| 2.4.2 BO-LID and LeTID in P-type mc-Si                                     | 55 |

| 3 MATERIALS AND METHODS                                                    | 61 |

| 3.1 ICP-OES impurities measurements of Brazilian quartz, MG-Si and UMG-Si. | 61 |

| 3.2 Characterization of commercially available mc-Si wafers                | 62 |

| 3.2.1 Investigations on LeTID                                              | 63 |

| 4 RESULTS AND DISCUSSION                                                   | 67 |

| 4.1 ICP-OES impurities measurements of Brazilian quartz, MG-Si and UMG-Si              | 67       |

|----------------------------------------------------------------------------------------|----------|

| 4.2 Characterization of commercially available mc-Si wafers                            | 70       |

| 4.2.1 Investigations on LeTID                                                          | 73       |

| 4.2.1.1 PL images and QssPC measurements for each Firing Profile                       | 74       |

| 4.2.1.2 Lifetime evaluation under illuminated annealing for different firing p         | orofiles |

|                                                                                        | 78       |

| 4.2.1.3 A method proposed for LeTID and BO-LID separation                              | 94       |

| 4.2.1.4 The Firing Profile curves investigation on LeTID formation/suppress mechanisms |          |

| 5 CONCLUSION                                                                           | 128      |

| REFERENCES                                                                             | 130      |

#### 1 INTRODUCTION

The continued cost reductions and the environmental benefits, aligned with global concerns about climate change, have made solar photovoltaic technology (PV) the most installed source of energy in the power sector worldwide [1]. The increasing investments in renewable energy are tracking more and more the global full potential of PV.

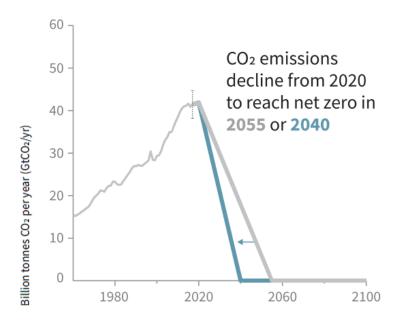

According to the special report on global warming impacts of 1.5°C from the Intergovernmental Panel on Climate Change (IPCC) [2], limiting global warming to 1.5°C would require rapid and far transitions in land, energy, industry, buildings, transport, and cities. The global net human-caused emissions of carbon dioxide needs to reduce to about 45% from 2010 levels by 2030, reaching 'net zero' around 2050. Figure 1 shows a stylized pathway from 2019 CO<sub>2</sub> emissions to a net zero emission in 2055 or 2040. These emission reduction paths would result in a higher probability of limiting warming to 1.5°C.

Figure 1 - A simple climate model to a pathway in which net  $CO_2$  emissions (grey line) decline in a straight line from 2020 to reach net zero in 2055. The blue line is a response to a faster  $CO_2$  emissions reduction, reaching net zero in 2040, reducing cumulative  $CO_2$  emissions. The purple line shows the response to net  $CO_2$  emissions declining to zero in 2055 with net non- $CO_2$  forcing remaining constant after 2030 [2].

Source: IPCC [2]

The IPCC report on the impacts of global warming of 1.5°C [2] is part of the task to consolidate the Paris Agreement [3], which entered into force in November of 2016. The report forecasts 70–85% renewables for electricity supply in 2050. Any remaining emissions would need to be balanced by removing CO<sub>2</sub> from the air. According to C. Breyer et al. [4], a very deep decarbonzation towards 100% renewables in the power sector between 2040 and 2050 is possible, taking technical, economic, and societal constraints into account, and is the resulting least cost energy system with the greatest societal welfare, thus, providing energy system resilience. By using renewables, huge amounts of currently required subsidies for fossil fuels and nuclear risk are phased out. Carbon dioxide level is increasing in 2019, though. In May 2019, is expected to peak around 415 parts per million [5], mainly due to the persistent worldwide increased use of fossil fuels.

The power sector has the most potential to ensure the achievement of the Paris Agreement, since other sources of greenhouse gas emissions are even more difficult to phase out, such as from agriculture, cattle farming, industries, and parts of the transportation sector [4]. Electricity is evolving to be the basis of the energy systems in this century, due to high technical efficiency, comparable low cost, and the availability of respective power-to-heat, power-to-water, power to-hydrocarbons and a directly or indirectly electrified transport sector. Hydrogen production via solar photovoltaic-electrolysis is a simple and feasible technology [6] and a common view for the decarbonization of the transport sector [7], [8], [9].

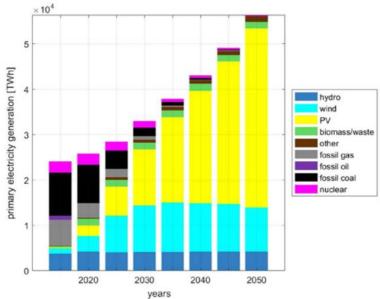

In C. Breyer et al. [4] energy system transition model, solar PV and batteries will evolve as the most important power technologies globally, complemented by wind energy and mainly existing hydropower as shown in Figure 2. In addition, gas turbines are the most valuable and flexible balancing technology on a time scale of days to months and will gradually evolve from fossil to renewable gas. The cumulative PV capacity will hit 19 TW by 2050, representing 40% of world electricity production. About 30% of this capacity will be installed in homes or commercial rooftops, while the remaining 13.3 TW will come from large-scale systems, mainly single-axis tracking PV power plants on the ground, which will represent 0.3% of the earth's surface. About 50 TWh of storage capacity will handle the variable power generation. The continuous cost decline of solar PV and battery systems combined with excellently distributed solar resources and high modularity are main factors for the PV dominance.

Figure 2 - Evolutionary development of the electricity generation for the global energy transition from 2015 to 2050. The model is based on hourly resolution for an entire year, the world structured in 145 regions, high spatial resolution of the input RE resource data, and transition steps of 5-year Period.

Source: C. Breyer et al. [4]

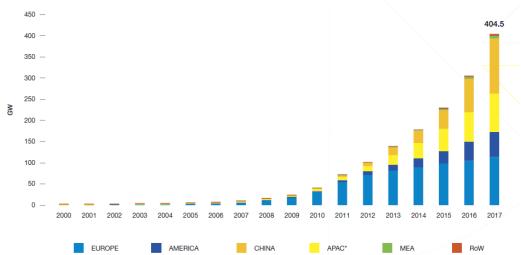

Photovoltaic solar energy has become the fastest growing power generation source in the world [1]. Figure 3 shows the growing of global total solar PV installed capacity from 2000 to 2017. In 2017, 98 GW were added to photovoltaic solar power generation capacity, thus surpassing the new installed capacity of new fossil fuels and nuclear combined. Once led by Germany, China promoted the rapid growing of the PV market. India and United States stand out as the next largest markets until 2022.

Figure 3 - Evolution of global total solar PV installed capacity 2000-2017

\* APAC - Pacific Asia and Central Asia Excl. China

Source: Inrtersolar Europe

According to Intersolar Europe [1], in the reference scenario, between 2018 and 2022 is expected the addition of approximately 400 GW of new photovoltaic capacity worldwide. Even in OPEC future scenario with greater participation of fossil fuels in the energy matrix, the growth in demand for the use of photovoltaic solar energy is well established. OPEC World Oil Outlook [10] estimates that, by 2040, the global use of renewables, mainly PV and wind, is projected to be five times higher compared to 2015.

The solar photovoltaic industry has become a global giant, with an increasing production rate that, in 2018, was 100 GW per year. Further opportunities are expected in research, manufacturing, services and the corresponding development of energy systems, electric mobility and energy storage.

Accordingly to J. Jean [11], it is possible to achieve 25 TWp in photovoltaic capacity until 2050 without major material constraints. The total amount of key elements required to satisfy 100% of global electricity demand with today's wafer-based PV technology is up to 60 Mt of silicon. It would be enough to achieve just over the target of 69% of the global electricity generation proposed by C. Breyer [4]. Still, PV production technologies are rapidly becoming even more efficient, requiring less amount of feedstock per Wp of photovoltaic capacity. The recycling of silicon in silicon photovoltaic modules should also be further relevant within the passing years [12].

According to the Brazilian Ministry of Mines and Energy (MME) [13], Brazil has the largest know reserves of silicon in the world with approximately 78 Mt of quartz. Therefore, there is a huge potential in the exploitation of this resource with clear benefits to the local economy and global environment. To this end, a national technology for purifying and manufacturing silicon wafers for an increasingly competitive and efficient photovoltaic industry must be fully developed. Quartz is currently produced and exported by Brazil in the metallurgical grade. The transformation of this metallurgical grade silicon into solar and/or electronic grade requires a purification process that would add high value to the mineral [14].

According to Brazilian national electrical system operator (ONS)<sup>1</sup>, 71.8% of the energy generation in the National Interconnected System (SIN) in 2018 was hydroelectric, 16.7% thermal fossil and biomass, 8.3% wind, 2.7% nuclear and 0.5 % solar. The installed capacity of photovoltaic solar energy in December 2018 was 1,78

-

<sup>&</sup>lt;sup>1</sup> www.ons.org.br

GW. Still, the potential positive impacts of the growth of PV generation in the national energy mix have not yet been fully studied and discussed.

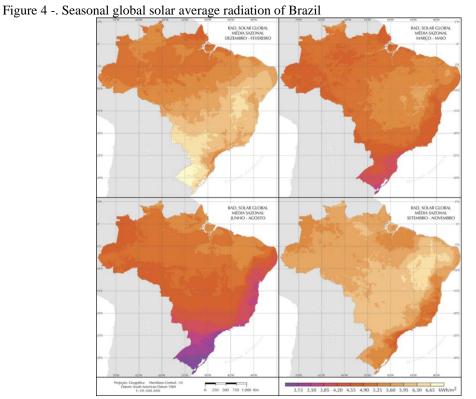

The annual electricity peak demand in Brazil has been reported for the all regions in accordance with the thermal discomfort caused by heat waves during the afternoons [15]. The increased maximum instantaneous demand and a water scarcity scenario and power loss by depletion of reservoirs at the end of the dry seasons have required an increase in the consumption of fossil fuel sources for thermoelectric generation with high operating costs. An analysis on the demand side taking into account the solar supply shows that the implementation of photovoltaic solar energy in the southern region would cause greater impact in reducing the annual daytime peak demand among all regions. In December, January and February (Figure 4), the solar radiation levels in the south are the largest in Brazil and, in addition, exactly in this period, the region imports electricity from Southeast and Midwest regions. A large quantity of solar photovoltaic generation in the southern region will have a positive impact for the Brazilian electricity system. PV solar energy therefore has a reliable intermittence; it is a highly dispatchable source of energy if considering the characteristics of the electric energy demand in Brazil [15] and in several other countries [4].

Soure: E. Pereira et al. [16]

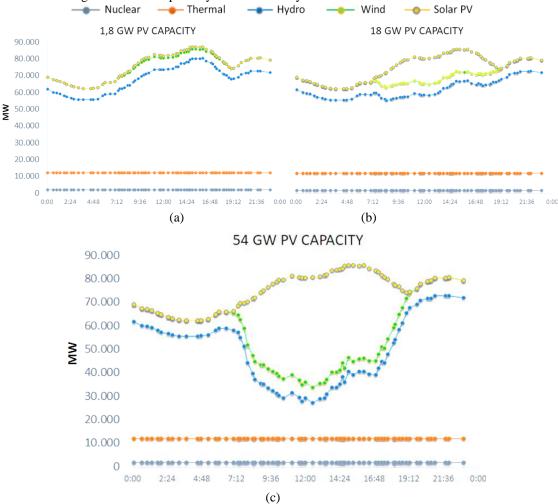

In a changing paradigm of Brazilian electricity generation, which once used the hydro energy as the priority energy source and should then use it as a backup source [17], solar and wind power generation capacity should be dimensioned to act in synergy with the other renewable sources ensuring the progressive reduction in fossil fuels consumption and water supply. In Figure 5, one daytime generation curve of a summer day, of February 2019, is presented, including renewable generation curves of hydro, wind and solar sources, fossil thermal and nuclear. In Figure 5(a) is shown the real daytime generation curves, with a peak demand at around 3:40 pm (summer time). In Figure 5(b), the hydro generation is subtracted from the actual solar PV generation multiplied by a factor of ten. In Figure 5(c), the hydro generation is subtracted from the actual solar PV generation multiplied by a factor of thirty. It is possible to observe the impact that solar generation can provide for the national electricity system. With an installed capacity increase from 1.8 GW to 18 GW, PV become a "shield" for the daytime peak, and further to 54 GW, solar energy will mainly positively affect hydro generation, saving water from reservoirs during the day, improving the management of water supply.

Figure 5 - Daytime generation curve of a summer day, of February 2019, including renewable generation curves of hydro, wind and solar sources, fossil thermal and nuclear. a) Real daytime generation curves; (b) daytime generation curves with the hydro generation subtracted by the actual solar PV generation multiplied by a factor of ten (c) daytime generation curves with the hydro generation subtracted by the actual solar PV generation multiplied by a factor of thirty

Source: D. Knob, P. J. Knob and H. G. Riella [18]

According to the ONS<sup>2</sup>, there were, in February 2019, 111 GW of installed hydro capacity, 30 GW of wind and 1.8 GW of solar PV. Peak demands on summer days are the highest of the year [15], at around 3:00 p.m. (summer time), where instant demand is close to 90 GW. With 0.5% of the energy generated in the day, solar photovoltaic generated 1.5% of the instant demand at peak time. Therefore, the highest load factor among the renewable sources in the peak time of the day, at 3:43 pm, is the solar photovoltaic, with approximately 80%, followed by hydropower, with 60% and wind with 20%.

<sup>2</sup> www.ons.org.br

According to C. Breyer et al. [4], photovoltaic solar energy can generate 63% of the demand for electric energy in Brazil in 2050. This corresponds to about 400GW of installed capacity, considering a conservative average annual global solar radiation in Brazil equivalent to 5.00 kW.m<sup>-2</sup>. In PDE2027 plan [19], the Brazilian Energy Research Office (EPE) estimates that solar PV will reach a cumulative installed capacity of 21GW by 2027. In the report Distributed Energy Resources 2050, EPE and MME estimates 101GW of capacity from micro and mini distributed generation in 2050 in Brazil for the upper scenario. PV generation above 50% in the electricity mix by 2050 has not yet been stipulated comprehensively by the MME. Clearly, there is a potential for the solar energy in the Brazilian electricity system to be the largest share among all other forms of energy. All of this requires more ambitious planning from the Brazilian MME to ensure a fossil-free electricity sector by 2050.

In terms of material type, crystalline silicon (c-Si) PV modules accounted for 95% of the global annual PV market in 2017 [20]. There are two main categories: monocrystalline (mono-Si) and multicrystalline (multi-Si) [21]. Fine films accounted in 2010 for 13% of global production of PV modules [22] and for 4.5% in 2017 [20]. There are three main groups: amorphous silicon (a-Si) and microamorph (a-Si / μc-Si), Cadmium-Tellurium (CdTe), and Copper-Indium-Selenide (CIS) and Copper-Indium-Galium-Selenide (CIGS) [21]. New PV concepts aim to obtain ultra-efficient solar cells through advanced materials and/or new conversion concepts and processes such as advanced thin films and organic cells, PV Concentrator (CPV).

The most commonly used material in photovoltaic cells is multicrystalline silicon (multi-Si) [23]. Since 2005, multi-Si maintained relatively constant market shares [24] until 2009 [25], competing directly with mono-Si. From 2009 to 2016 it increased its share, but the trend stopped in 2017 [20], when mono technology started to grow relatively after manufacturers began switching towards lower processing cost and higher yield diamond-wafer technology while processing equipment suppliers began offering tools for low-cost high-efficiency cell designs [1].

The silicon crystallization market is dependent on the price of the raw material and the efficiency gap between the multi and mono crystalline silicon. Low prices favor the production of highly efficient monocrystalline silicon. However, new solar cell technologies continue to reduce the efficiency gap between the two. However, future cell concepts with increasing efficiencies favor the use of monocrystalline silicon. Nearly all mono cell lines in 2018 were capable of producing Passivated Emitter rear

Contact (PERC). The technology brings 0.5-1 percentage efficiency improvements with little more cost [1]. In the case of multicrystalline silicon cells, which is the target of the interests of this thesis, the LeTID (Light and elevated Temperature-Induced Degradation) is the specific object of investigations. Its causes remain unknown [26]. Understand and contain the LeTID is seen as essential, as is most evident and cause greater loss of efficiency in the PERC solar cell structure compared to its predecessor in the industry, the aluminum back surface field (Al-BSF). Avoiding LeTID for the p-type mc-Si is crucial for its survival in the future market for increasingly efficient solar cells.

The impact of impurities on solar cell and module performance increases for advanced cell architectures even for n-type substrates [27]. If the cell efficiency cannot be maintained, then the advantage of the feedstock low cost is lost due to quality degradation. Thus, is observed a raise in the demand for high quality quartz, specifically low in boron and phosphorus.

For photovoltaic solar industry, impurities concentrations for solar grade silicon (SoG-Si) are well below the concentrations of impurities found in metallurgical grade silicon (MG-Si). Therefore, purification processes of silicon metallurgical grade to ultra-metallurgical grade silicon (UMG) are necessary [28]. However, impurities for solar grade silicon may be at higher levels than the impurity levels required for electronic grade silicon (EG-Si). From the PV industry, the production of a less expensive and less pure solar grade silicon, adapted for the photovoltaic market, has emerged. For this end, the metallurgical route purification of silicon with less strict control of impurities enables the processing of solar cells with a satisfactory photovoltaic conversion efficiency. In addition, there are more metals impurities in multicrystalline Silicon compared with single crystal Silicon due to less pure coating and crucible materials, even with significant improvement by the materials suppliers. Still, the manufacture of multicrystalline silicon of high performance (HPMC-Si) is successfully done in the industry, and the object of investigations [29].

Typically, manufacturers of raw materials Solar Grade Silicon qualify their products by controlling contained chemical impurities. However, the electron activity of some impurities may be dependent on their chemical configuration or their physical distribution in the crystal (complexed with other impurities, dissolved in the matrix or agglomerated). These effects can be investigated by the electronic properties of the crystallized silicon and are therefore used as a measure of the quality of the raw material. Structural and electronic quality can be measured by optical inspection, lifetime, traps

density and by photoluminescence in silicon wafers [30]. The demands on quality control systems are growing in parallel with the PV market. Advanced characterization techniques play an important role in the offline characterization of samples at different stages of processing, which is indispensable for process optimization and material qualification.

The characterization and qualification of silicon wafers must take into account the main mechanisms of light-induced degradation in solar cells. The study on LeTID in multicrystalline silicon encompasses the understanding of steps subsequent to the manufacture of the wafers: gettering, passivation and firing or hydrogenation. The hydrogen contained in the passivation layers, despite deactivating various defects contained in multicrystalline silicon, can activate the LeTID defect, which will result in a loss of efficiency of the photovoltaic cell in the field that can reach 10% relative [31]. In partnership with the IFE of Norway, we have conducted a series of experiments to investigate the possible causes of LeTID, to understand the quality of the multicrystalline silicon used by the industry; the possible routes for deactivation of defects; and wafer characterization methods.

In Brazil, the promising photovoltaic market demand numerous initiatives that are being articulated to insert photovoltaic solar energy significantly in the country's energy mix. Keeping this in view, CCN of IPEN had the initiative in investigating the production of metallic silicon via magnesiothermal reduction and metallurgical route purification, qualified for the photovoltaic industry. This initiative requires a characterization of samples in different stages of production necessary for the validation of processes from quartz to wafer.

In this work, we perform an acid leaching in the material resulting from the magnesiothermal reduction, produced in IPEN, to form a MG-Si with relatively low impurities. The conditions of the acid leaching was taken from best results from the extensive work conducted by R. Ramos [32]. On more acid leaching step with HCl + HF in this resulting magnesiothermal reduced/acid leached material was proceed, using the conditions given in Ref. [33] aiming further purification of the MG-Si to a specific UMG-Si. In addition, the same HCl + HF acid leaching was performed in a commercially available Brazilian-made metallurgical grade silicon produced via carbothermal reduction. All samples impurities from each processing step, was measured by ICP-OES. The results was analyzed and compared to the state of art on literature [27]. We further conducted a study on BO-related LID and LeTID on mc-Si, in IFE, Norway. We used

neighboring HPMC-Si p-type wafers that were prepared and tested in different firing process conditions, i.e. different temperatures and furnace belt speeds. The effects of the different firing furnace conditions on subsequent LeTID was investigated in terms of defects activation and a corresponding lifetime degradation. An extensive investigation was taken on LeTID degradation and recovery mechanisms, seeking to eliminate or take more into account possible causes and solutions to suppress, partially suppress or overcame the defect. In addition, we have proposed a new method to separate BO-LID effects of LeTID during the characterization of the material, enabling to find and measure LeTID even where it was thought to be fully suppressed. The Tine Uberg Nærland et al. [34], [35], [36], Rune Søndenå et al. [37], [38], Tim Niewelt et al. [26] studies was the main references on LID to this thesis.

## 1.1 Objectives

Evaluation of silicon impurities after the reduction and purification processes and characterization of multicrystalline silicon wafers taking into account the main defect mechanisms such as LeTID.

# Specific objectives:

- Analyzes different routes for the production of multicrystalline silicon wafers from quartz to ultra-metallurgical grade silicon,.

- Evaluation of impurities of the Brazilian solar grade silicon production,

- Investigate LeTID by wafer characterization after applying different Firing Furnace Conditions in commercially available p-type multi-Si wafers.

- Investigate possible causes and solutions to suppress, partially suppress or overcame the LeTID defect and a method to separate BO-LID effects from LeTID.

- Investigate metrics and propose models for the LeTID defect formation and suppression.

#### 2 BIBLIOGRAPHIC REVIEW

#### 2.1 From silica to solar modules

Silicon has been the dominant material in the photovoltaic industry and this is the trend for the coming decade [20], [1]. It is an abundant material that enables the projected growth of the PV installed capacity even in the most challenging scenarios of complete replacement of fossil fuels [11] in ever-growing electric power sector. In this chapter, a review of the manufacture of photovoltaic modules based on crystalline silicon, mainly the multi-crystalline silicon (mc-Si) is presented. The processing steps for the production of silicon-based photovoltaic modules from quartz can be divided into: production of metallurgical grade metal silicon; refining of metallurgical grade silicon via chemical or metallurgical routes to produce silicon grade solar; crystallization; wafer manufacturing; solar cell manufacturing; manufacturing of modules.

This work focus the bibliographic review on multicrystalline silicon material, manufactured via directional solidification from UMG feedstock. Multicrystalline silicon has a simpler, cheaper and less energy-intensive production. However, its survival on the PV industry must depend on constant advances in the conversion efficiency of photovoltaic cells produced with this material. For this, the LeTID, that is the most detrimental degradation seen in mc-Si PERC cells under the operating conditions of its photovoltaic modules in the field, must be overcome. This chapter will introduce the manufacturing process steps, therefore, especially for the multi-Si production and the implications of impurities from the feedstock and the contaminations within the processes.

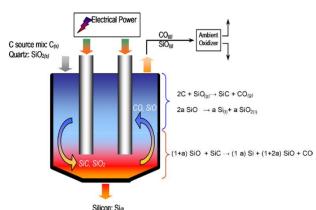

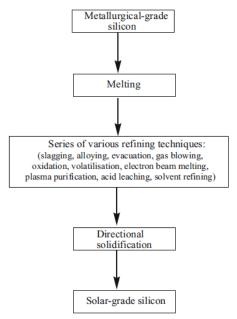

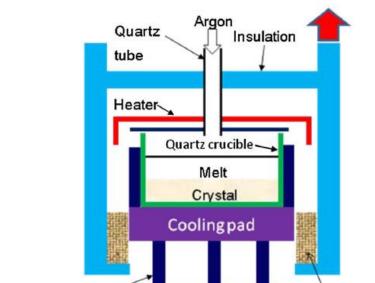

## 2.1.1 From Quartz to Metallurgical grade Silicon