André Mantini Eberle

| SERVIÇO DE PÓS-GRADUAÇÃO DO ICMC-USP |

|--------------------------------------|

| Data de Depósito:                    |

| Assinatura:                          |

#### **André Mantini Eberle**

Análise dos caminhos de execução de programas para a paralelização automática de códigos binários para a plataforma intel x86

Dissertação apresentada ao Instituto de Ciências Matemáticas e de Computação - ICMC-USP, como parte dos requisitos para obtenção do título de Mestre em Ciências - Ciências de Computação e Matemática Computacional. VERSÃO REVISADA

Área de Concentração: Ciências de Computação e Matemática Computacional

Orientador: Prof. Dr. Rodrigo Fernandes de Mello

USP – São Carlos Dezembro de 2015

# Ficha catalográfica elaborada pela Biblioteca Prof. Achille Bassi e Seção Técnica de Informática, ICMC/USP, com os dados fornecidos pelo(a) autor(a)

Eberle, André Mantini

E16a Análise dos caminhos de execução de programas para a paralelização automática de códigos binários para a plataforma intel x86 / André Mantini Eberle; orientador Rodrigo Fernandes de Mello . -- São Carlos, 2015.

70 p.

Dissertação (Mestrado - Programa de Pós-Graduação em Ciências de Computação e Matemática Computacional) -- Instituto de Ciências Matemáticas e de Computação, Universidade de São Paulo, 2015.

1. Paralelização automática. 2. Análise de dependências . 3. Código Binário. 4. Plataforma Intel x86. I., Rodrigo Fernandes de Mello, orient. II. Título.

#### **André Mantini Eberle**

Analysis of the execution paths of programs to perform automatic parallelization of binary codes on the platform intel x86

Master dissertation submitted to the Instituto de Ciências Matemáticas e de Computação - ICMC-USP, in partial fulfillment of the requirements for the degree of the Master Program in Computer Science and Computational Mathematics. FINAL VERSION

Concentration Area: Computer Science and Computational Mathematics

Advisor: Prof. Dr. Rodrigo Fernandes de Mello

USP – São Carlos December 2015

## Resumo

Aplicações têm tradicionalmente utilizado o paradigma de programação sequencial. Com a recente expansão da computação paralela, em particular os processadores multinúcleo e ambientes distribuídos, esse paradigma tornou-se um obstáculo para a utilização dos recursos disponíveis nesses sistemas, uma vez que a maior parte das aplicações tornam-se restrita à execução sobre um único núcleo de processamento. Nesse sentido, este trabalho de mestrado introduz uma abordagem para paralelizar programas sequenciais de forma automática e transparente, diretamente sobre o código-binário, de forma a melhor utilizar os recursos disponíveis em computadores multinúcleo. A abordagem consiste na desmontagem (disassembly) de aplicações Intel x86 e sua posterior tradução para uma linguagem intermediária. Em seguida, são produzidos grafos de fluxo e dependências, os quais são utilizados como base para o particionamento das aplicações em unidades paralelas. Por fim, a aplicação é remontada (assembly) e traduzida novamente para a arquitetura original. Essa abordagem permite a paralelização de aplicações sem a necessidade de esforço suplementar por parte de desenvolvedores e usuários.

**Palavras-chave:** paralelização automática, análise de dependências, código-binário, plataforma Intel x86.

## **Abstract**

Traditionally, computer programs have been developed using the sequential programming paradigm. With the advent of parallel computing systems, such as multi-core processors and distributed environments, the sequential paradigm became a barrier to the utilization of the available resources, since the program is restricted to a single processing unit. To address this issue, we introduce a transparent automatic parallelization methodology using a binary rewriter. The steps involved in our approach are: the disassembly of an *Intel x86* application, transforming it into an intermediary language; analysis of this intermediary code to obtain flow and dependency graphs; partitioning of the application into parallel units, using the obtained graphs and posterior reassembly of the application, writing it back to the original *Intel x86* architecture. By transforming the compiled application software, we aim at obtaining a program which can explore the parallel resources, with no extra effort required either from users or developers.

**Keywords:** automatic parallelization, dependency analysis, binary rewriter, binary code, Intel x86 platform.

# Lista de Figuras

| 1.1<br>1.2                             | Exemplo de código de máquina com dependências                                                                                                                                                                                                                                                   | 5<br>5                     |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6 | Dependência do tipo RAW.  Dependência do tipo WAR.  Dependência do tipo WAW.  Exemplo de bloco com entrada lateral (Adaptado de (HANK <i>et al.</i> , 1993)).  Exemplo de bloco com entrada lateral em um grafo de fluxo de execução.  Exemplo de super-bloco em um grafo de fluxo de execução. | 22<br>22<br>23<br>24<br>24 |

| 4.1                                    | Exemplo de grafo de fluxo de execução                                                                                                                                                                                                                                                           | 38                         |

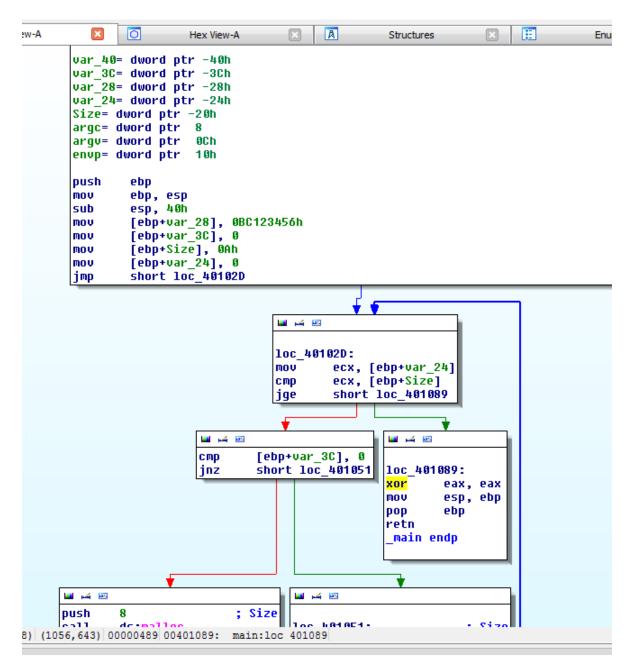

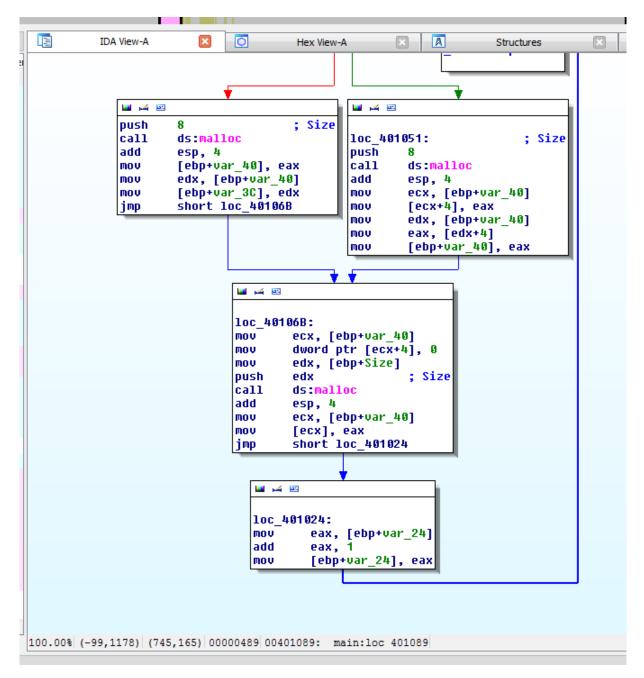

| 4.2<br>4.3                             | Exemplo de aplicação desmontada pela ferramenta <i>IDA Starter Edition</i> (Parte 1)                                                                                                                                                                                                            | 41<br>42                   |

| 4.4                                    | Exemplo de algoritmo em linguagem <i>C</i> para uma aplicação                                                                                                                                                                                                                                   | 43                         |

| 4.5                                    | Exemplo de instruções para a análise de dependências                                                                                                                                                                                                                                            | 44                         |

| 4.6                                    | Exemplo de expressões finais para a análise de dependências                                                                                                                                                                                                                                     | 44                         |

| 4.7                                    | Exemplo de bloco condicional                                                                                                                                                                                                                                                                    | 46                         |

| 4.8                                    | Exemplo de expressões para um bloco condicional                                                                                                                                                                                                                                                 | 46                         |

| 4.9                                    | Exemplo de laço de repetição.                                                                                                                                                                                                                                                                   | 47                         |

|                                        | Exemplo de laço de repetição desenrolado em execuções sequenciais                                                                                                                                                                                                                               | 47                         |

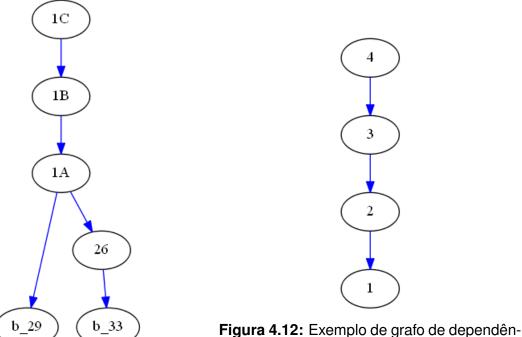

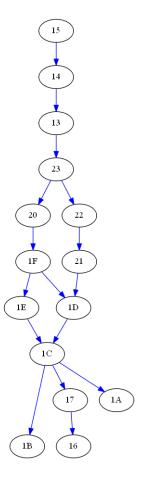

|                                        | Exemplo de grafo de dependências após a análise I                                                                                                                                                                                                                                               | 49                         |

|                                        | Exemplo de grafo de dependências após a análise II                                                                                                                                                                                                                                              | 49                         |

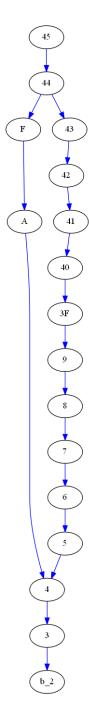

|                                        | Exemplo de grafo de dependências e técnica de particionamento                                                                                                                                                                                                                                   | 53                         |

| 4.14                                   | Exemplo de grafo de dependências sobre laço                                                                                                                                                                                                                                                     | 60                         |

|                                        | Exemplo de aplicação Intel x86                                                                                                                                                                                                                                                                  | 69                         |

| A.2                                    | Exemplo de aplicação Intel x86 transformada para a linguagem intermediária.                                                                                                                                                                                                                     | 70                         |

xii LISTA DE FIGURAS

# Lista de Tabelas

| <b>11</b>        | Regultados dos | e evperimentos | com os tempos em milisseguno | dos | 55 |

|------------------|----------------|----------------|------------------------------|-----|----|

| <del>4</del> . I | nesultados dos | experimentos.  | com os tempos em milisseduno | 10S | ၁၁ |

xiv LISTA DE TABELAS

# Lista de Siglas

RNG Gerador de números aleatórios (Random number generator)

RAW Dependência do tipo leitura após escrita (Read After Write)

WAR Dependência do tipo escrita após leitura (Write After Read)

WAW Dependência do tipo escrita após escrita (Write After Write)

PGHPF The Portland Group Compiler Technology

POS Reticulado de ordem parcial (Partial order set)

xvi LISTA DE TABELAS

# Sumário

| Re | Resumo |                                                        |    |  |  |  |

|----|--------|--------------------------------------------------------|----|--|--|--|

| Αŀ | ostrac | et e e e e e e e e e e e e e e e e e e                 | ix |  |  |  |

| 1  | Intro  | dução                                                  | 1  |  |  |  |

|    | 1.1    | Problema de paralelização automática de código binário | 3  |  |  |  |

|    | 1.2    | Hipótese e objetivo                                    | 7  |  |  |  |

|    | 1.3    | Organização da monografia                              | 7  |  |  |  |

| 2  | Trab   | alhos relacionados                                     | 9  |  |  |  |

|    | 2.1    | Considerações iniciais                                 | 9  |  |  |  |

|    | 2.2    | Estudos principais                                     | 9  |  |  |  |

|    | 2.3    | Estudos secundários                                    | 11 |  |  |  |

|    | 2.4    | Considerações finais                                   | 12 |  |  |  |

| 3  | Con    | ceitos sobre a paralelização de aplicações             | 13 |  |  |  |

|    | 3.1    | Considerações iniciais                                 | 13 |  |  |  |

|    | 3.2    | Paralelização de aplicações                            | 13 |  |  |  |

|    | 3.3    | Análise de instruções                                  | 14 |  |  |  |

|    |        | 3.3.1 Paralelização sobre código-fonte                 | 14 |  |  |  |

|    |        | 3.3.2 Paralelização sobre linguagem de máquina         | 14 |  |  |  |

|    | 3.4    | Paralelização manual e automática                      | 15 |  |  |  |

|    | 3.5    | Foco da análise e particionamento                      | 15 |  |  |  |

|    |        | 3.5.1 Paralelização entre blocos                       | 15 |  |  |  |

|    |        | 3.5.2 Paralelização entre iterações                    | 16 |  |  |  |

|    |        | 3.5.3 Paralelização híbrida                            | 17 |  |  |  |

|    |        | 3.5.4 Unidades de particionamento                      | 17 |  |  |  |

|    | 3.6    | Escopo da análise e paralelização                      | 18 |  |  |  |

|    | 3.7    | Preservação de consistência                            | 18 |  |  |  |

|    | 3.8    | Grau de paralelismo                                    | 19 |  |  |  |

|    | 3.9    | Teoria de ordem – grafos de ordem parcial              | 19 |  |  |  |

|    |        | Taxonomia                                              | 20 |  |  |  |

|    | 55     | 3.10.1 Taxonomia para dependências entre instruções    | 21 |  |  |  |

|    |        | 3.10.2 Paralelismo transparente e não transparente     | 22 |  |  |  |

|    |        | 3.10.3 Super-blocos                                    | 23 |  |  |  |

| xviii |  |  | SUM |  |

|-------|--|--|-----|--|

|       |  |  |     |  |

| <b></b> |                                                         | , ., ., • |

|---------|---------------------------------------------------------|-----------|

|         | 3.10.4 Segregação                                       | 25        |

| 4       | Abordagem para a paralelização automática de aplicações | 29        |

|         | 4.1 Objetivo                                            | 29        |

|         | 4.2 Metodologia empregada                               | 30        |

|         | 4.3 Estudo da arquitetura Intel x86                     | . 31      |

|         | 4.4 Desmontador e grafo de fluxo de controle            | 34        |

|         | 4.5 Linguagem intermediária                             | . 36      |

|         | 4.6 Análise de dependências                             | . 37      |

|         | 4.7 Análise de dependências em laços                    |           |

|         | 4.8 Particionamento                                     | 51        |

|         | 4.9 Ferramenta e implementação                          | 52        |

|         | 4.10 Experimentos                                       | 53        |

|         | 4.11 Exemplo de paralelização                           | 55        |

|         | 4.12 Considerações finais                               | 59        |

| 5       | Conclusão e trabalhos futuros                           | 61        |

| Re      | ferências                                               | 63        |

| Α       | Linguagem intermediária                                 | 67        |

|         | A.1 Instruções                                          | 67        |

|         | A.2 Sintaxe                                             |           |

|         | A.3 Exemplo                                             | 69        |

CAPÍTULO

1

# Introdução

A necessidade por processamento de alto desempenho e a redução de custo de recursos computacionais motivaram a construção de ambientes *scale-up* e *scale-out* (MICHAEL *et al.*, 2007). Esses ambientes permitem explorar o poder computacional de várias máquinas e componentes de maneira integrada. A tentativa de utilizar recursos disponíveis, no entanto, tem como obstáculo a natureza sequencial dos paradigmas mais convencionais (imperativo e orientado a objetos) da computação. Nesse contexto, aplicações tradicionais (principalmente o legado) acabam por explorar pouco o potencial desses ambientes. Para contornar esses problemas, esforços têm sido realizados para paralelizar essas aplicações de forma a permitir a utilização desses recursos.

As primeiras pesquisas realizadas na área de paralelização automática de programas datam do final da década de 1980 e início da década de 1990. Esses trabalhos focaram, principalmente, na paralelização de código-fonte para as linguagens C e Fortran (GILDER; KRISHNAMOORTHY, 1994). Em resumo, eles realizavam análises das dependências entre instruções e de fluxo em estruturas bem conhecidas dos programas, como laços, repetições, recursões em códigos-fonte, com objetivo de produzir técnicas para a paralelização de regiões dos programas que utilizavam esse tipo de estrutura. Ainda nesse período, outros trabalhos buscaram analisar as dependências de instruções a fim de compreender trechos de código-fonte que poderiam ser paralelizados (GRIEBL; COLLARD, 1995). Na década de 1990, pesquisadores como Zima *et al.* (1993) buscaram por soluções de paralelização automática de código-fonte para sistemas de memória compartilhada distribuída. Após utilizar máquinas de busca, i.e., IEEExplore, ACM Digital Library e Google Scholar, observou-se um período de 1993 ao início de década de 2000 em que poucos trabalhos

foram desenvolvidos em termos de paralelização de código. Em contrapartida, destacamse, nesse período, estudos e propostas de arcabouços para a escrita de códigos paralelos tanto para sistemas *scale-up* quanto *scale-out* (MICHAEL *et al.*, 2007).

No início de década de 2000, trabalhos concentraram-se na paralelização automática de programas seja explorando características do código-fonte ou do binário (BASTOUL, 2003; DEPARTMENT et al., 2003). Automatizando a paralelização, usuários sem conhecimentos do paradigma de programação concorrente (GHEZZI; JAZAYERI, 1997) teriam acesso aos recursos disponíveis tanto em computadores de uso pessoal, os quais já contavam com múltiplos núcleos ou processadores, quanto em ambientes distribuídos, tais como aglomerados (clusters) de computadores, grades (grids) computacionais, etc. Esses trabalhos focaram na paralelização sobre o código-fonte, principalmente sobre a linguagem C, utilizando modelos poliedrais (BASTOUL, 2003). O modelo poliedral é uma abstração que pode ser aplicada sobre iterações que ocorrem em laços de repetição, quando esses laços possuem limites, ou seja, as condições de término definidas por um contador. Nesse modelo, o domínio das iterações pode ser representado por um conjunto de inequações lineares, as quais podem ser modeladas por um poliedro. Mais especificamente, esse poliedro forma um conjunto convexo de pontos em um reticulado (lattice) (LI; PINGALI, 1992). Utilizando essa técnica, esses trabalhos focaram em transformar essas repetições de forma a criar blocos de execução paralelos. Apesar dos avanços significativos dessa abordagem, o foco em estruturas fechadas de repetição apenas permite a paralelização em casos específicos.

À partir de 2008, observou-se novo interesse pela área, com diversos trabalhos publicados. Bondhugula (BONDHUGULA, 2011) propõe uma técnica para otimizar a comunicação entre blocos de execução paralelos, obtidos à partir da paralelização de uma aplicação sequencial. Como a comunicação é limitada pela dependência entre diferentes instruções, e por sua vez, entre diferentes blocos, essa abordagem descreve o problema da distribuição dos blocos frente ao grau de paralelismo obtido. Howard et al. (HOWARD; RYAN; COLLINS, 2011) apresentam uma abordagem utilizando algoritmos evolutivos para a paralelização automática. Utilizando Programação Genética, esse trabalho descreve operações sobre blocos sequenciais de instruções, buscando formas de refatoração que levam ao paralelismo. A abordagem explora possíveis maneiras de separar as instruções em um dado número de processadores, de forma a não violar a dependência entre elas. (KOVACEVIC et al., 2013) apresentaram um arcabouço completo para a paralelização automática de aplicações. Nesse trabalho, os passos para obter o paralelismo são delineados, mas não são explicados em detalhes. Nessa abordagem, apenas dependências de acesso aos registradores do processador são consideradas, não se levando em consideração os acessos à memória.

Essas diversas frentes de pesquisa buscaram por diferentes maneiras de prover paralelismo para aplicações projetadas e desenvolvidas para execução sequencial. Contudo, observa-se a necessidade de ferramentas que permitam traduzir códigos binários sequenciais em versões paralelas, a fim de utilizar os recursos atualmente disponíveis em ambientes *scale-up* e *scale-out*. Isso se dá principalmente no que se refere a aplicações legadas (feitas para arquiteturas específicas), usualmente disponíveis apenas na forma de código binário. Esta é a lacuna considerada por este trabalho de mestrado, a qual motivou a definição da hipótese e do objetivo. Antes de apresentá-los, o problema abordado por este trabalho é melhor descrito na seção seguinte.

# 1.1 Problema de paralelização automática de código binário

O paradigma mais tradicional de desenvolvimento de *software* é voltado para a programação sequencial de aplicações. Nessa abordagem, as aplicações são definidas por conjuntos de instruções, que executam em uma sequência pré-definida. Quando um algoritmo é descrito em termos de uma sequência de instruções, a lógica inerente ao processo implica em dependências entre as partes envolvidas na execução. Dessa maneira, uma instrução, de maneira geral, não pode ser executada fora de ordem, caso contrário os dados podem entrar em um estado de inconsistência, comprometendo a lógica envolvida, i.e., a semântica da aplicação.

Programas construídos dessa maneira executam tão rápido quanto o processador permite, ou seja, a restrição de velocidade está na capacidade de execução de instruções por unidades de tempo concedidas pelo processador. Durante muitos anos, processadores sofreram uma rápida evolução em termos dessa capacidade. No entanto, em meados dos anos 2000, os fabricantes encontraram limitações físicas que comprometeram essa evolução, limitando, por enquanto, a expansão direta de velocidade de cada unidade de processamento. O principal obstáculo é a temperatura que o componente atinge quando o clock do processador é aumentado. Para contornar esse problema, o foco da construção desses componentes mudou, do aumento da frequência do relógio do processador para a inclusão de múltiplas unidades funcionais e núcleos em um único computador. No entanto, a utilização desse tipo de abordagem leva ao fato de que uma aplicação sequencial não pode mais utilizar todo o potencial oferecido pelo computador, pois sua construção a restringe a um único núcleo.

Além de processadores com vários núcleos, outra forte tendência na computação são os ambientes distribuídos. Em aglomerados de computadores (*clusters*), ambientes de grade computacional (*grid computing*) e na chamada computação em nuvem (*cloud computing*), sítios de máquinas são utilizados, em geral grupos de processadores, para o armazenamento de dados e a execução de aplicações. Porém, como no caso de processadores de vários núcleos, aplicações sequenciais não podem utilizar plenamente o potencial desses ambientes, pois sempre estarão restritas a um único núcleo.

Um dos obstáculos, portanto, para o uso da computação paralela e distribuída encontrase na dificuldade em migrar programas do tradicional paradigma sequencial para uma versão paralela, que permita utilizar o potencial dos novos tipos de ambientes computacionais. A dificuldade em modificar a aplicação para tal fim surge dos problemas causados pela rigidez na ordem de execução das instruções sequencialmente definidas. Como algumas instruções utilizam resultados de computações anteriores, cria-se uma dependência entre elas e, portanto, precisam ser executadas em sequência. Porém, essa dependência não ocorre necessariamente entre todas as instruções de uma mesma aplicação. De fato, se grupos de instruções puderem ser isolados de forma que não exista dependência entre eles, cada grupo poderia ser executado em paralelo sem prejudicar a lógica dos algoritmos envolvidos. Dessa maneira, pode-se projetar uma abordagem para a paralelização automática de aplicações. Para criar uma versão paralela de uma aplicação, deve-se analisá-la, estabelecer as dependências entre suas instruções, e gerar uma nova aplicação, pronta para ser executada em paralelo.

A análise de uma aplicação a fim de se obter paralelismo pode ser dividida em duas abordagens distintas. Ela pode ser feita em alto nível, seja em código-fonte ou outra abstração, ou em baixo nível, quando aplicada diretamente sobre uma linguagem de máquina. Muitos dos trabalhos existentes focam em análises de código-fonte como uma forma de auxiliar o desenvolvedor (BASTOUL, 2003; DEPARTMENT et al., 2003; GRIEBL; COLLARD, 1995). Neste trabalho de mestrado, o foco é dado para a linguagem de máquina, com o objetivo de se obter um paralelizador completo e transparente para o usuário final. Além disso, pode-se dividir a análise propriamente dita em duas fases. Uma fase estática, a qual é feita diretamente sobre as instruções da aplicação, seja em alto ou baixo nível, e uma possível fase dinâmica, em que resultados da execução podem ser analisados para se tomar decisões de paralelização. As duas fases não são mutuamente exclusivas, e podem ser usadas uma em suporte da outra.

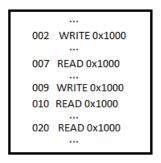

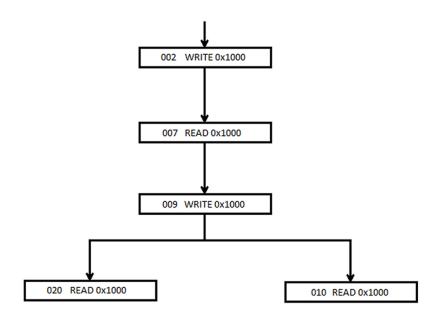

O problema da análise de dependências entre instruções é complexo. As dependências, de forma geral, podem ser diretas ou indiretas, ou seja, uma instrução pode depender imediatamente de outra, ou pode depender de uma (ou mais) instrução (ões) intermediária(s). Dessa forma, as dependências podem ser vistas como um grafo direcionado. Na Figura 1.1 é ilustrado um exemplo de código, em linguagem de máquina, onde existem dependências entre instruções. Na Figura 1.2, apresenta-se o grafo de dependências para esse código. As instruções 020 e 010 dependem da instrução 009, pois elas leem a memória na mesma posição onde foi realizada uma escrita. De forma similar, a instrução 007 depende da instrução 002. A dependência entre 009 e 007 ocorre de maneira diferente. Nesse caso, 009 irá sobrescrever o valor que 007 iria ler, e portanto 009 deve ser executada após 007.

A obtenção desse grafo, porém, pode ser muito difícil. Como uma aplicação tende a percorrer caminhos de execução variados, resultados de computações anteriores de-

Figura 1.1: Exemplo de código de máquina com dependências.

Figura 1.2: Exemplo de grafo de dependências.

terminam dependências entre instruções. Nesses casos, pode-se avaliar as condições necessárias para a ocorrência de dependências, verificando as computações envolvidas e buscando analisar seus possíveis resultados. No entanto, em alguns cenários as combinações possíveis de condições podem ser exponenciais. Portanto, a obtenção de um grafo completo e preciso de dependências envolve um problema exponencialmente difícil para diversas aplicações (GAREY; JOHNSON, 1979).

A complexidade se deve à dificuldade em prever os possíveis estados de uma aplicação após um período de execução. Entradas fornecidas à aplicação, seja pelo usuário, seja por meio de elementos externos (como geradores de números aleatórios), podem produzir estados variados. Dependendo de como o resultado de computações sobre essas entradas é reutilizado, o número possível de combinações de estados pode crescer exponencialmente. Isso ocorre, principalmente, quando há muitos caminhos condicionais, sendo que cada ramo de execução leva a potenciais estados distintos. No Algoritmo 1.1, um exemplo

de dependências complexas é ilustrado. Nesse algoritmo, o valor de i é inicializado de maneira aleatória, sobre o qual incidem várias computações. Em cada bloco condicional, a computação realizada depende do resultado do bloco anterior. Dessa forma, para cada bloco, as possibilidades para o valor de i dobram. Assim, ao término do bloco, o número de possibilidades para i é  $2^k$ , em que k é o número de blocos condicionais entre o valor inicial de i e o momento de leitura de i para acesso ao vetor vec. Se i é uma variável índice, como nesse caso, então ela determina um acesso à memória, como um deslocamento de vec e, portanto, conhecê-la é necessário para entender como a memória é acessada.

**Algoritmo 1.1:** Exemplo de pseudocódigo. Neste caso, prever o valor da variável i, ao fim do bloco, é exponencialmente difícil (GAREY; JOHNSON, 1979).

```

1: Seja vec um vetor de tamanho arbitrário, inicializado com valores arbitrários

2: i \leftarrow Saída de um RNG (gerador de números aleatórios)

3: if i < 10 then

i \leftarrow i * 12

5: else

6:

i \leftarrow i - 3

7: end if

8: if i < 5 then

9:

i \leftarrow i * 15

10: else

11:

i \leftarrow i/2

12: end if

13: if i > 100 then

14:

i \leftarrow i * 81

15: else

16:

i \leftarrow i + 4

17: end if

{... outros blocos condicionais similares}

18: X \leftarrow vec[i]

```

Outra questão importante está relacionada ao acesso à memória. Em laços de repetição, estruturas de dados podem ser acessadas em vários níveis. Por exemplo, uma árvore pode ser percorrida parcial ou integralmente, em que a partir de uma raiz, vários nós são lidos, possivelmente através de referências (ponteiros). Se alguma outra instrução acessar a mesma estrutura em outro ponto do programa, é preciso saber quais partes são acessadas para determinar se há ou não dependências. De forma geral, é muito difícil prever, para uma execução, quando e quais partes da estrutura serão acessadas dentro do laço de repetição. Ainda nesse sentido, a definição dos locais em que ocorrem acessos à memória compreende outro problema.

Esses diversos problemas justificam a proposta de trabalhos voltados para auxiliar desenvolvedores por meio da análise de dependências em aplicações, tanto em código-fonte como sobre código binário. Com base nessa motivação, a seção seguinte apresenta a hipótese e objetivo deste trabalho de mestrado.

#### 1.2 Hipótese e objetivo

A falta de ferramentas automáticas que permitam traduzir código binário de aplicações de propósito geral para versões paralelas motivou a hipótese deste trabalho, a qual é definida como segue:

A análise dos caminhos de execução de um código binário permite o particionamento desse programa em regiões independentes e sua posterior paralelização automática.

Motivado por essa hipótese, o objetivo deste trabalho foi o desenvolvimento de uma metodologia para a paralelização automática envolvendo a desmontagem (disassemble), a análise dos caminhos de execução determinísticos, i.e., aqueles que dependem apenas da entrada do programa, bem como os estocásticos, i.e., aqueles relacionados a resultados intermediários e desconhecidos na etapa de análise, a criação de grafos de fluxo de controle e dependências e o particionamento em unidades paralelas para execução em ambientes multinúcleo (multi-core). Como contribuição, aplicações legadas podem utilizar os recursos de ambientes paralelos atualmente disponíveis, principalmente em ambientes multinúcleo.

## 1.3 Organização da monografia

Esta monografia está organizada da seguinte maneira. No Capítulo 2, apresenta-se uma revisão da literatura, contando com os principais trabalhos encontrados, assim como suas limitações. Em seguida, conceitos utilizados durante o projeto são apresentados no Capítulo 3. No Capítulo 4, apresentam-se a abordagem desenvolvida e as atividades realizadas, destacando-se os problemas encontrados. O Capítulo 5 apresenta as conclusões e discussões sobre trabalhos futuros.

CAPÍTULO

2

# Trabalhos relacionados

#### 2.1 Considerações iniciais

Este capítulo apresenta alguns estudos primários e secundários (*surveys*), com o intuito de compreender a área de pesquisa na qual este trabalho de mestrado está inserido. Além disso, esses estudos permitiram melhor embasar o desenvolvimento da abordagem de paralelização automática.

## 2.2 Estudos principais

Banerjee (BANERJEE, 2013) procura fundamentar matematicamente conhecimentos e técnicas existentes para a determinação de dependências entre instruções. Esse trabalho introduz diversos conceitos e notações para acessos de leitura e escrita à memória (particularizado pela atribuição de um valor a uma variável) e para estruturas de repetição. O programa é definido como um conjunto de instruções, sobre o qual é imposta uma relação de ordem R, com o operador menor que (ou seja, <). Como a aplicação é executada sequencialmente, R é definida pela ordem em que instruções são processadas. Como a atribuição é a única instrução considerada (note que instruções de laços como *do-while* servem apenas para controle de fluxo, e não são consideradas para dependências), então elementos são apenas acessos à memória.

Seja P um programa e  $S \in P$  e  $T \in P$  elementos do seu conjunto de instruções, então se define S < T se e somente se S executa antes de T. No entanto, se S ocorre dentro de um laço de repetição, então esse acesso não pode ser considerado como uma

única execução. Em particular, considera-se que S possui instâncias, de acordo com a iteração considerada. Seja L o laço que contém S e I o índice que controla seu número de iterações. Dessa maneira, as instâncias de S são definidas por S(I). Se outro acesso  $T \in L$  for considerado, instâncias para T(J) também podem ser representadas. Assim diz-se que S(I) < T(J), se e somente se, a instância I de S executa antes de T(J). As posições léxicas de S e T dentro do laço são utilizadas para definir conjuntos de I e I, em que I0 executa antes de I1, I2,...,I4. Nesse caso, um acesso I2 pode ocorrer em um ou mais I4, e suas instâncias são representadas por I3, em que I4 denota o número de estruturas que I5 participa.

Sobre um laço de repetição bem definido, com a relação de ordem sobre as instâncias dos acessos conhecida, Banerjee define a existência de uma dependência entre  $S'=S(I_1,I_2,...,I_m)$  e  $T'=T(J_1,J_2,...,J_n)$  (definida por  $S'\sigma T'$ ) se S'< T', S' e T' acessam uma mesma região de memória M e um dos acessos é uma escrita. Além disso, a dependência é classificada em um de três tipos:

- $\mathit{flow-dependent}$  (dependente do  $\mathit{fluxo}$ ), em que S' escreve em M e T' realiza uma leitura;

- anti-dependent (antidependente), se S' lê M e, posteriormente, T' escreve nessa região;

- output-dependent (dependente por saída), se S' e T' escrevem em M.

Além dos tipos de dependência, Banerjee introduz também os conceitos de nível e distância, definidos pelo número de iterações que separam uma execução de S e T necessárias para a ocorrência de uma dependência. Para decidir se existe ou não uma dependência em um laço, ele é definido em termos de funções dos seus acessos à memória. Em particular, as variáveis envolvidas são expressas em um sistema de equações lineares, sujeitas a algumas restrições (também lineares). O trabalho demonstra que, se uma solução inteira existe para esse sistema, então uma dependência existe entre os acessos envolvidos, e as instâncias específicas podem ser derivadas da solução. Posteriormente, apresenta-se abordagens para resolver esses sistemas em casos específicos. Banerjee contribui para a conceituação de um elemento crítico para a paralelização automática, que é a análise de dependência, além de trazer avanços no tratamento de laços de repetição. No entanto, uma limitação importante dessa abordagem é desconsiderar o caminho de execução, no caso de saltos condicionais, que podem inviabilizar a relação de ordem Rproposta de acordo com o comportamento da aplicação. Além disso, esse trabalho pressupõe a existência de índices bem definidos em laços, algo que nem sempre ocorre na prática.

#### 2.3 Estudos secundários

Nesta seção, alguns estudos secundários (*surveys*) são abordados, assim como lacunas conhecidas na área de paralelização automática.

Em 2005, DiPasquale *et al.* (DIPASQUALE; WAY; GEHLOT, 2005) publicaram um estudo comparativo com várias técnicas para paralelização automática. A primeira técnica abordada testou a análise sobre variáveis escalares e vetores. Quanto a variáveis escalares, laços foram analisados de forma a tentar transformar os índices da iteração (quando presentes) em equações lineares. Essa abordagem permitiu paralelizar o laço resolvendo tais equações. No entanto, essa técnica é limitada a laços em programas que funcionam de maneira muito específica. A técnica de análise sobre vetores envolve segregação (ver Seção 3.10.4) de dados em vetores para cada instância de execução. O vetor é analisado e, quando possível, reduzido a uma equação que representa seus valores no tempo. A partir dessa equação é possível determinar se há dependências para esse vetor, dentro de um laço, por exemplo. Se não existem dependências, então o laço pode ser paralelizado. Uma desvantagem dessas técnicas é que elas são restritas a cenários muito específicos o que, em uma aplicação real, pode ser muito raro. Além disso, essas técnicas não abordam ponteiros e outros tipos de funcionalidades clássicas.

A próxima técnica abordada é denominada análise comutativa. A ideia é que se algumas operações, como uma iteração de um laço, apresentam certas equivalências, então a ordem de execução dessas iterações não influencia no resultado final. Essas equivalências são baseadas na propriedade matemática de comutação entre certas operações. Em particular, essa técnica é aplicada sobre objetos em linguagens orientadas a objetos.

Em sequência, aborda-se a técnica de paralelização em alto nível, a qual propõe uma linguagem intermediária para paralelização. Essa linguagem, implementada em uma biblioteca, é referenciada por chamadas dentro da aplicação. Em particular, estruturas típicas das linguagens C e FORTRAN, como vetores, são automaticamente preparadas para serem paralelizadas quando acessadas em laços de repetição. Além disso, outras otimizações são feitas para explorar automaticamente o paralelismo nos procedimentos do programa. A grande limitação dessa técnica está em sua restrição a poucas linguagens e a necessidade de refatorar o código-fonte para utilizá-la.

Em outro trabalho, (FRUMKIN *et al.*, 1998) apresentam comparações entre ferramentas de paralelização automática disponíveis na literatura. A primeira ferramenta abordada é denominada *CAPTools* (IEROTHEOU *et al.*, 1996). Essa ferramenta aceita código FORTRAN sequencial e converte chamadas entre regiões independentes em termos de passagem de mensagens, de forma similar a bibliotecas como MPI e PVM. Nessa ferramenta, uma interface gráfica é fornecida ao usuário para que ele decida sobre o nível de paralelismo e de análise entre outros parâmetros.

A próxima ferramenta é o compilador PGHPF. Também voltado para a linguagem FOR-

TRAN, essa ferramenta visa automaticamente paralelizar laços de repetição, criando blocos de aplicação a serem distribuídos entre processadores de uma ou mais máquinas. Esse compilador permite que o desenvolvedor decida sobre o tamanho dos dados a serem separados entre esses blocos, de forma a controlar a quantidade de comunicação realizada, e também a quantidade de dados a serem segregados.

A terceira ferramenta considerada é composta por diretivas de compilação para uma arquitetura específica, em particular os processadores *SGI Origin2000*. Essas diretivas são inseridas no código-fonte, dentro de laços de repetição, para indicar variáveis que não possuam dependências entre si. Essa inserção pode ser feita pelo desenvolvedor, ou por ferramentas disponíveis para essa arquitetura.

As ferramentas consideradas são comparadas no trabalho de Frumkin *et al.* (FRUM-KIN *et al.*, 1998), utilizando *benchmarks* de forma a conhecer os ganhos obtidos com o paralelismo. Uma conclusão importante dos resultados é que todas as técnicas superam o desempenho de execuções sequenciais. Porém, o aumento no desempenho depende de ajustes e calibragens feitos pelo desenvolvedor ao empregar todas as técnicas consideradas. Essa restrição denota uma limitação importante dessas ferramentas, já que a necessidade de intervenção do usuário reduz o grau de automação do processo.

## 2.4 Considerações finais

Este capítulo apresentou trabalhos relacionados à área de paralelização de aplicações, com técnicas automáticas e manuais. Algumas fundamentações matemáticas foram introduzidas, assim como descrições de diversas abordagens para o problema. Esses estudos contribuíram para este trabalho de mestrado no sentido de propiciar um melhor entendimento das etapas envolvidas na paralelização, além de contribuir com ideias para atacar o problema de análise de dependências e particionamento de programas.

Diferentemente das abordagens apresentadas neste capítulo, este trabalho realiza o processo de paralelização de maneira automática, diretamente sobre o código binário. Além disso, a análise de dependências é feita sobre o código como um todo, e não apenas em estruturas particulares. Dessa maneira, a necessidade de intervenção por parte de desenvolvedores e usuários sobre o processo é minimizada.

CAPÍTULO

3

# Conceitos sobre a paralelização de aplicações

#### 3.1 Considerações iniciais

Este capítulo apresenta o conceito de paralelização de um programa e as complicações decorrentes desse processo. Também são apresentadas abordagens existentes para realizar essa operação, e outros conceitos pertinentes, além de uma taxonomia. Introduz-se também alguns conceitos da teoria de ordem, pertinentes ao problema tratado.

#### 3.2 Paralelização de aplicações

A paralelização de uma aplicação consiste em transformar um programa sequencial em uma versão que pode ser executada em paralelo, sem comprometer sua semântica (MES-SINA; WILLIAMS; FOX, 1994). A versão transformada é formada por um conjunto de unidades funcionais que, durante uma eventual execução, podem ser distribuídas para vários processadores. Essas unidades podem ser blocos de instruções da aplicação original ou versões com semântica equivalente, porém aptas a executar em paralelo.

Uma versão transformada, quando executada em um dado ambiente, deve produzir resultados idênticos ao da aplicação original, não apenas ao final do processo, mas também em eventuais computações intermediárias. Essa característica é denominada consistência da transformação, e precisa ser preservada para uma paralelização bem sucedida.

Para paralelizar a aplicação, várias abordagens são possíveis. O processo pode ser

efetuado tanto sobre código-fonte como sobre aplicações compiladas em linguagem de máquina. A transformação pode ser manual, por meio de análise humana, bem como automática com técnicas algorítmicas. As abordagens podem focar em componentes específicos do programa, ou o todo. Essas possibilidades são descritas em mais detalhes nas próximas seções.

#### 3.3 Análise de instruções

A fase inicial do processo de paralelização consiste em interpretar a semântica do programa, de forma a compreender suas computações. Para tanto, deve-se considerar como a aplicação está apresentada para o processo. Se ela está disponível como código-fonte ou se está compilada. Esses dois casos são detalhados na próxima seção, e suas vantagens e desvantagens são ponderadas.

Após a conclusão da interpretação, uma abstração pode ser gerada, e a presença ou não do código-fonte não possuirá impacto nos processos seguintes de paralelização e particionamento das instruções.

#### 3.3.1 Paralelização sobre código-fonte

A análise de código-fonte consiste em observar a linguagem do programa e buscar maneiras de paralelizar as instruções. Uma abordagem muito comum consiste em o próprio desenvolvedor repensar trechos de código e criar alternativas paralelas. Esses casos são explícitos e, em geral, as unidades paralelas estarão bem descritas no código transformado. Outra maneira consiste em algoritmos que buscam estruturas específicas dentro do código, e quando possível, as transformam em versões que podem ser executadas em paralelo.

A abordagem em código-fonte apresenta uma vantagem importante quando a paralelização é manual, já que esse código possui abstração mais alta, mais fácil de ser compreendido por seres humanos. No entanto, essa abordagem possui complicações para processos automáticos, já que exige maior interpretação das abstrações e da linguagem.

Uma limitação importante deste caso é uma questão prática: muitas vezes, o códigofonte não está disponível. Nesse caso, a paralelização seria inviável. Outra limitação é a restrição de técnicas automáticas para uma linguagem específica.

#### 3.3.2 Paralelização sobre linguagem de máquina

Aplicações compiladas são descritas por uma linguagem de baixo nível, para uma máquina específica. Em geral, essas arquiteturas possuem instruções de baixa abstração. Como consequência, técnicas automáticas precisam de menos instrumentos para interpretar esses cenários, já que não precisam fazer análises léxicas e sintáticas. No entanto,

essas linguagens são, em geral, menos intuitivas para leitura humana e apresentam maior dificuldade para a paralelização manual.

Uma vantagem importante deste tipo de processo é a capacidade de transformar qualquer aplicação de uma dada arquitetura em uma versão paralela, independentemente da disponibilidade do código-fonte. Para linguagens interpretadas, no entanto, o próprio código-fonte pode ser visto como binário. para esses casos, a possibilidade de realizar a paralelização depende da capacidade da ferramenta em tratar o código final.

### 3.4 Paralelização manual e automática

A atuação do desenvolvedor, ou de um terceiro sobre o código-fonte para transformar uma região sequencial em blocos paralelos caracteriza a paralelização manual (HUANG; STEF-FAN, 2011). Nesse cenário, diversas técnicas podem ser empregadas, desde métodos em que estruturas específicas são localizadas e transformadas até casos *ad-hoc*, em que a intuição e conhecimento prévio são aplicados. Enquanto resultados excelentes podem ser obtidos, especialmente quando o domínio do programa é bem compreendido, a abordagem manual apresenta uma limitação evidente: o processo é artesanal, sendo restrito a aplicações específicas, além de necessitar da disponibilidade do código-fonte e conhecimento do desenvolvedor. Para aplicações compiladas a dificuldade aumenta, dado que a falta de abstração torna a interpretação mais complicada.

A paralelização automática, em contrapartida, consiste em utilizar algoritmos para varrer instruções e encontrar regiões que possam ser paralelizadas. Esse processo tipicamente busca por blocos com estruturas pré-definidas a serem modificadas, ou trechos sem dependências entre si para serem particionados. Essa abordagem possui uma vantagem importante, já que não depende da intervenção do desenvolvedor.

Uma outra possibilidade são técnicas híbridas ou semi-automáticas, onde algumas etapas são automatizadas, com intervenção do desenvolvedor nas demais fases.

#### 3.5 Foco da análise e particionamento

A transformação pode ser feita sobre alguns possíveis cenários: entre blocos ou regiões distintas do programa; entre iterações de estruturas de repetição; e, finalmente, em cenários híbridos, em que ocorrem ambos casos.

#### 3.5.1 Paralelização entre blocos

Define-se por bloco básico um trecho sequencial de instruções da aplicação. Nessa abordagem, trechos da aplicação original são extraídos e analisados, de forma a encontrar um conjunto em que os trechos não possuam dependências entre si.

Uma possível paralelização busca o particionamento de blocos básicos independentes, ou seja, regiões em que os resultados das computações envolvidas não possuem interdependência. Nesse caso, a ordem de execução das regiões não interfere no resultado final. Se casos como esses puderem ser detectados, então o particionamento é trivial: cada região é inserida em uma unidade funcional, podendo eventualmente ser executada em paralelo.

Uma outra possível situação consiste em regiões com instruções misturadas. Nesse caso, algumas instruções de um bloco básico dependem de outras em uma outra região, mas não todas. Por exemplo, seja  $b_1$  um bloco básico com n instruções, numeradas de  $I_1,\ldots,I_n$ , e  $b_2$  um bloco básico com m instruções,  $J_1,\ldots,J_m$ . Considere que  $I_{(i+2)}$  dependa de  $I_i$  e  $J_{(j+2)}$  de  $J_j$ , e que  $J_1$  dependa de  $I_{(n-1)}$  e  $J_2$  de  $I_n$ . Dessa maneira, existe uma dependência entre  $b_2$  e  $b_1$ , porém apenas entre partes distintas dos blocos. Em particular, o subconjunto  $J_j \in J$  para todo j par depende de  $I_i \in I$  para todo i par. O mesmo vale para os subconjuntos com i e j ímpares. Para esse cenário, as instruções que possuem dependências entre si podem ser extraídas dos blocos básicos em que se encontram, formando conjuntos separados. Nesse caso em particular, conjuntos seriam formados por instruções  $I_i$  e  $J_j$  para i e j separados por paridade. O particionamento então é feito transformando esses grupos em unidades funcionais, que podem ser executadas em paralelo.

#### 3.5.2 Paralelização entre iterações

Um caso específico e importante na paralelização trata de estruturas de repetição. Essas regiões de código executam uma ou mais vezes, com uma característica bem definida: as instruções executadas são sempre as mesmas, variando apenas os dados sendo trabalhados, e eventuais caminhos de execução. É importante notar que as funções internas do laço podem variar entre iterações. Por exemplo, um caminho condicional pode chamar procedimentos diferentes dependendo dos valores na memória. Em outros casos, como polimorfismo dinâmico e estático, mensagens distintas são traduzidas para métodos distintos. Nesse caso, a análise precisa considerar todos os caminhos possíveis.

Para efeito da análise de dependências, pode-se considerar a estrutura como um bloco básico, que é executado diversas vezes em sequência. Com essa abordagem, o processo pode ser realizado de maneira similar à paralelização entre blocos, com uma ressalva: o número de iterações nem sempre é conhecido. Essa característica leva a complicações nas decisões de análise. Uma possibilidade é considerar o número infinito, e analisar todas as possíveis dependências para esse caso. Quando tal análise é possível, as técnicas de particionamento em blocos podem ser aplicadas. Dessa maneira, instruções que dependam de outras em iterações seguintes são extraídas para formar grupos paralelizáveis.

Uma característica muito importante em estruturas de repetição é que o número de

iterações pode ser muito alto. De fato, para algumas aplicações, o tempo gasto iterando em laços pode ser muito maior do que o tempo gasto em blocos sem repetição. Como consequência, é desejável para a paralelização que as iterações sejam o mais independentes entre si possível, de maneira a formarem unidades paralelas. Quando esse cenário é possível, o grau de paralelismo (definido em 3.8) obtido pode ser muito alto, com um ganho importante para o programa. No entanto, nem sempre essa independência existe. Para contornar essas restrições, algumas técnicas podem ser aplicadas, com o intuito de remover dependências e permitir esse tipo de particionamento. Algumas dessas técnicas são apresentadas no Capítulo 4, junto com uma discussão sobre suas aplicações.

Além dessa abordagem existem outras maneiras de tratar a análise e o particionamento de laços de repetição, como análise de índices e separação de acessos à memória. No Capítulo 2, apresenta-se uma abordagem que considera os acessos no laço como um sistema de equações lineares. Apresenta-se também uma discussão sobre como resolver o particionamento, encontrando soluções para o sistema.

#### 3.5.3 Paralelização híbrida

O particionamento de regiões contendo trechos com e sem repetição pode ser feito de maneira híbrida, com conceitos dos dois tipos de paralelização. Quando laços de repetição são abordados como blocos executados repetidamente de maneira sequencial, eles podem ser analisados junto com outros blocos sem repetição. Dessa maneira, grupos de instruções podem ser extraídos de todas as regiões, de acordo com as dependências existentes entre elas, e particionados em unidades funcionais.

#### 3.5.4 Unidades de particionamento

O particionamento consiste na criação de unidades funcionais, cada uma contendo blocos de instruções prontos para serem executados. O resultado do processo cria unidades que não possuem dependências entre si, o que permite sua execução em paralelo. No decorrer da análise e particionamento, unidades geradas em algumas regiões de código podem, no entanto, depender de unidades geradas em outras fases do processo de paralelização. Essa característica permite que enquanto algumas regiões da aplicação apresentem algum grau de paralelismo, outras podem não ter tal característica. Também é possível o surgimento de gargalos, dado que algumas regiões da aplicação apresentem pouco ou nenhum grau de paralelismo.

O tamanho de cada unidade pode variar de acordo com a abordagem utilizada. Por questões práticas, como o tempo para enviar cada unidade para um processador ou outras eventuais restrições, pode ser desejável criar unidades maiores ou menores. Essa decisão depende da estratégia escolhida, e possui implicações no tamanho dos blocos a serem analisados e unidades mínimas a serem geradas. O tamanho consiste, em geral, no

número de instruções dentro da unidade. Caso haja laços de repetição dentro da unidade, o número de iterações estimado pode ser utilizado para definir o tamanho.

## 3.6 Escopo da análise e paralelização

O particionamento e análise são feitos sobre regiões de instruções bem definidas da aplicação, escolhidas de acordo com a abordagem utilizada. A escolha possui implicações importantes sobre o processo e, em geral, decorre de um compromisso entre as questões que devem ser consideradas: o desempenho do processo e o grau de paralelismo obtido. É importante notar que cada região pode ser subdividida em um ou mais blocos para a análise. Para efeito de simplificação, esse tipo de região será referenciada como uma super-região (HANK et al., 1993).

Quando uma super-região é definida, ela torna-se uma caixa-preta dentro do processo de análise para outras super-regiões. Em particular, todas as dependências internas são expressas em função de suas entradas e saídas. Uma super-região pode conter um desvio para uma ou mais super-regiões, inclusive a si mesma. A análise de dependências e particionamento são feitos sobre todas as suas instruções. Uma super-região muito grande pode conter muitos caminhos de execução e, portanto, muitas dependências. Dessa maneira, a análise tenderá a ser demorada. Em contrapartida, mais instruções podem ser comparadas individualmente, aumentando as possibilidades de posterior particionamento.

Uma outra característica importante, mas menos evidente, é o número de combinações entre casos de dependências. Em particular, alguns caminhos de execução podem permitir um número muito alto de possibilidades para o resultado de computações. Como exemplo, caminhos condicionais em certas configurações podem criar cenários com um número exponencial de resultados possíveis. Quando ocorre essa explosão combinatória, uma abordagem comum é assumir todos os valores possíveis para essas computações. Esses casos podem criar dependências muito abrangentes, inviabilizando o particionamento. Super-regiões muito grandes possuem tendência a apresentar um número maior desses casos, podendo reduzir o grau de paralelismo obtido.

#### 3.7 Preservação de consistência

Para que a semântica da versão transformada da aplicação seja equivalente à original, algumas propriedades devem ser observadas. Em particular, as dependências entre instruções devem ser mantidas. Quando esse caso ocorre, a ordem original de execução dessas instruções deve ser preservada, caso contrário, o resultado das computações será diferente, e a aplicação perderá consistência e terá seu resultado comprometido. Mais informações sobre a natureza das dependências são apresentadas na Seção 3.10.

A consistência é uma métrica crítica para o processo de paralelização. A não observância dessa característica implica em uma eventual distorção do programa original, o que não é aceitável para o processo. Dessa maneira, análises e métodos que garantam a preservação da consistência são um ponto central da paralelização.

#### 3.8 Grau de paralelismo

Uma métrica relevante sobre aplicações transformadas é o seu grau de paralelismo (GOS-DEN, 1966), que é o número de unidades paralelas possíveis em uma execução. Esse valor pode variar dentro de um mesmo programa, dependendo da região considerada. Em particular, alguns blocos podem possuir alto grau de paralelização, enquanto outras regiões podem ter um grau muito pequeno ou até mesmo inexistente.

Embora, idealmente, seja desejável o maior grau de paralelismo possível, para alguns casos um paralelismo muito alto pode ser desvantajoso. Por exemplo, o ganho de desempenho para uma única instrução paralela pode não compensar a sobrecarga de desempenho (*overhead*) para distribuí-la. Quanto exatamente é esse impacto varia de arquitetura para arquitetura, e deve ser considerado no momento de encapsular as instruções em unidades paralelas. As variações sobre essa quantidade dependem principalmente do número de dependências existentes e que possam ser removidas entre as regiões consideradas. Para alguns casos, as instruções podem possuir muitas interdependências, impossibilitando sua separação. Em outros casos, total separação é possível, permitindo uma alta paralelização.

## 3.9 Teoria de ordem – grafos de ordem parcial

Um aspecto importante da paralelização é a geração de grafos como subprodutos das análises envolvidas. Em particular, os grafos de fluxo, que denotam a ordem de execução da aplicação, e de dependências, que definem quais instruções podem ser executadas em paralelo com outras, e quais devem ser executadas sequencialmente. Como a ordem é importante para esse último caso, esse grafo pode ser tratado como um grafo de ordem parcial (WARD, 1954). Além disso, o particionamento envolve técnicas sobre grafos bem estabelecidas em teoria de ordem. Por esse motivo, esta seção introduz alguns conceitos e técnicas dessa teoria.

Seja U um conjunto, e seja (E,F) um par de elementos  $E,F\in U$ . Seja AU o conjunto de todos os pares (E,F) possíveis em U. Define-se a relação  $\oplus$  sobre U como um relacionamento entre dois de seus elementos. Denomina-se  $\oplus(E,F)$  a relação  $\oplus$  sobre um par (E,F).  $\oplus$  pode ser definida sobre todos os pares em AU, ou apenas sobre um subconjunto  $SAU\in AU$  de pares. Se  $\oplus$  for definida sobre todo AU ela é dita uma relação total, caso contrário  $\oplus$  é uma relação parcial.  $\oplus$  é definida como uma relação de ordem

quando para  $\oplus(E,F)$ ,  $\oplus$  definir uma direção, denotada por  $E\oplus F$ . Nesse caso, diz-se que E relaciona F. Além disso,  $\oplus$  deve obedecer às seguintes propriedades:

- $\forall E \in U, \oplus(E,E)$  é definido (reflexiva);

- $\forall E, F, G \in U$ , se  $E \oplus F$  e  $F \oplus G$ , então  $E \oplus G$  (transitiva);

- $\forall (E,F)$  se  $E \oplus F$  existe, então  $F \oplus E$  não pode ocorrer (anti-simétrica).

Seja G um grafo direcionado definido sobre um conjunto U e uma relação de ordem  $\oplus$ . Cada vértice  $V \in G$  é definido como um elemento  $E \in U$ . Uma aresta A(V,T) entre os vértices V(G) e T(G) existe se e somente se  $\oplus(E,F)$  é definido, em que E é o elemento do vértice V e F o de T. A direção da aresta depende da ordem do relacionamento, portanto se  $E \oplus F$ , a aresta sairá de V em direção a T e vice-versa. Como consequência das características de  $\oplus$ , o grafo possui algumas propriedades: se A(V,T) e A(T,X) existem, então A(V,X) existe; se A(V,T) existe então A(T,V) não existe e A(V,V) existe. Um grafo de dependências pode ser interpretado também dessa maneira. Se os vértices forem instruções, então as arestas definem a ordem de execução entre elas. Se  $\oplus$  não estiver definido entre duas instruções (ou elementos), então não há dependência entre eles.

Sobre grafos de ordem parcial define-se o conceito de anticadeia (COMTET, 1974) (antichain), que consiste em um conjunto de vértices sobre os quais  $\oplus$  não está definido (ou seja, entre os quais não há arestas). A cardinalidade da maior anticadeia existente no grafo define a sua largura W. É interessante observar que o maior grau de paralelismo possível em uma região da aplicação é o valor W de seu grafo de dependências. Todas as anticadeias nesse grafo consistem em instruções sem dependências entre si. Se as anticadeias puderem ser determinadas, então o particionamento consiste em separar seus elementos. Em particular, é desejável que dentro desses grupos  $\oplus$  esteja definida como uma relação de ordem total. Os algoritmos conhecidos para a obtenção de anticadeias possuem complexidade exponencial (JOHNSTON, 1976), uma limitação que precisa ser contornada para sua aplicação no particionamento de aplicações.

#### 3.10 Taxonomia

Nesta seção, são apresentadas taxonomias para a paralelização de aplicações. Primeiramente é detalhada a taxonomia de Bernstein (BERNSTEIN, 1966) sobre dependências entre instruções, em seguida uma taxonomia sobre paralelismo implícito e explícito. Em seguida, o conceito de super-regiões é detalhado, o qual é definido sobre grafos de fluxo de execução de programas. Posteriormente, o conceito de segregação, o qual produz cópias idênticas de trechos de memória de um programa a fim de evitar problemas de consistência. Finalmente, apresenta-se o conceito de execução especulativa, o qual faz a tentativa

3.10. Taxonomia 21

de executar instruções futuras a fim de aumentar o desempenho de aplicações com o custo de, eventualmente, desfazer tais operações para manter consistência.

#### 3.10.1 Taxonomia para dependências entre instruções

A dependência entre duas instruções ocorre quando a semântica da aplicação resulta da ordem de execução entre elas, ou seja, quando uma execução fora de ordem pode comprometer a consistência do algoritmo. Uma maneira de classificar esse tipo de dependência foi proposta por Bernstein (BERNSTEIN, 1966). Esse tipo de dependência refere-se ao acesso a variáveis, ou seja, a dados, e pode ser dividido em três categorias: *read-after-write* (RAW) (leitura após escrita), *write-after-read* (WAR) (escrita após leitura) e *write-after-write* (WAW) (escrita após escrita).

Dependências do tipo RAW são provenientes de leituras em variáveis (registros ou posições de memória) feitas após uma escrita nessa mesma variável. Como o resultado esperado da leitura é o que foi escrito anteriormente, não é possível executar consistentemente essa leitura antes da escrita.

As dependências WAR são produzidas por escritas após a leitura de uma variável. Nesse caso, a escrita sobrescreve o valor, o que comprometeria o resultado da leitura caso essas instruções executassem fora de ordem. Porém, é possível evitar esses problemas de consistência com algumas estratégias, como salvar o valor em outro lugar, ou alterar a posição de escrita (e subsequentes acessos), caso a semântica permita. O último tipo, WAW, refere-se à dependência da ordem entre escritas. Essencialmente, para manter a consistência, a última escrita deve prevalecer ao final da execução dessas instruções. Em paralelização, quando esse caso é identificado, todas as escritas exceto a última podem ser descartadas, sem prejudicar a semântica da aplicação.

Na Figura 3.1, é apresentado um exemplo de uma dependência do tipo RAW. Para esse caso, suponha que não ocorra nenhuma modificação no registador **edx** entre as instruções 2 e 4 de um programa em linguagem de montagem para processadores da família de arquiteturas x86. Dessa forma, na instrução 2 escreve-se o valor 5 na região de memória apontada por **edx**. Na instrução 4, essa região de memória é lida. Nesse tipo de dependência, espera-se que na instrução 4, o valor 5 seja retornado. A Figura 3.2 mostra um exemplo da dependência do tipo WAR. Novamente, assume-se que *edx* não é modificado entre as instruções 2 e 4. Nesse caso, a instrução 2 precisa ser executada antes da 4. Se a instrução 4 for executada primeiro, o valor contido na região de memória apontada por *edx* seria sobrescrito, e uma execução posterior a instrução 2 poderia retornar um valor inválido. Um exemplo de dependência do tipo WAW é mostrado na Figura 3.3. Nesse caso, o valor na região apontada por *edx* é alterado na instrução 2 e na 4. Uma posterior leitura nessa região, no entanto, precisa mostrar o valor escrito na instrução 4, ou seja, 8 nesse exemplo. Observe que para esse tipo de dependência, as instruções 2 e 4 podem

ser executadas fora de ordem, desde que seja garantido que o valor escrito pela instrução 4 predomine para uma próxima leitura.

```

1 func:

2    mov [edx],5

3    ...

4    mov eax,[edx]

```

Figura 3.1: Dependência do tipo RAW.

```

1 func:

2     mov eax,[edx]

3     ...

4     mov [edx],5

```

Figura 3.2: Dependência do tipo WAR.

```

1 func:

2 mov [edx],5

3 ...

4 mov [edx],8

```

Figura 3.3: Dependência do tipo WAW.

#### 3.10.2 Paralelismo transparente e não transparente

Uma outra taxonomia em termos do tipo de paralelismo obtido em aplicações distingue o paralelismo transparente do não transparente (YARDIMCI, 2008). O paralelismo transparente é aquele em que um usuário tem a ilusão de que a aplicação executou de forma sequencial, quando de fato ela executou em paralelo. Nesse caso, a paralelização da aplicação é transparente para o usuário final ou para o desenvolvedor do software. A paralelização pode ocorrer tanto em tempo de compilação como durante a execução, por meio de módulos do sistema operacional ou empregando alguma outra abstração intermediária.

O paralelismo é dito não transparente quando ele é evidente para o usuário ou para o desenvolvedor. Nesse cenário, o desenvolvedor pode criar o paralelismo de maneira direta, por meio de funcionalidades do sistema operacional ou da plataforma alvo da aplicação, ou utilizando ferramentas que buscam alterar o código-fonte para introduzir regiões paralelizáveis. Para o usuário, o paralelismo fica explícito quando a aplicação é distribuída entre processadores de forma manual, ou automática mas com informações claras sobre a localidade dos processos.

3.10. Taxonomia

Este trabalho tem como objetivo gerar uma ferramenta para paralelização transparente, de forma a suprimir o trabalho extra necessário por parte de desenvolvedores e usuários para atingir o paralelismo. Ao automatizar o processo de distribuição, a ferramenta visa facilitar o processo, aumentando a abrangência de programas sendo paralelizados.

#### 3.10.3 Super-blocos

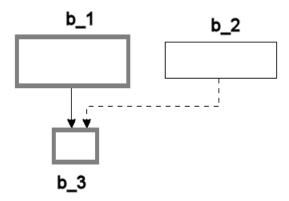

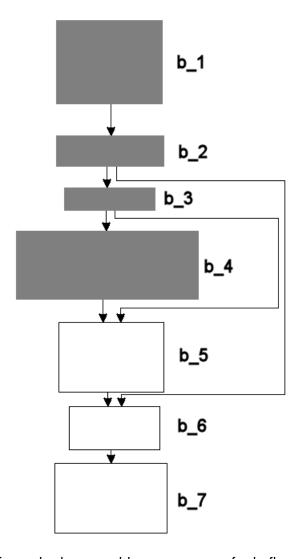

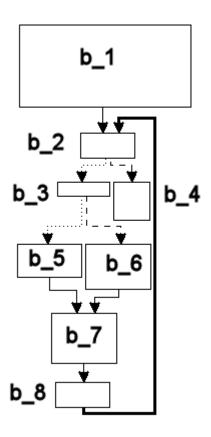

(HANK *et al.*, 1993) introduzem o conceito de super-blocos (*superblocks*), os quais são definidos por blocos básicos de instruções que não possuem entradas oriundas de outros blocos básicos. Uma entrada é definida como um salto condicional, ou uma consequência natural da execução em direção ao bloco básico. Na Figura 3.4, observa-se um bloco de instruções com um salto entrando entre as instruções *Inst 2* e *Inst 3*, vindo de uma outra região da aplicação. Na Figura 3.5, um grafo de fluxo de execução de uma aplicação é apresentado, no qual os vértices representam blocos de instruções, e as arestas caminhos possíveis de execução. Em particular, os vértices marcados em cinza representam o bloco observado na Figura 3.4. Esse bloco é particionado em dois vértices, pois há mais de um caminho para atingir a segunda região, após a instrução *Inst 2*. Nesse caso, a entrada representada na Figura 3.4 torna-se a aresta representada em tracejado no grafo.

Para ser considerado um super-bloco, os blocos não podem conter entradas (exceto alguma entrada em seu início), mas podem conter saídas, ou seja, saltos para fora do bloco. No grafo de fluxo, um conjunto de vértices é considerado um super-bloco quando, para cada vértice, no máximo uma aresta entra, independentemente do número de arestas saindo. Na Figura 3.6, tem-se um exemplo de um grafo de fluxo com uma super-bloco definido pelos vértices marcados em cinza.

Figura 3.4: Exemplo de bloco com entrada lateral (Adaptado de (HANK et al., 1993)).

# 3.10.4 Segregação

DiPasquale *et al.* (DIPASQUALE; WAY; GEHLOT, 2005) introduzem a ideia de segregação de dados. Essa técnica, aplicada à paralelização, tem como objetivo particionar os dados acessados pela aplicação e separá-los em regiões distintas. Esse particionamento pode envolver a clonagem dos dados ou apenas o particionamento de um vetor. O objetivo dessa

Figura 3.5: Exemplo de bloco com entrada lateral em um grafo de fluxo de execução.

Figura 3.6: Exemplo de super-bloco em um grafo de fluxo de execução.

abordagem é criar imagens de dados, de forma que aplicações paralelizadas possam trabalhar sobre elas de maneira independente. De acordo com a semântica da aplicação, a segregação não só é possível, como também elimina alguns tipos de dependências que poderiam comprometer o paralelismo.

#### 3.10.5 Execução especulativa

É possível que, para uma dada aplicação, duas regiões distintas de código possuam ou não dependência entre si, de acordo com parâmetros da aplicação. Esses parâmetros são tipicamente desconhecidos em tempo de compilação, como por exemplo, entradas de usuários, saídas de RNG (geradores de números aleatórios), etc. Nesse caso, uma abordagem possível é a execução especulativa. Ela consiste em executar essas regiões em paralelo e, caso os parâmetros fornecidos caracterizem a dependência, a execução da região dependente é descartada. Caso não ocorra a dependência, a execução é preservada. Em geral, os testes que determinam se ocorreu ou não uma dependência são baseados em informações fornecidas por uma análise anterior. Outro fator importante para essas execuções é que nem sempre elas podem ser retroagidas, ou seja, descartadas sem perdas. Dessa maneira, a aplicação dessas técnicas depende do caso considerado. Nos Algoritmos 3.1 e 3.2, apresenta-se um exemplo de dependência entre blocos que ocorre apenas com parâmetros específicos. Em particular, o Bloco 2 depende do Bloco 1 quando o valor X, provido pelo usuário, é X < 10. Nesse caso, o Bloco 2 lê uma região de memória escrita no Bloco 1. Dessa maneira, os dois blocos poderiam ser executados em paralelo, de maneira especulativa. Porém, caso seja detectado que X < 10, a execução do Bloco 2 precisaria ser descartada e reiniciada.

#### **Algoritmo 3.1:** Exemplo de execução especulativa – Bloco 1.

- 1: X = Entrada do Usuário

- 2: **if** X < 10 **then**

- 3: Escrever X na posição de memória 0x100

- 4: else

- 5: Escrever X na posição de memória 0x200

- 6: end if

#### **Algoritmo 3.2:** Exemplo de execução especulativa – Bloco 2.

1: Y = Leitura da posição de memória 0x100

# 3.11 Considerações finais

Este capítulo apresentou conceitos em paralelização automática e em teoria de ordem, pertinentes ao problema abordado. Apresentou-se também as opções de abordagens feitas neste trabalho. Em particular, por paralelização implícita, automática e sobre o binário compilado. Essa escolha visa minimizar o esforço necessário para realizar a paralelização,

permitindo que usuários com pouco ou nenhum domínio do problema possam se beneficiar de paralelismo em suas aplicações.

**Código 3.1:** Exemplo de instruções da arquitetura Intel x86.

#### main:

| push ebp          | 55       |

|-------------------|----------|

| xor eax, eax      | 31 C0    |

| mov ebp, esp      | 89 E5    |

| push edi          | 57       |

| cmp edx, 0FFFFF57 | 83 FA 57 |

CAPÍTULO

4

# Abordagem para a paralelização automática de aplicações

#### 4.1 Objetivo

O objetivo deste trabalho foi o de construir um conjunto de ferramentas que receba como entrada uma aplicação compilada para a arquitetura Intel x86, e fosse capaz de retornar uma aplicação equivalente com o máximo possível de estruturas paralelizadas automaticamente. A aplicação de saída deve preservar completamente a semântica da aplicação original, sendo equivalente em todas as entradas e saídas. Nesse sentido, o conjunto de ferramentas buscou analisar as dependências de instruções, detectar pontos passíveis de paralelização, e reconstruir a aplicação com as novas instruções obtidas. Para atingir o objetivo final, foram estabelecidas metas específicas, usando como base os estudos feitos anteriormente:

- Construir um desmontador para uma aplicação Intel x86 para transformação em uma linguagem intermediária;

- Construir um analisador capaz de gerar o grafo de fluxo de controle da aplicação;

- Construir um analisador capaz de gerar o grafo de dependências da aplicação;

- Construir um módulo que, automaticamente, elimine dependências quando aplicável;

- Construir um módulo que, com base no grafo final de dependências, fosse capaz de particionar o programa em unidades paralelas.

## 4.2 Metodologia empregada

Para atingir o objetivo proposto, as seguintes atividades foram planejadas e executadas: i) estudo da arquitetura Intel x86 (BENNETT, 2011); ii) implementação de um desmontador; iii) análise de fluxo de execução; iv) análise estática de dependências; v) particionamento dos grafos de dependência para obtenção de paralelismo; iv) remontagem de uma versão paralela da aplicação.

Iniciou-se com o estudo da arquitetura Intel x86, instruções e organizações típicas de aplicações. O objetivo dessa fase foi o de compreender as instruções da arquitetura, como é realizado o encoding em bytes e quais são as variações possíveis de acesso a registradores e memória. Além disso, estudou-se estruturas típicas de montagem da aplicação, de seu fluxo de execução, de estabelecimento e chamada de funções, para melhor compreensão das aplicações sendo abordadas. O foco desse estudo foram os principais compiladores em linguagem C disponíveis, para delinear as primeiras estratégias de paralelização. No entanto, deve-se ressaltar que o foco do trabalho não se restringe apenas à paralelização de aplicações criadas por esses compiladores. Esse estudo serve como um ponto de partida para uma generalização para qualquer aplicação escrita para a plataforma x86. Na etapa seguinte, projetou-se um desmontador (disassembler) para aplicações Intel x86 para, em seguida, obter uma abstração da aplicação. Essa abstração deve apresentar os acessos tanto à memória como a registradores, explicando se esses são relativos à escrita ou leitura. Deve-se também obter os pontos em que ocorrem saltos para outras regiões do programa, condicionais ou não, determinando sob quais circunstâncias eles ocorrem. Quando possível, funções devem ser delimitadas, determinando seu ponto de entrada e seus pontos de retorno. Nesse caso, todas as chamadas para cada função devem ser identificadas. Nota-se que, nesse momento, nem todas as chamadas podem ser identificadas, em particular nos casos em que as chamadas são dinâmicas. Esses casos são abordados nas próximas fases.

Como terceira etapa analisou-se o fluxo de execução das aplicações. Após a abstração ser obtida, o fluxo de execução deve ser obtido na forma de um grafo direcionado, o qual serve como base para análises subsequentes. Esse grafo consiste na sequência de instruções, em que cada vértice representa um bloco sequencial, e as arestas correspondem aos possíveis caminhos, especialmente em caso de desvios (*branching*) e laços de repetição. A seguir, foi conduzida uma análise estática sobre as dependências entre instruções. As dependências devem ser modeladas, também, na forma de um grafo, de acordo com o comportamento observado das instruções. A ideia é analisar cada instrução, tentandose obter os valores esperados em registradores/memória para aquele ponto da execução. Essa análise é estática, ou seja, leva apenas em consideração as instruções tal como obtidas na fase de desmontagem, sem que a aplicação seja executada. Essa análise deve ser feita de maneira a obter o grafo mais preciso possível, porém, entende-se que em uma

análise estática há limitações do que pode ser extraído. Em particular, é impossível saber o resultado de leituras de entrada e saída do sistema, como valores providos por usuários, conteúdo de arquivos, etc. Caminhos condicionais também dependem de condições, cujos valores, em geral, não estão disponíveis nessa etapa.

Em seguida, foram realizados particionamentos e modificações sobre o grafo de dependência entre instruções. Técnicas precisam ser aplicadas sobre tais grafos de forma a isolar grupos de vértices que podem ser executados em paralelo. Em particular, utilizou-se métodos de separação de grafos em anticadeias, descritos nas próximas seções. Ainda nesse sentido, buscou-se identificar pontos em que modificações permitiram aumentar o paralelismo do programa em questão.