#### Lucas Barbosa Sanches

## ChipCFlow - Partição e Protocolo de Comunicação no Grafo a Fluxo de Dados Dinâmico

#### Lucas Barbosa Sanches

## ChipCFlow - Partição e Protocolo de Comunicação no Grafo a Fluxo de Dados Dinâmico

Dissertação apresentada ao Instituto de Ciências Matemáticas e Computação - ICMC-USP, como parte dos requisitos para obtenção do título de Mestre em Ciências - Ciências de Computação e Matemática Computacional.

Orientador:

Prof. Dr. Jorge Luiz e Silva

## A grade cimentos

Em primeiro lugar, a Deus, por me conceder a bênção da saúde e do tempo para poder me dedicar a este trabalho. Ao meu orientador, professor Dr. Jorge, pela oportunide, e principalmente pela infinita paciência e apoio incondicional em todas as etapas, sem os quais não teria conseguido chegar até aqui. Ao Francisco, colega do mestrado que proporcionou as mais fecundas discussões em torno das questões do projeto. Sem ele este trabalho seria muitas vezes mais pobre. À Smar, empresa que me permitiu conduzir este trabalho de forma paralela à minha carreira profissional, sem prejuízo de um ou de outro. À minha esposa e à minha filha, que toleraram e apoiaram um marido e pai algumas vezes ausente, mas que nunca deixará de guardá-las com imenso amor no coração. Por fim, aos meus pais, alicerce fundamental sobre o qual pude sempre construir com tranquilidade e firmeza. Se pude chegar a algum lugar, devo isso a eles.

## Resumo

Este trabalho descreve a prova de conceito de uma abordagem que utiliza o modelo de computação a fluxo de dados, inerentemente paralelo, associado ao modelo de computação reconfigurável parcial e dinamicamente, visando à obtenção de sistemas computacionais de alto desempenho. Mais especificamente, trata da obtenção de um modelo para o particionamento dos grafos a fluxo de dados dinâmicos e de um protocolo de comunicação entre suas partes, a fim de permitir a sua implementação em arquiteturas dinamicamente reconfiguráveis, em especial em FGPAs Virtex da Xilinx. Enquadra-se no contexto do projeto *ChipCFlow*, de escopo mais amplo, que pretende obter uma ferramenta para geração automática de descrição de *hardware* sintetizável, a partir de código em alto nível, escrito em linguagem C, fazendo uso da abordagem a fluxo de dados para extrair o paralelismo implícito nas aplicações originais. O modelo proposto é aplicado em um grafo a fluxo de dados dinâmico, e através de simulações sua viabilidade é discutida.

### Abstract

This work describes the concept of an approach that uses dataflow computational model, inherently parallel, associated with de reconfigurable computing model, partial and dynamic, in order to obtain high performance computational systems. More specifically, it is about a model to the partitioning and communication between partitioned sectors of a CDFG (Control Dataflow Graph) in order to map these graphs on a partial reconfiguration FPGA fabric, in special Virtex II/II-Pro from Xilinx. It is part of the *ChipCFlow* project, that has a bigger scope, and that aims to automatically obtain syntetisable hardware descriptions, from high level code written in C and, by using a dataflow approach to extract implicit parallelism in original applications. The model obtained is extensively explained and applied to an example of CDFG, where by means of simulations its feasibility is discussed.

## Sum'ario

#### Lista de Figuras

| 1        | Intr | oduçã  | 0           |                                                          | p. 17 |

|----------|------|--------|-------------|----------------------------------------------------------|-------|

|          | 1.1  | Objet  | ivos do tra | abalho                                                   | p. 19 |

|          | 1.2  | Organ  | ização da   | dissertação                                              | p. 19 |

| <b>2</b> | Con  | nputaç | ção a Flu   | ixo de Dados                                             | p. 21 |

|          | 2.1  | Ciclos | , iterações | s e reentrância em grafos a fluxo de dados               | p. 25 |

|          | 2.2  | Arqui  | teturas tra | adicionais a fluxo de dados                              | p. 27 |

|          |      | 2.2.1  | Máquina     | as a fluxo de dados estáticas                            | p. 29 |

|          |      | 2.2.2  | Máquina     | as a fluxo de dados dinâmicas                            | p. 30 |

|          |      |        | 2.2.2.1     | A máquina de Manchester ((GURD; KIRKHAM; WATSON, 1985))  | p. 31 |

|          |      |        | 2.2.2.2     | A arquitetura Tagged-token do MIT (ARVIND; NIKHIL, 1990) | p. 33 |

|          | 2.3  | Arqui  | teturas mo  | odernas inspiradas no modelo a fluxo de dados            | p. 33 |

|          |      | 2.3.1  | Wavesca     | lar(SWANSON et al., 2007)                                | p. 34 |

|          |      | 2.3.2  | TRIPS (     | (BURGER et al., 2004)                                    | p. 37 |

| 3        | Con  | nputaç | ção Reco    | nfigurável                                               | p. 41 |

|          | 3.1  | Arqui  | teturas de  | computação reconfigurável                                | p. 42 |

|          |      | 3.1.1  | Primeiro    | os sistemas de computação reconfigurável                 | p. 43 |

|          |      |        | 3.1.1.1     | MATRIX (MIRSKY; DEHON, 1996)                             | p. 44 |

|   |     |         | 3.1.1.2    | RAW (WAINGOLD et al., 1997)                                     | p. 44 |

|---|-----|---------|------------|-----------------------------------------------------------------|-------|

|   |     |         | 3.1.1.3    | RaPiD(EBELING; CRONQUIST; FRANKLIN, 1996)                       | p. 45 |

|   |     |         | 3.1.1.4    | Firefly(GOEKE et al., 1997)                                     | p. 45 |

|   |     |         | 3.1.1.5    | SPLASH-II(GOKHALE et al., 1990)                                 | p. 46 |

|   |     |         | 3.1.1.6    | DECPeRLe-1(VUILLEMIN et al., 2002)                              | p. 46 |

|   |     |         | 3.1.1.7    | PRISM(ATHANAS; SILVERMAN, 1993)                                 | p. 47 |

|   |     |         | 3.1.1.8    | GARP(Hauser; Wawrzynek, 1997)                                   | p. 47 |

|   |     | 3.1.2   | Sistemas   | mais recentes de computação reconfigurável                      | p. 48 |

|   |     |         | 3.1.2.1    | PACT XPP(BAUMGARTE et al., 2003)                                | p. 49 |

|   |     |         | 3.1.2.2    | NEC DRP                                                         | p. 50 |

|   |     |         | 3.1.2.3    | picoCHIP                                                        | p. 51 |

|   | 3.2 | Arquit  | etura dos  | FPGAS                                                           | p. 51 |

|   |     | 3.2.1   | Tecnolog   | ias de configuração dos FPGAs                                   | p. 53 |

|   |     |         | 3.2.1.1    | Antifuse                                                        | p. 54 |

|   |     |         | 3.2.1.2    | Memória                                                         | p. 54 |

|   | 3.3 | Reconf  | iguração j | parcial em FPGAs Xilinx                                         | p. 55 |

|   |     | 3.3.1   |            | ros e comunicação interna em sistemas parcialmente re-<br>iveis | p. 60 |

| 4 | Ор  | rojeto  | Chip CF    | low                                                             | p. 63 |

|   | 4.1 | Mapea   | mento do   | s grafos dinâmicos em FPGAs parcialmente reconfiguráveis        | p. 63 |

|   |     | 4.1.1   | ChipCFle   | ow: fluxo de projeto                                            | p. 66 |

| 5 | Mod | delo de | Particio   | onamento e Protocolo de Comunicação                             | p. 71 |

|   | 5.1 | O mod   | lelo de pa | rticionamento                                                   | p. 74 |

|   | 5.2 | Comur   | nicação .  |                                                                 | p. 75 |

|   |     | 5.2.1   | Controla   | dor e canal de comunicação                                      | p. 76 |

|   |     | 5.2.2   | Protocolo  | 0                                                               | p. 80 |

|                  |       | 5.2.3 Gerência de reconfiguração | p. 82 |

|------------------|-------|----------------------------------|-------|

|                  | 5.3   | Exemplo de aplicação             | p. 83 |

| 6                | Cor   | nclusão                          | p. 85 |

| Re               | eferê | ências                           | p. 87 |

| $\mathbf{A}_{1}$ | nexo  |                                  | р. 91 |

# Lista de Figuras

| 1  | Representação na forma de um grafo a fluxo de dados da computação de $A = (B-C)^*(D+E)  \dots  \dots  \dots  \dots  \dots$                                                                                                                                                                   | p. 21 |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 2  | Grafo a fluxo de dados incorporando operadores de controle de fluxo (adaptado de (ARVIND; CULLER, 1986))                                                                                                                                                                                     | p. 22 |

| 3  | Operadores Decider e Branch, respectivamente                                                                                                                                                                                                                                                 | p. 23 |

| 4  | Operadores <i>Deterministic merge</i> , <i>non-deterministic merge</i> e <i>copy</i> . Através destes operadores há a criação ou eliminação de dados durante a execução de um grafo                                                                                                          | p. 24 |

| 5  | Operador funcional hipotético. Tradicionalmente é implementado um operador para cada função lógica ou aritmética básica                                                                                                                                                                      | p. 24 |

| 6  | Problemas com estruturas cíclicas: o grafo da esquerda (a) fica em deadlock, o da direita (b) nunca termina de executar                                                                                                                                                                      | p. 25 |

| 7  | Uma maneira insegura de implementar um loop                                                                                                                                                                                                                                                  | p. 26 |

| 8  | Loop seguro usando branch composto (VEEN, 1986))                                                                                                                                                                                                                                             | p. 27 |

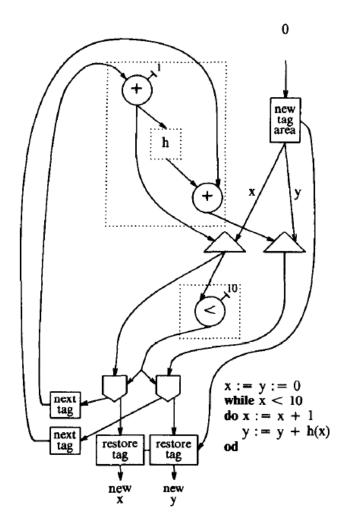

| 9  | Uma implementação de um loop usando tagged tokens. No início do loop um novo tag é alocado (definindo uma nova área de tokens). Tokens de iterações consecutivas recebem tags indicando pertencerem a esta área. O tag anterior ao loop é restaurado em tokens que saem do loop (VEEN, 1986) | p. 28 |

| 10 | Organização básica de uma máquina fluxo de dados estática((LEE; HURSON, 1993))                                                                                                                                                                                                               | p. 29 |

| 11 | Formato de instrução de uma máquina fluxo de dados estática                                                                                                                                                                                                                                  | p. 29 |

| 12 | Esquema geral de uma arquitetura a fluxo de dados dinâmica. (LEE; HURSON, 1993)                                                                                                                                                                                                              | p. 30 |

| 13 | Visão geral da arquitetura de Manchester                                                                                                                                                                                                                                                     | p. 32 |

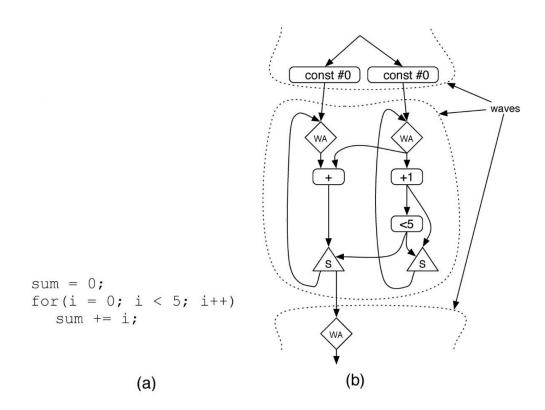

| 14 | Um loop simples (a) e sua implementação em WaveScalar (b) (adaptado de (SWANSON et al., 2007))                                                                                                                                                                                                 | p. 35 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 15 | Chamada de função em WaveScalar                                                                                                                                                                                                                                                                | p. 36 |

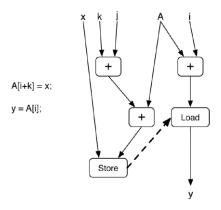

| 16 | A linha tracejada representa uma potencial dependência de dados implícita entre as instruções load e store(SWANSON et al., 2007)                                                                                                                                                               | p. 37 |

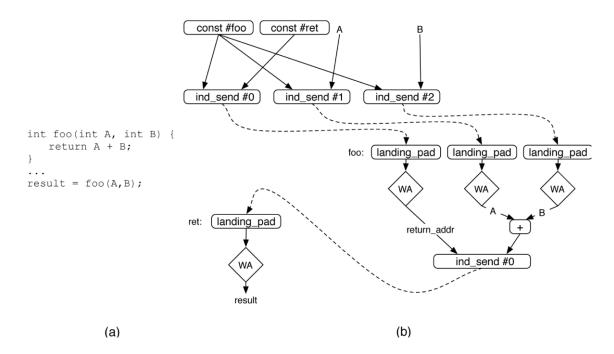

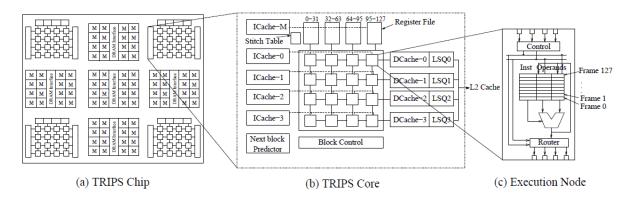

| 17 | Visão geral da arquitetura TRIPS. Retirado de (SANKARALINGAM et al., 2003)                                                                                                                                                                                                                     | p. 38 |

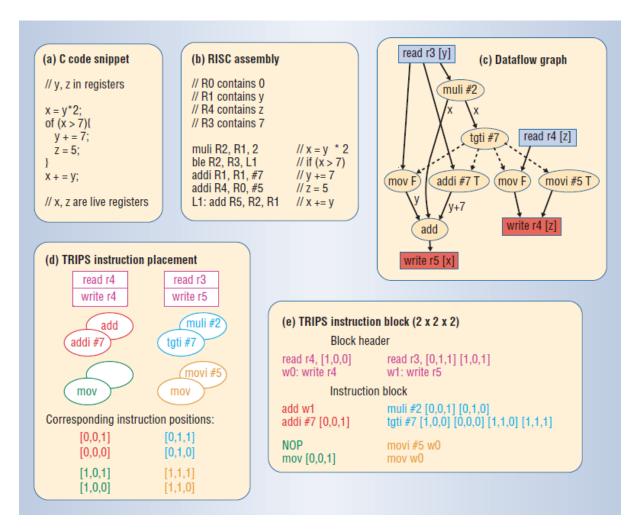

| 18 | Geração de código para o TRIPS(SANKARALINGAM et al., 2003)                                                                                                                                                                                                                                     | p. 39 |

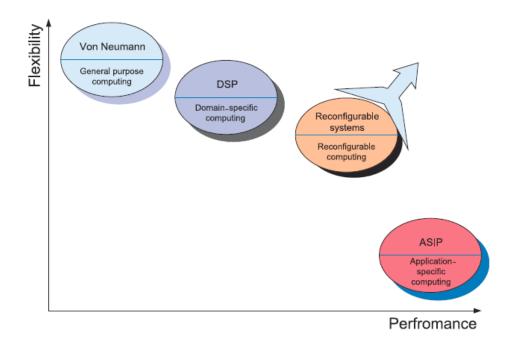

| 19 | Gráfico mostrando a relação desempenhoxflexibilidade para as classes de máquinas computacionais                                                                                                                                                                                                | p. 42 |

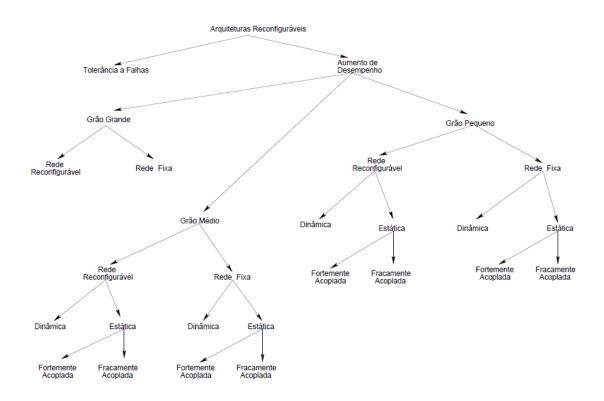

| 20 | Classificação de (RADUNOVIC; MILUTINOVIC, 1998) em forma de árvore (retirado de (MESQUITA, 2002))                                                                                                                                                                                              | p. 43 |

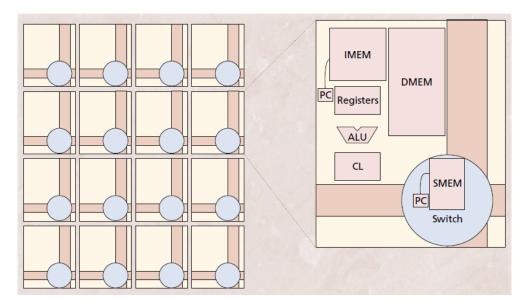

| 21 | Um processador RAW é construído de múltiplos blocos idênticos. Cada bloco contém memória de instrução (IMEM), memória de dados (DMEM), unidade aritmética e lógica (ALU), registradores, lógica configurável(CL) e um <i>switch</i> programável associado com sua memória de instrução (SMEM). | p. 45 |

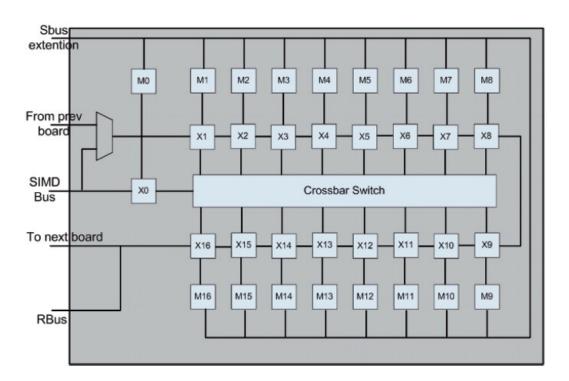

| 22 | Arquitetura SPLASH-II.(retirado de (BOBDA, 2007))                                                                                                                                                                                                                                              | p. 46 |

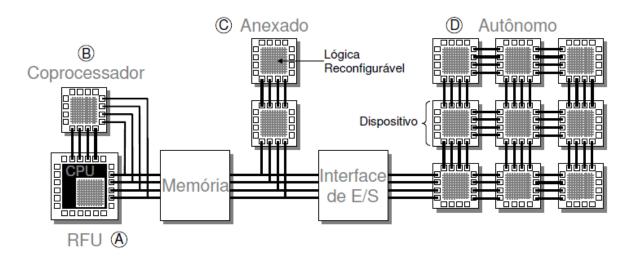

| 23 | Posicionamento da lógica programável em arquiteturas de computação reconfigurável ((HAUCK, 1998))                                                                                                                                                                                              | p. 48 |

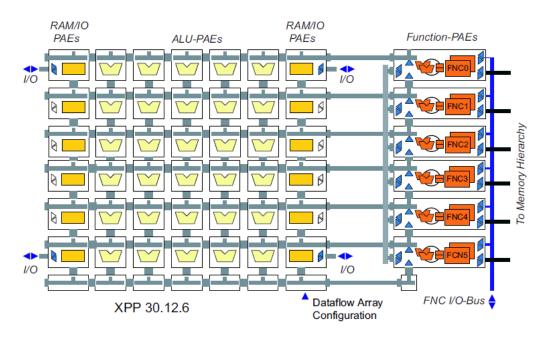

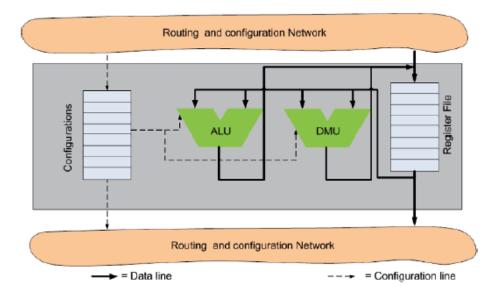

| 24 | Arquitetura PACT XPP-III                                                                                                                                                                                                                                                                       | p. 49 |

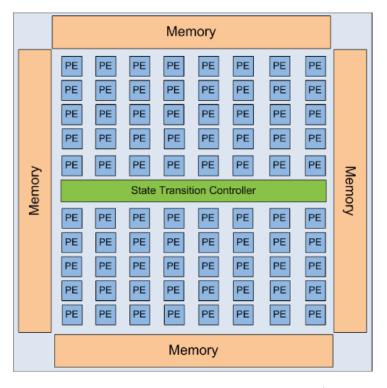

| 25 | Arquitetura DRP da NEC. Retirado de (BOBDA, 2007)                                                                                                                                                                                                                                              | p. 51 |

| 26 | Um elemento de processamento da arquitetura DRP. Retirado de (BOBDA, 2007)                                                                                                                                                                                                                     | p. 52 |

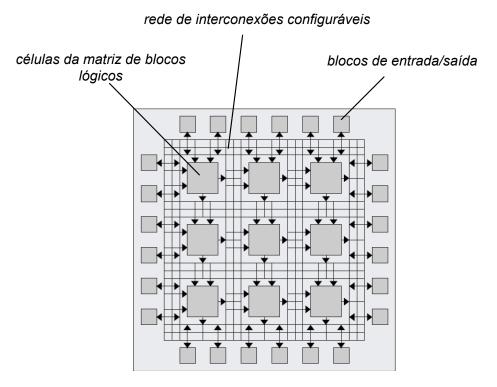

| 27 | Visão abstrata da arquitetura de um FPGA (adaptado de (HAUCK; DEHON, 2008))                                                                                                                                                                                                                    | p. 53 |

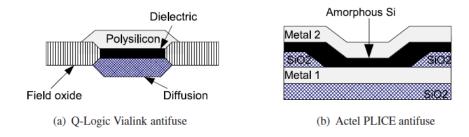

| 28 | Tecnologias antifuse. Em (a), Vialink, da empresa QuickLogic; em (b), PLACE, da Actel.(BOBDA, 2007)                                                                                                                                                                                            | p. 54 |

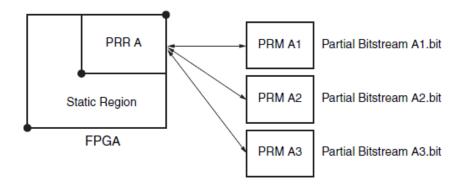

| 29 | Uma região parcialmente reconfigurável (PRR) A pode ser carregada com os módulos parcialmente reconfiguráveis A1, A2, A3                                                                                                                                                                       | p. 56 |

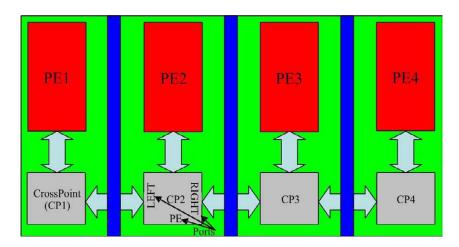

| 30 | Divisão de um FPGA utilizando o sistema de comunicação RMBoC.<br>Retirado de (AHMADINIA et al., 2005)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | p. 60 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 31 | Um $crosspoint$ do sistema RMBoC (retirado de (BOBDA, 2007))                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | p. 61 |

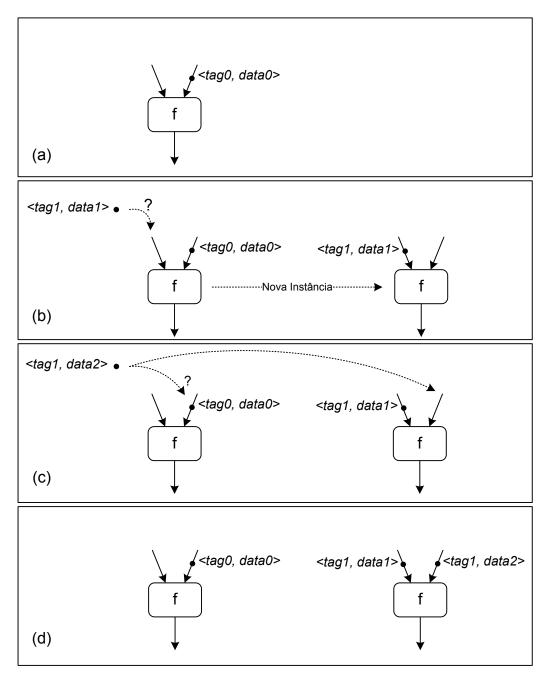

| 32 | Evolução de um operador no modelo de instâncias. Em (a) o operador aguarda em seu segundo arco um operador com o mesmo tag do primeiro. Em (b) um novo dado chega, porém de tag diferente, provocando a instanciação de um novo operador(c). Em (d) um dado com o tag igual ao da segunda instância chega, e o matching é bem sucedido. A segunda instância está habilitada a disparar                                                                                                                                                                                                                                                                                                                                                                                                                             | p. 64 |

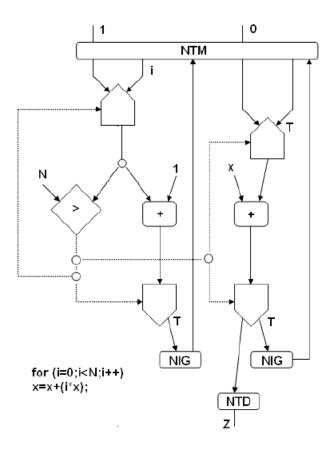

| 33 | Um grafo $dataflow$ dinâmico com os operadores de $tag$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | p. 66 |

| 34 | Originalmente o projeto Chip<br>CFlow previa um operador por $\ensuremath{PRR}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | p. 67 |

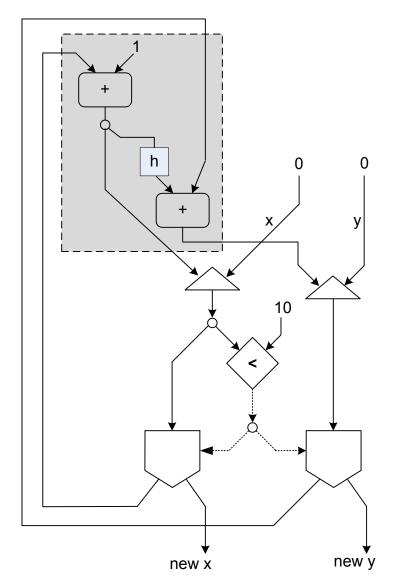

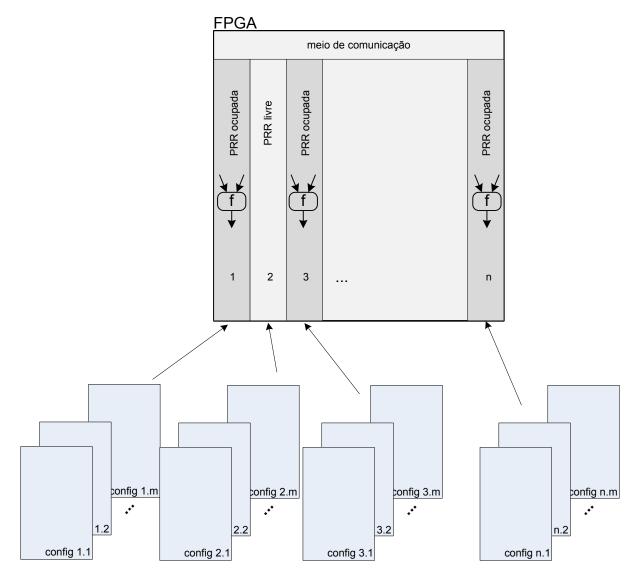

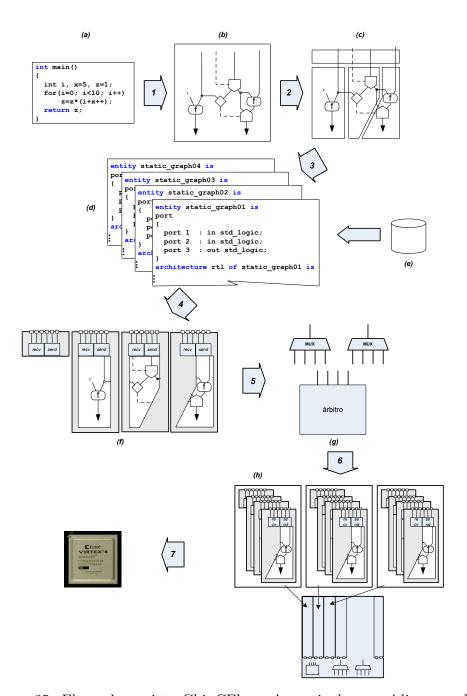

| 35 | Fluxo de projeto ChipCFlow. A partir de um código em alto nível (a), obtém-se uma representação do programa em CDFG(b). O grafo é então particionado(c), e a partir de cada partição gera-se uma descrição VHDL para cada subgrafo estático(d). A cada subgrafo estático são adicionados controladores de comunicação(4), obtendo-se a descrição completa de cada partição(f). Além dos elementos de comunicação de cada partição, os elementos estáticos são adicionados(g). O projeto nas ferramentas EDA associa a cada PRR a possibilidade de conter qualquer uma das partições como configuração(h) e posiciona também os elementos estáticos fora das PRRs e ligados a elas pelas bus-macros. O projeto é compilado de acordo com as regras das ferramentas, obtendo-se os bits-treams finais de programação | p. 68 |

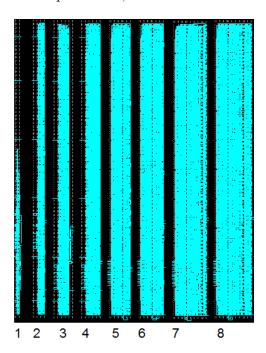

| 36 | Alocação de colunas do FPGA em partições com diferentes números de operadores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | p. 72 |

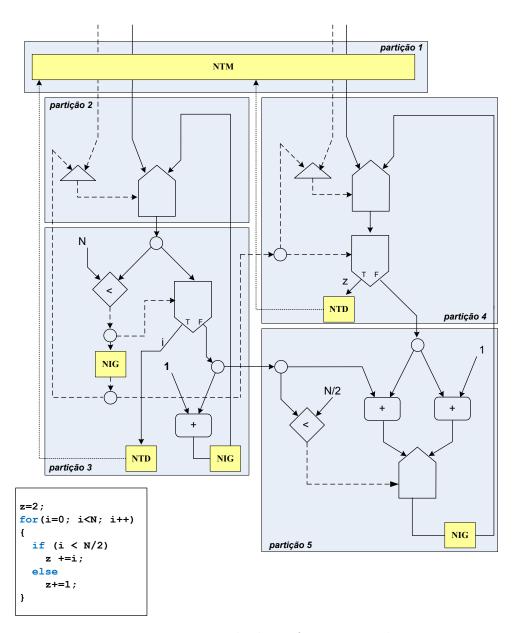

| 37 | Exemplo de grafo particionado                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | p. 75 |

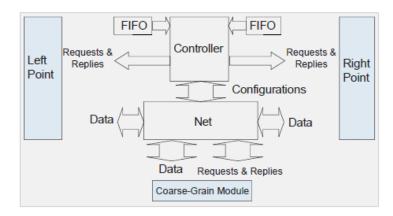

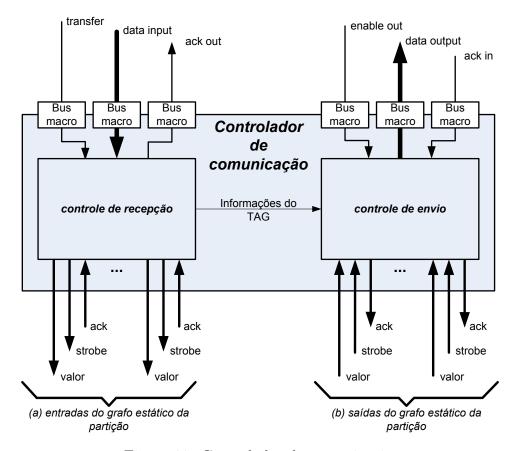

| 38 | Controlador de comunicação                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | p. 77 |

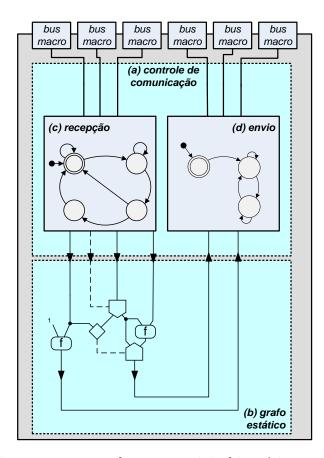

| 39 | Diagrama mostrando uma partição hipotética composta de seu grafo estático e seu controlador de comunicação                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | p. 78 |

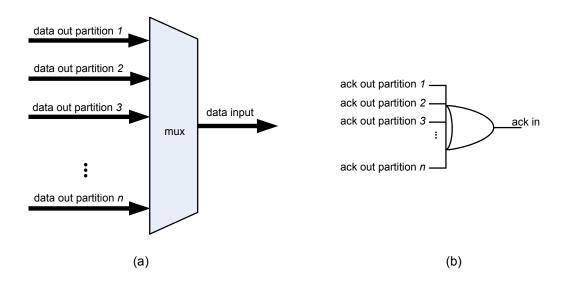

| 40 | Elementos de interligação entre as partições que compõem o canal de comunicação. Em (a) um multiplexador dos dados; em (b) uma porta lógica OU para a indicação de recebimento de um quadro válido $(matching)$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | p. 79 |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |

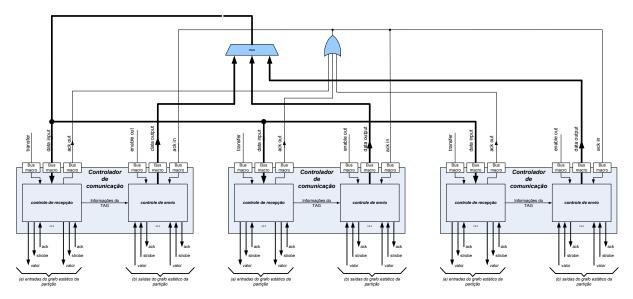

| 41 | Exemplo de interligação dos controladores de comunicação de três partições           |       |

|----|--------------------------------------------------------------------------------------|-------|

|    | com o canal de comunicação. O multiplexador e a porta lógica que se                  |       |

|    | vêem ao alto são posicionados em uma região estática, enquanto a cada                |       |

|    | PRR associa-se uma partição                                                          | p. 80 |

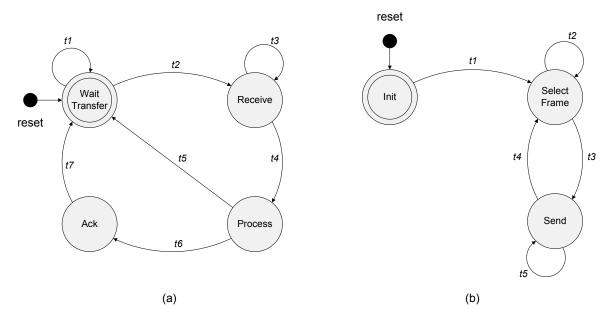

| 42 | Máquinas de estado dos submódulos de recepção (a) e envio (b) do con-                |       |

|    | trolador de comunicação                                                              | p. 81 |

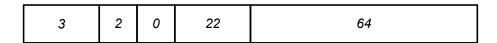

| 43 | Quadro de comunicação                                                                | p. 81 |

| 44 | Exemplo de quadro trocado entre uma partição e outra, carregando um                  |       |

|    | token e seu tag                                                                      | p. 82 |

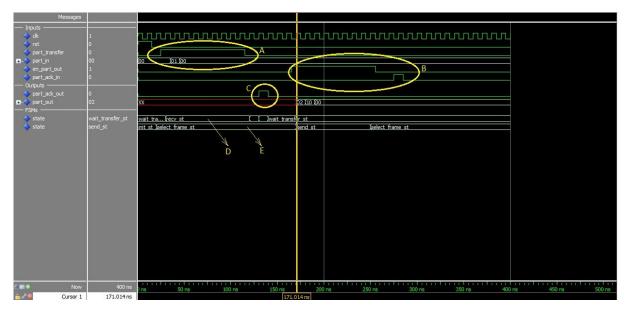

| 45 | Tela de uma das simulações realizadas para verificar a implementação do              |       |

|    | gerenciador de comunicação na partição 1. Em (A) observa-se a janela                 |       |

|    | de transferência em que o controle de recepção recebe um <i>token</i> . Após a       |       |

|    | recepção completa, o sinal de $acknowledge$ out é ativado (C). Em (B) vê-            |       |

|    | se o sinal de habilitação de envio e posteriormente o sinal de $acknowledge$         |       |

|    | $\mathit{in},$ indicando que o pacote foi recebido. Em (D) e (E) é possível observar |       |

|    | os estados das máquinas de recepção e de envio, conforme apresentado                 |       |

|    | na seção 5.2.1                                                                       | p. 84 |

## 1 Introdução

O modelo de computação a fluxo de dados sempre despertou interesse como área de pesquisa por sua elegância ao extrair e representar de maneira simples o paralelismo presente em tarefas de computação. Houve muitas tentativas no passado de se implementar máquinas de propósito geral baseadas no modelo. No entanto, as dificuldades para se obter uma máquina a fluxo de dados de propósito geral sempre se mostraram enormes (LEE; HURSON, 1993). Já a partir do final da década de 80 o interesse pelo assunto parecia estar diminuindo, como mostram, por exemplo, as estatísticas em (NAJJAR; LEE; GAO, 1999). No entanto, devido ao seu potencial, o modelo nunca deixou totalmente de levantar interesse da comunidade científica.

Embora as pesquisas não tenham levado a uma arquitetura de propósito geral largamente comercial, o modelo a fluxo de dados é amplo o suficiente para ser aplicado em diversas áreas, como linguagens de programação, projeto de processadores, processamento digital de sinais e, mais recentemente, computação reconfigurável (NAJJAR; LEE; GAO, 1999) (COMPTON; HAUCK, 2002).

A computação reconfigurável, por sua vez, apesar de estar embasada em conceitos que não são novos, definiu-se mais claramente como área de pesquisa graças ao grande avanço das tecnologias de fabricação de circuitos integrados ocorrido nas últimas décadas, os quais permitiram o surgimento e a evolução dos FPGAs (Field Programmable Gate Arrays) ou matrizes de portas programáveis em campo. De acordo com (COMPTON; HAUCK, 2002) atualmente quando a expressão computação reconfigurável é usada, refere-se a sistemas que incorporam algum tipo de capacidade de programação de hardware utilizando certo número de pontos de controle que podem ser alterados, e que configuram como este hardware é usado. FPGAs e CPLDs são exemplos de dispositivos que concretizam esse conceito em um único circuito integrado.

Eles possibilitam a flexibilidade de se obter *hardware* específico para determinada aplicação de maneira rápida e barata. Rápida e barata por não exigir que este *hard*-

1 Introdução

ware projetado seja fabricado, como circuito integrado de aplicação específica (ASIC - Application-specific integrated circuit), mas possa simplesmente ser carregado em campo, ou seja, no momento do uso, como uma configuração de um FPGA.

Normalmente, o circuito digital projetado é definido em uma linguagem de descrição de hardware (HDL - Hardware Description Language), sendo VHDL e Verilog as mais comumente usadas. Ferramentas de software adequadas sintetizam o circuito projetado, ou seja, obtêm a configuração correspondente a partir da entrada em linguagem de descrição.

Essa tecnologia permite, assim, a prototipação rápida de circuitos de propósito específico, sem a necessidade da fabricação. Além disso, abre campo para inúmeras outras aplicações.

Os FPGAs atuais agregam até milhões de portas lógicas, podendo ser usados para implementar, em um único circuito integrado, desde aplicações simples de lógica digital até sistemas inteiros, compostos de um processador (ou mais de um) e todos os seus periféricos necessários. Estes últimos conhecidos como SoCs - System on a Programmable Chip.

Além da possibilidade de se obter sistemas em *hardware* de grande complexidade para propósitos específicos de maneira rápida e barata, o que é de grande interesse para a indústria eletrônica e de computação em geral, os FPGAs fomentaram campos novos de pesquisa. Um desses campos é o que busca obter descrições de *hardware* eficientes a partir de programação em alto nível. Há ferramentas comerciais, como as citadas em (LOPES, 2007), que geram descrição de *hardware* que implementa algoritmos definidos a partir de linguagem de alto nível, como C, por exemplo.

Com essas novas possibilidades abertas, a computação reconfigurável, indiretamente, deu novo fôlego às pesquisas relacionadas ao modelo de computação a fluxo de dados. A fim de fazer uso do imenso potencial de paralelismo real oferecido pelas tecnologias de computação reconfigurável, o modelo a fluxo de dados se mostra bastante promissor, e é usado em algumas das ferramentas citadas anteriormente como representação intermediária, visando extrair o paralelismo implícito na codificação em alto nível. Foi revisitado também, em pesquisas de arquiteturas de processadores novas e bastante promissoras, como TRIPS e Wavescalar.

Este trabalho se enquadra neste contexto, e faz parte do projeto ChipCFlow, que tem por objetivo obter uma ferramenta de compilação capaz de gerar descrição de *hardware* a partir de código de alto nível (linguagem C) e que utilize como representação inter-

mediária o modelo a fluxo de dados dinâmico, visando extrair ao máximo o paralelismo de granularidade fina intrínseco ao código.

Numa primeira etapa do projeto, foram obtidos os operadores usados nos grafos a fluxo de dados do projeto (ASTOLFI; SILVA, 2007).

Numa segunda etapa, pretende-se obter implementações de grafos dinâmicos, fazendo uso de características de reconfiguração parcial dos FPGAs.

### 1.1 Objetivos do trabalho

A idéia de mapear grafos a fluxo de dados dinâmicos em FPGAs parcialmente reconfiguráveis é um dos pontos centrais do projeto ChipCFlow. Um dos objetivos deste trabalho é apresentar uma cadeia consistente e completa para o mapeamento dos grafos a fluxo de dados dinâmicos, incluindo seus operadores de tag, em FPGAs parcialmente reconfiguráveis. Consistente no sentido de garantir que o sistema execute de acordo com o modelo a fluxo de dados dinâmico, sem deadlocks, e completo no sentido de cobrir toda a cadeia de desenvolvimento para se obter o sistema final, tomando como ponto de partida os grafos dinâmicos obtidos por compilação. Esta é uma grande contribuição para o projeto. Para atingir o objetivo de mapear os grafos dinâmicos em uma arquitetura de FPGA parcialmente reconfigurável, é apresentado um modelo para o particionamento dos grafos e a comunicação entre suas partições. A proposta será aplicada a um exemplo, visando analisar suas características.

Não faz parte do escopo deste trabalho qualquer preocupação com a obtenção dos grafos a partir dos códigos em alto nível. Apenas admite-se que os grafos são entradas e que a saída é um sistema parcialmente reconfigurável que os implemente.

#### 1.2 Organização da dissertação

No capítulo 2, são apresentados os conceitos e principais arquiteturas tradicionais e modernas que fazem uso do modelo de computação a fluxo de dados. As informações apresentadas são essenciais para o embasamento do projeto ChipCFlow.

No capítulo 3 é feito um levantamento das tecnologias envolvidas no campo da computação reconfigurável, bem como das principais arquiteturas baseadas nela. É apresentada, também, a tecnologia para reconfiguração parcial da Xilinx, primeiro fabricante a

20 1 Introdução

fornecer dispositivos e ferramentas para essa nova tecnologia, ainda experimental.

O capítulo 4 apresenta em maiores detalhes o projeto ChipCflow, principalmente no que tange ao seu conceito de mapeamento dos grafos a fluxo de dados dinâmicos (CDFG) em FPGAs parcialmente reconfiguráveis.

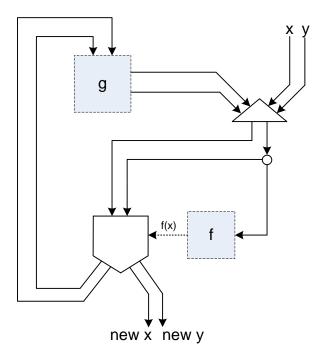

No capítulo 5 é proposto um modelo para o particionamento e para o sistema de comunicação entre as partições previstas para os grafo a fluxo de dados dinâmicos do projeto. A implementação e simulação do modelo para um exemplo específico é mostrada, visando provar a viabilidade da proposta apresentada.

Por fim, o capítulo 6 traz discussões e conclusões a respeito do trabalho, além de propor um caminho para o projeto ChipCFlow a partir dos resultados.

## 2 Computação a Fluxo de Dados

O modelo de computação a fluxo de dados é um modelo de computação simples e poderoso, especialmente na representação do paralelismo em diversas tarefas de computação. Ele está baseado na idéia de que uma operação de computação, para ser executada, necessita apenas de que seus operandos estejam disponíveis num determinado instante. Dessa maneira, diversas operações podem ser executadas simultaneamente.

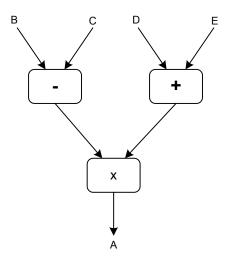

Neste modelo, os programas são grafos orientados cujos nós (em alguns casos chamados de atores (NAJJAR; LEE; GAO, 1999)) definem operações, e os arcos, a relação entre as operações, indicando a origem e o destino dos dados (também chamados de tokens). Como exemplo, o grafo da Figura 1 representa a computação A = (B - C) \* (D + E).

Figura 1: Representação na forma de um grafo a fluxo de dados da computação de A = (B-C)\*(D+E)

No modelo, os dados, ou *tokens*, transitam entre os operadores através dos arcos. Todo operador possui arcos de entrada e arcos de saída. Desde que todos os dados necessários nas entradas estejam disponíveis, o operador executa (dispara) e gera *tokens* nos seus arcos de saída, consumindo os *tokens* de suas entradas. Dessa forma, as operações de subtração e de soma indicadas na Figura 1, por exemplo, podem ser executadas paralelamente.

Em arquiteturas a fluxo de dados não existe o conceito de uma memória global nem de um contador de programa (program counter), como nas arquiteturas Von Neumann tradicionais, e o controle das operações está distribuído entre os nós do grafo. O modelo potencialmente permite, como mostrado no exemplo anterior, extrair de maneira natural o paralelismo dos algoritmos, além de fornecer um mecanismo simples de sincronização entre as operações.

Figura 2: Grafo a fluxo de dados incorporando operadores de controle de fluxo (adaptado de (ARVIND; CULLER, 1986))

O modelo a fluxo de dados em princípio não define restrições para a complexidade dos operadores, cabendo aos projetistas de determinada arquitetura esta definição.

O grafo apresentado na Figura 1 é um grafo simples, que possui apenas operadores lógico matemáticos. Além desses operadores há os de controle e de decisão, que geram tokens que controlam o fluxo de dados em outros operadores. Em geral, as arestas que

conduzem estes tokens são representadas por linhas tracejadas, como forma de diferenciação (Figura 2).

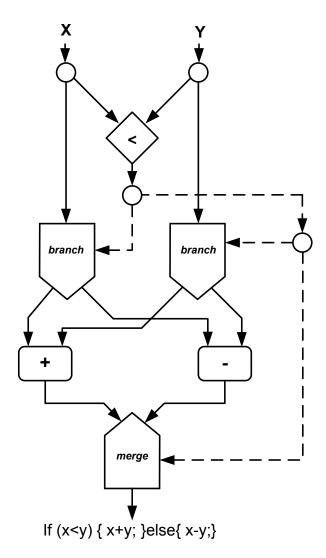

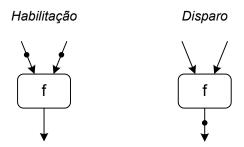

No modelo adotado neste trabalho os nós podem pertencer a três classes: condicionais, de cópia e junção, ou funcionais. Entre os primeiros estão dois operadores: o de decisão (decider) e o de ramificação (branch). A Figura 3 ilustra os dois operadores antes e depois do disparo, enquanto a Figura 2 mostra um grafo simples que faz uso desses operadores.

Figura 3: Operadores *Decider* e *Branch*, respectivamente.

O operador de decisão recebe dois valores e quando habilitado gera um dado (token) booleano verdadeiro ou falso de acordo com a aplicação de uma função aos dados de entrada.

O operador de ramificação, por sua vez, recebe um *token* em sua entrada que é direcionado para uma ou outra aresta de saída de acordo com um *token* de controle recebido em outra entrada.

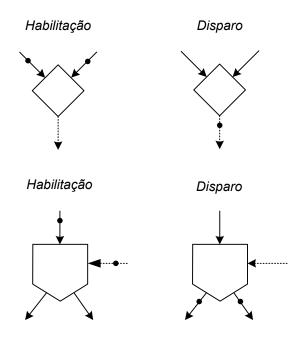

Como operadores de cópia e junção tem-se os operadores junção determinística por valor (deterministic merge), junção não determinística (non-deterministic merge) e o operador de cópia (copy). A Figura 4 ilustra os três operadores antes e depois de seu disparo.

O operador de junção determinística recebe um valor de controle que seleciona uma ou outra entrada para ser colocada em sua saída após a sua habilitação. O operador de junção não determinística coloca em sua saída o primeiro dos dois valores possíveis que receber em suas entradas. O operador de cópia, por sua vez, duplica um dado recebido

Figura 4: Operadores *Deterministic merge*, non-deterministic merge e copy. Através destes operadores há a criação ou eliminação de dados durante a execução de um grafo.

em sua entrada para as suas duas saídas.

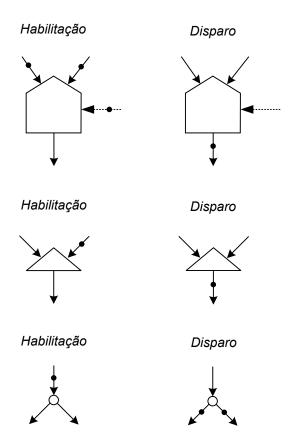

Figura 5: Operador funcional hipotético. Tradicionalmente é implementado um operador para cada função lógica ou aritmética básica

Os operadores funcionais (Figura 5) são os que efetivamente realizam as operações de computação desejadas com os dados. Os mais comuns são aqueles que implementam as operações lógicas e aritméticas básicas, como soma, subtração, 'e', 'ou', 'não', etc. No entanto, como afirmado anteriormente, a princípio não há restrições no modelo a fluxo de dados para a complexidade do operador.

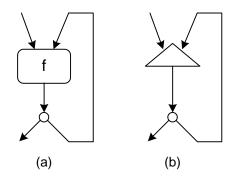

# 2.1 Ciclos, iterações e reentrância em grafos a fluxo de dados

Quando um grafo contém ciclos, é possível que alguns problemas sejam originados. No grafo hipotético (a) da Figura 6 tem-se uma situação que gera um deadlock, enquanto em (b) tem-se uma situação em que o grafo não termina de executar nunca. As situações deste exemplo (VEEN, 1986), podem ocorrer em qualquer grafo cíclico, a menos que precauções especiais sejam tomadas.

Figura 6: Problemas com estruturas cíclicas: o grafo da esquerda (a) fica em *deadlock*, o da direita (b) nunca termina de executar.

A Figura 7 mostra um exemplo de grafo cíclico, e a computação que implementa.

Trata-se de um *loop* implementado de forma insegura. Neste exemplo, é possível que um novo *token* chegue ao subgrafo 'h' antes de o primeiro ter sido processado.

Esta ocorrência é chamada de reentrância, e a forma que uma determinada arquitetura baseada no modelo a fluxo de dados lida com ela é um conceito fundamental(VEEN, 1986).

Uma forma de resolver a questão da reentrância é através do método da fechadura (lock method). Um exemplo de grafo cíclico seguro, que usa este método, está ilustrado na Figura 8.

Esta abordagem exige a inserção de novos operadores: o branch composto e o merge composto. Através do uso adequado destes operadores garante-se o determinismo do grafo. Eles fazem o sincronismo adequado dos dados, evitando a ocorrência de múltiplos tokens em uma entrada do subgrafo 'g' 8, e mantêm a condição de disparo estrita, ou seja, disparam apenas quando todos os tokens em suas entradas estiverem presentes.

Uma outra forma de lidar com a situação da reentrância é o uso de arcos de acknowledge (reconhecimento) entre os operadores produtores e consumidores. Este método garante que cada arco de um grafo armazene apenas um token em um determinado mo-

Figura 7: Uma maneira insegura de implementar um loop.

mento, mantendo o seu determinismo. Os produtores aguardam até que os consumidores sinalizem através do arco de reconhecimento o recebimento do *token*, e só então o produtor está apto a enviar novos *tokens*. Esta abordagem permite uma concorrência maior que o método da fechadura, ao custo de o número de arcos e *tokens* no mínimo dobrar.

No entanto, é interessante que se possibilite um maior nível de concorrência, permitindo que as iterações dos laços sejam executadas paralelamente. Uma forma de se conseguir isso é utilizando arquiteturas que de algum modo permitam cópia de código. Nesta abordagem, novas instâncias do grafo reentrante são criadas para cada iteração dos laços (loops) e a arquitetura precisa prover algum mecanismo de os tokens serem direcionados para a sua instância corretamente.

Uma segunda solução potencialmente mais eficiente de implementar a cópia de código

Figura 8: Loop seguro usando branch composto (VEEN, 1986)).

é alcançada através de arquiteturas que compartilham a estrutura do grafo reentrante original, mas distingue os dados de cada iteração através de uma etiqueta (tag), que define a qual instância um token pertence. Uma mudança é realizada na regra de disparo: aqui, para disparar, um operador precisa receber dados de um mesmo tag em suas entradas. Essas são as arquiteturas tagged-token.

A Figura 9 ilustra como a característica dos tags aparece em um programa para arquiteturas deste tipo. Além dos operadores tradicionais, outros que modificam tags estão presentes.

### 2.2 Arquiteturas tradicionais a fluxo de dados

Tradicionalmente a forma pela qual uma máquina a fluxo de dados lida com a reentrância define sua classificação como estática ou dinâmica. Aquelas que tratam a reentrância através de travamento ou de operadores com reconhecimento estão entre as primeiras, enquanto aquelas com mecanismos de cópia de código ou *tagged-token* estão entre as últimas.

Na abordagem estática uma única instância de um nó pode estar habilitada para disparar. Um operador só poderá disparar quando todas as suas entradas estiverem presentes e não houver *tokens* em nenhum de seus arcos de saída. Na abordagem dinâmica

Figura 9: Uma implementação de um loop usando tagged tokens. No início do loop um novo tag é alocado (definindo uma nova área de tokens). Tokens de iterações consecutivas recebem tags indicando pertencerem a esta área. O tag anterior ao loop é restaurado em tokens que saem do loop (VEEN, 1986).

é possível o disparo de várias instâncias de um nó ao mesmo tempo em tempo de execução. O(tag), é usado para diferenciar as instâncias de um nó, e identifica o contexto em que um determinado token foi criado. Neste caso, um nó está habilitado quando suas entradas contem um conjunto de tokens com tags idênticos.

As máquinas a fluxo de dados clássicas, que serviram de base para desenvolvimentos subsequentes foram as máquinas estática de Jack Dennis (DENNIS; MISUNAS, 1974) e as máquinas dinâmicas do MIT(ARVIND; NIKHIL, 1990) e da Universidade de Manchester(GURD; KIRKHAM; WATSON, 1985).

#### 2.2.1 Máquinas a fluxo de dados estáticas

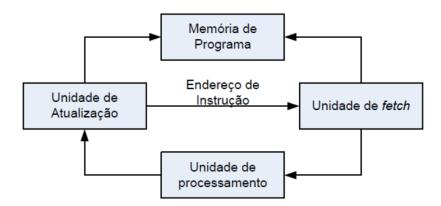

A Figura 10 mostra a organização geral de uma máquina fluxo de dados estática. A memória de programa contém padrões que representam os nós em um grafo a fluxo de dados (Figura 11). Cada padrão de estrutura possui um código de operação, espaços para os operandos e endereços de destino. Para determinar a disponibilidade dos operandos, os espaços contem bits de presença. A unidade de atualização é responsável por detectar as instruções prontas para serem executadas. Quando esta condição é verificada, a unidade de atualização envia as instruções prontas para a unidade de Fetch. A unidade de Fetch envia um pacote completo de operação contendo o opcode correpondente, os dados e a lista de destinos para a unidade de processamento e também limpa os bits de presença. A unidade de processamento realiza a operação, monta o pacote resultante e o envia para a unidade de atualização. A unidade de atualização armazena cada resultado no espaço dos operandos apropriados e checa os bits de presença para determinar se a atividade está habilitada.

Figura 10: Organização básica de uma máquina fluxo de dados estática((LEE; HURSON, 1993))

| PB | Operand 1     |

|----|---------------|

| PB | Operand 2     |

| 1  | Destination 1 |

| Ι  | Destination 2 |

Figura 11: Formato de instrução de uma máquina fluxo de dados estática

#### 2.2.2 Máquinas a fluxo de dados dinâmicas

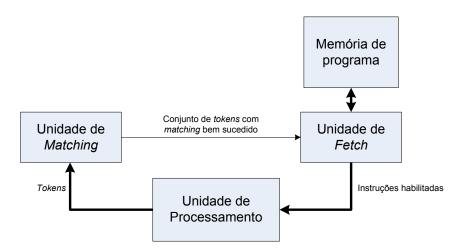

O modelo a fluxo de dados dinâmico foi proposto por Arvind no MIT (ARVIND; NIKHIL, 1990) e por Gurd e Watson na Universidade de Manchester (GURD; KIRKHAM; WATSON, 1985). A organização básica da arquitetura a fluxo de dados dinâmica é mostrada na Figura 12. Os tokens são recebidos pela unidade de Matching, que é uma memória contendo uma coleção de tokens em espera. A operação básica da Unidade de Matching é colocar juntos tokens com tags idênticos. Se um acerto existe (match), o token correspondente é extraído da Unidade de Matching e este conjunto de tokens é passado para a unidade de Fetch. Na unidade de Fetch os tags do par de tokens identificam univocamente uma instrução a ser carregada da memória de programa. Um formato típico de instrução para o modelo a fluxo de dados consiste de um código de operador, um campo literal ou constante e um campo de destino. A instrução, em conjunto com o par de tokens formam a instrução habilitada, a qual é enviada para a Unidade de Processamento. A unidade de processamento executa as instruções habilitadas e produz tokens de resultado a serem enviados à unidade de Matching.

Figura 12: Esquema geral de uma arquitetura a fluxo de dados dinâmica. (LEE; HURSON, 1993)

A maior vantagem do modelo dinâmico sobre o estático está no maior desempenho que pode ser obtido ao se permitir múltiplos tokens em um arco. Um laço, por exemplo, é desdobrado em tempo de execução, criando múltiplas instâncias do seu corpo e permitindo a execução de suas instâncias concorrentemente. O overhead, no entanto, envolvido na operação de matching sempre foi um grande problema. Para reduzir este custo em tempo de execução, as máquinas dinâmicas requerem a implementação de memórias associativas. Na prática, devido ao alto custo dessas memórias o que se usou foram mecanismos de matching pseudo-associativos, que requerem múltiplos acessos à memória. Estes acessos

tipicamente reduzem o desempenho e a eficiência das máquinas a fluxo de dados dinâmicas.

Outro problema típico dessas arquiteturas é a complexidade envolvida na alocação de recursos (regiões de memória). Cada operação de matching mal-sucedida provoca alocação de memória na unidade de matching. Em outras palavras, quando um bloco de código é mapeado para um processador, assume-se que a unidade de matching será capaz de suportar a alocação máxima de recursos do programa. Se este limite supera a capacidade da unidade, o programa pode entrar em deadlock. Por outro lado, esses recursos são muito caros para serem considerados infinitos.

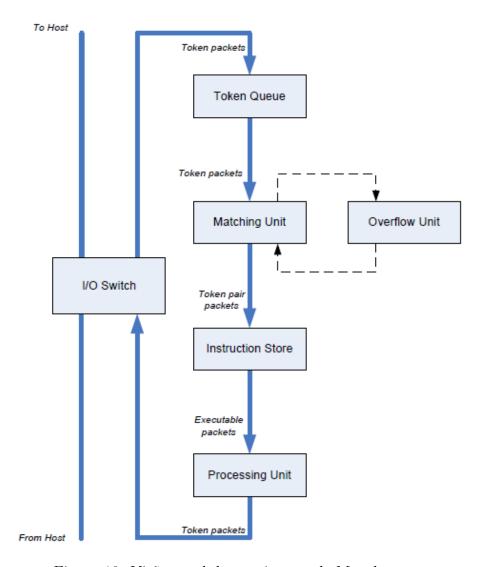

#### 2.2.2.1 A máquina de Manchester ((GURD; KIRKHAM; WATSON, 1985))

O grupo de Manchester desenvolveu o conceito de tagged-tokens para aumentar o paralelismo em grafos reentrantes independentemente do trabalho similar de Arvind e Gostelow(ARVIND; NIKHIL, 1990). A estrutura da arquitetura desenvolvida era similiar àquela mostrada na Figura 13. Tratava-se de um pipeline de quatro unidades: token queue, unidade de matching, unidade de fetching e unidade funcional (ou de processamento). Cada unidade trabalhava internamente de forma síncrona, mas se comunicava por meio de protocolos assíncronos.

Mais de 30 pacotes podiam ser processados simultaneamente nos vários estágios do pipeline. Para maximizar a velocidade de comunicação todos os dados eram transmitidos paralelamente, o que fazia com que cada pacote fosse transmitido totalmente de uma única vez. Consequentemente o tamanho dos pacotes, e portanto, dos tokens, era fixo. O token queue era simplesmente um buffer FIFO. Ele servia para regular as taxas irregulares de saída de dados de outras duas unidades no pipeline: a unidade de matching e a unidade funcional.

A unidade de matching aceitava tokens do token queue e enviava conjuntos completos de tokens de entrada para a unidade de fetching. Nessa máquina o número de arcos de entrada de um nó era limitado a dois, e um nó de destino poderia, portanto, ser apenas de uma entrada (monadic) ou de duas entradas (dyadic). Cada token levava a informação para distinguir os dois casos. No primeiro caso o token era simplesmente passado para a unidade de fetching. Para nós dyadic, uma operação de matching era realizada. Uma operação de matchingpoderia ou não resultar na produção de um pacote de saída. Isso explica a taxa variável desta unidade.

A unidade de fetching combinava o conjunto dos tokens de entrada com a descrição

Figura 13: Visão geral da arquitetura de Manchester

do nó de destino em um pacote executável. Cada nó poderia conter até duas descrições de destino, cada uma consistindo de um endereço e uma indicação se o nó de destino era monadic ou dyadic. Uma instrução dyadic poderia se tornar monadic trocando-se uma das descrições de destino por uma entrada constante (como um literal) para uma das duas portas de entrada.

A unidade funcional consistia de um preprocessador e um conjunto de elementos funcionais conectados via um distribuidor e um árbitro. O preprocessador executava instruções que requeriam acesso ao contador de memória. A maior parte dos contadores era usada para monitorar desempenho. Um dos contadores, chamado de contador de nome de ativação (activation name) era usado para a geração de áreas de tags únicas e podia ser manipulado apropriadamente pelo programa. Embora esta não fosse uma operação funcional, o conjunto de instruções era tal que ele próprio não poderia levar

a programas não funcionais. Os elementos funcionais eram processadores divididos em pequenas larguras de *bits* microprogramados. O tempo de processamento por instrução variava de 3 a 30 microssegundos, com uma média de 6 microssegundos. Essa variação, combinada ao fato de uma instrução poder produzir nenhum, um ou dois *tokens*, explica a taxa irregular da unidade funcional.

#### 2.2.2.2 A arquitetura Tagged-token do MIT (ARVIND; NIKHIL, 1990)

A máquina a fluxo de dados do MIT (MIT Tagged-Token Dataflow Architecture), assim como a máquina de Manchester foi implementada como um pipeline circular. Cada instrução pode ter até dois dados de entrada. Os tokens também possuíam tags que os associavam ao contexto de código a que pertenciam. Eram da forma  $\langle c.s_p, v \rangle$ . O campo  $c.s_p$  forma o tag. s identifica a instrução de destino, c indica a instância a que pertence o dado e p a porta de entrada do dado (esquerda ou direita).

Os tokens são agrupados na unidade de matching, cuja funcionalidade é a mesma da unidade de matching da máquina de Manchester. Os tokens com matching bem sucedido são então enviados à unidade de Fetch, onde o contexto é utilizado para endereçar um registrador de contexto. No registrador é obtido o endereço base do bloco de código (CBR), e pela soma do CBR com o  $offset\ s$  é obtido o endereço da memória de instrução onde estão armazenadas as seguintes informações: opcode, uma constante, um offset e no máximo dois destinos ( $s_1$  e  $s_2$ ). Há também associado com o registrador de contexto a memória de constantes (literais), os quais devem ser utilizados pelo bloco de código. Quando uma instrução especifica um offset, esse é utilizado para que seja buscado uma constante dentro da memória de constantes.

A ULA processa os valores de entrada da instrução e a constante, (se existir). Ao mesmo tempo são gerados os *tags* a serem utilizados pelos resultados da execução. Se forem produzidos mais *tokens* do que a Unidade de *Matching* pode processar, o excesso é armazenado na fila de *tokens* (*User Queue*).

# 2.3 Arquiteturas modernas inspiradas no modelo a fluxo de dados

Os conceitos da computação a fluxo de dados vêem sendo utilizados atualmente na concepção de algumas arquiteturas diferenciadas. Entre as mais eminentes estão Wavescalar e TRIPS.

#### 2.3.1 Wavescalar(SWANSON et al., 2007)

WaveScalar é uma ISA (*Instruction Set Architecture*) e um modelo de execução projetado para processadores escalonáveis de baixa complexidade e alto desempenho. Diferente de máquinas a fluxo de dados anteriores, a arquitetura WaveScalar pode prover de maneira eficiente a semântica sequencial que as linguagens imperativas tradicionais (como C/C++) requerem. Para permitir aos programadores expressarem de maneira fácil o paralelismo, WaveScalar suporta o estilo *pthread*, de granularidade alta e o estilo fluxo de dados, de granularidade fina. Além disso, ela permite mesclar as duas abordagens dentro de uma aplicação ou mesmo de uma única função(SWANSON et al., 2007).

Para executar os programas da arquiteura WaveScalar, foi desenvolvido um processador de arquitetura tile escalável chamado WaveCache. À medida que um programa executa, o WaveCache mapeia as instruções do programa em seu vetor de elementos de processamento. As instruções permanecem em seus elementos de processamento por várias invocações, e de acordo com a mudança do conjunto de trabalho de instruções, o WaveCache remove as instruções não utilizadas e mapeia novas em seus lugares. As instruções comunicam-se entre si diretamente através de uma interconexão escalável, hierárquica, dentro do próprio chip, removendo a necessidade de longos fios e comunicações broadcast.

WaveScalar procura resolver a maior dificuldade em relação às arquiteturas a fluxo de dados: a ausência de ordenação de memória, como requerida pelas linguagens populares, como C. Wavescalar impõe essa ordenação de memória introduzindo um novo conceito conhecido como wave-ordered memory. Na memória wave-ordered, instruções de memória são anotadas com informação extra que as ordena relativamente a outras instruções em porções do grafo de programa chamadas waves (ondas). Presentemente há duas formas de acessar memória: a interface wave-ordered e a interface não ordenada.

Waves. Na arquitetura WaveScalar os tags são chamados wave-numbers. Um token com um wave-number w e um valor v é designado como w.v. Ao invés de associar diferentes wave-number a diferentes instâncias de instruções específicas (como fazem a maioria das máquinas fluxo de dados), WaveScalar os associa a porções delineadas pelo compilador chamadas waves. As waves possuem mais de uma entrada e podem conter junções controladas (semelhante aos operadores deterministic merge). Elas não podem conter loops. A Figura 14 mostra um exemplo de loop dividido em waves, como mostrado pelas linhas tracejadas.

No topo de cada wave há um conjunto de instruções WAVE-ADVANCE (pequenos lo-

Figura 14: Um *loop* simples (a) e sua implementação em WaveScalar (b) (adaptado de (SWANSON et al., 2007))

sangos na figura). Cada qual incrementa o wave-number do token que passa por ele.

Chamadas de função. As chamadas de função em WaveScalar passam explicitamente os argumentos e um endereço de retorno para a função e disparam sua execução. Ao passar argumentos, cria-se uma dependência de dados entre a função chamadora (caller) e a função chamada (callee). Para funções indiretas, essas dependências não são estaticamente conhecidas e portanto o grafo fluxo de dados estático da aplicação não as contem. Ao contrário, WaveScalar provê um mecanismo para envio de valores de dados para uma instrução num endereço computado. A instrução que permite isso é chamada INDIRECT-SEND.

A instrução INDIRECT-SEND toma como entrada o dado a ser enviado, um endereço base para a instrução de destino (normalmente um *label*), e o *offset* a partir da base (como um dado imediato).

A Figura 15 contem o grafo para um pequena função e um local de chamada. As linhas tracejadas nos grafos representam as dependências que existem apenas em tempo de execução. A instrução LANDING\_PAD provê um destino alvo para um dado enviado via INDIRECT-SEND. Para chamar a função, é necessário usar três instruções INDIRECT-SEND,

Figura 15: Chamada de função em WaveScalar

duas para A e B e uma para o endereço de retorno, que é o endereço do LANDING\_PAD (label ret na Figura).

Quando os valores chegam em foo, as instruções LANDING\_PAD as passam para as instruções WAVE-ADVANCE, que os repassam para o corpo da função (o calee inicia uma nova wave). Uma vez que a função foi terminada, eventualmente executando muitas waves, foo usa uma única instrução INDIRECT-SEND para retornar o resultado à instrução LANDING\_PAD do chamador. Após uma chamada de função, o chamador inicia uma nova onda usando uma instrução WAVE-ADVANCE.

Memory Ordering. Uma ISA a fluxo de dados mantém a dependência de dados apenas no grafo, e não possui um mecanismo garantindo que as operações de memória ocorram na ordem do programa. A Figura 16 mostra um grafo que demonstra o problema de ordenação de memória. No grafo, o load precisa ser executado após o store. No entanto, o grafo não expressa essa dependência implícita entre as duas instruções (linhas pontilhadas).

A memória wave-ordered soluciona o problema de ordenação de memória usando waves. Dentro de cada wave, o compilador anota as instruções de acesso à memória para codificar as restrições de ordenação entre elas. Como os wave-numbers aumentam durante a execução do programa, eles provêem uma ordenação para as ondas em execução. Tomadas juntas, a ordenação de granularidade alta entre as waves (através de seus wave-numbers),

Figura 16: A linha tracejada representa uma potencial dependência de dados implícita entre as instruções LOAD e STORE(SWANSON et al., 2007).

combinadas com a ordenação de granularidade fina dentro de cada *wave*, provêem uma ordem total em todas as operações de memória do programa.

## 2.3.2 TRIPS (BURGER et al., 2004)

A arquitetura TRIPS (The Tera-op, Reliable, Intelligently adaptive Processing System<sup>1</sup>) está sendo desenvolvida com o intuito de se adequar à evolução dos semicondutores na próxima década, avançando para novos níveis de eficiência e desempenho(BURGER et al., 2004). Ela é a primeira instância do conjunto de instruções EDGE (Explicit Data Graph Execution<sup>2</sup>) uma nova classe de ISA.

O conjunto de instruções EDGE é definido por seu modo de execução em blocos atômicos assim como por sua característica de comunicação direta para as instruções dentro de um bloco. Isso sgnifica que um bloco de instruções pode ser carregado e executado como uma unidade. Com a comunicação direta, as instruções dentro de um bloco podem ser enviadas diretamente para instruções dependentes dentro de um mesmo bloco. Esse modo de execução é muito similar ao conceito de fluxo de dados: instruções dependentes esperam operandos de outras instruções antes de iniciar sua execução.

Os quatro objetivos com a implementação TRIPS são os seguintes:

- Aumentar a concorrência;

- Minimizar o consumo de energia tanto quanto possível;

- ullet Minimizar os tempos de comunicação e

<sup>&</sup>lt;sup>1</sup>Sistema de processamento de TERA operações, inteligentemente adaptativo, confiável.

<sup>&</sup>lt;sup>2</sup>Execução explícita a grafo de dados

#### • Oferecer uma maior flexibilidade

A arquitetura TRIPS busca estes quatro objetivos combinando os elementos do modelo a fluxo de controle com os benefícios do modelo de execução a fluxo de dados.

Muitas das atuais arquiteturas caem em uma de duas categorias: sistemas de granularidade fina, de aplicação específica ou sistemas de granularidade grossa, para propósitos gerais. Ambas possuem desvantagens: sistemas de granularidade fina possuem um desempenho fraco em aplicações seriais ou fora do padrão, enquanto arquiteturas de granularidade grossa são incapazes de apresentar o mesmo desempenho nas aplicações paralelas. A arquitetura TRIPS busca unir os benefícios de ambas através de uma arquitetura polimórfica, ou seja, a arquitetura TRIPS pode trabalhar tanto em uma forma com granularidade fina, quanto em uma forma com granularidade grossa.

Figura 17: Visão geral da arquitetura TRIPS. Retirado de (SANKARALIN-GAM et al., 2003)

Essa flexibilidade é conseguida através do uso de núcleos grandes, de granularidade alta que podem ser divididos em núcleos menores para aplicações altamente paralelas. Com essa abordagem, a arquitetura pretende alcançar alto desempenho tanto com aplicações altamente paralelas quanto com aplicações sequenciais, sendo uma máquina de propósito geral.

Os hiperblocos são grupos de até 128 instruções, organizadas pelo compilador, que são mapeadas em um vetor de unidades de execução. Esses hiperblocos são criados de maneira que possam ser executados atomicamente, como definido pela arquiteura EDGE. Cabe ao compilador agrupar estes conjuntos de instruções para que os hiperblocos possam ser executados sem nenhuma potencial ramificação (branch). Uma vez iniciada a execução de um hiperbloco, as dependências entre as instruções são resolvidas pela comunicação direta dentro do bloco, representando um modelo de execução semelhante ao modelo a fluxo de dados.

Figura 18: Geração de código para o TRIPS(SANKARALINGAM et al., 2003)

A Figura 18 é um exemplo de código no TRIPS. Neste pequeno trecho de código (a) em C, o compilador aloca a entrada y em um registrador (b). No código assembly semelhante ao MIPS, a variável x é salva no registro 5(c). O compilador converte o branch original para uma instrução de teste e usa o resultado para predicar as instruções dependentes de controle, que aparecem como linhas tracejadas no grafo (d). Cada nó 2x2 na matriz de nós guarda até duas instruções (e). O compilador gera no formato do processador alvo, correspondendo ao mapa de localizações de instruções na parte de baixo de (d).

Predicação de ramificação. Branch predication é o método de adiconar um outro operando, chamado de predicado, para toda instrução condicional - uma instrução que pode ou não executar, dependendo do resultado do branch. Instruções que produzem valores podem também produzir predicados, que podem então ser transmitidos para essas instruções condicionais. A instrução condicional não pode executar até receber o predicado, uma vez que ele é um operando para a instrução. Baseado no valor do predi-

cado, a instrução pode teminar ou ser executada. O que ocorre efetivamente, é que este mecanismo converte a dependência de controle resultante da instrução de ramificação condicional em dependências de dados para as instruções em seguida à ramificação.

Assim sendo, embora as dependências ainda existam, mais instruções podem ser carregadas sem a preocupação com as predições de ramificação (branch prediction). Uma vez que o compilador precisa encontrar instruções sem dependências de controle para agrupar em hiperblocos, este mecanismo de predicação de ramificação se integra à arquitetura TRIPS, aumentando bastante o número de instruções que podem ser agrupadas em um hiperbloco.

Dentro do hiperbloco, as ramificações são tratadas como dependências de dados num método semelhante ao modelo a fluxo de dados e com comunicação direta.

Memória. Uma vez que a implementação TRIPS opera em múltiplos hiperblocos de 128 instruções cada, um poderoso sistema de memória é necessário para prevenir a degradação do desempenho geral do sistema. O sistema de memória usa múltiplos bancos, buffers e tabelas para alcançar a alta velocidade necessária pelo sistema. Em particular, cada processador TRIPS possui quatro bancos de memória, que podem suportar até 256 operações de memória.

# 3 Computação Reconfigurável

A variedade de objetivos das tarefas computacionais levou ao desenvolvimento de três classes de arquiteturas de computadores (BOBDA, 2007):

- As arquiteturas de propósito geral, largamente usadas e fundamentalmente baseadas no modelo de Von Neumann;

- As arquiteturas para domínios específicos, em que características típicas de um campo de aplicação determinam o projeto de arquiteturas voltadas para o alto desempenho nesse tipo de aplicação. Entre os exemplos mais eminentes estão os DSPs (Digital Signal Processors) ou processadores digitais de sinais;

- As arquiteturas específicas para aplicação, compreendida pelos ASIP Application-Specific Instruction-Set Processors, desenvolvidas especialmente para uma única aplicação. Em processamento de mídia por exemplo, processadores são desenvolvidos especialmente para algoritmos de um determinado padrão de compressão de vídeo. Estes processadores são incapazes de realizar quaisquer outras tarefas.

O gráfico da Figura 19, retirado de (BOBDA, 2007) mostra que em geral há um compromisso entre flexibilidade e desempenho entre essas classes. Os computadores de propósito geral, por exemplo possuem grande flexibilidade, o que na prática quer dizer que podem ser aproveitados para resolver virtualmente qualquer tarefa de computação, no entanto, com um desempenho relativamente baixo, quando comparados às outras classes, quando usadas para suas aplicações alvo. À medida que o campo de aplicação de um processador se restringe, diminui-se também sua flexibilidade, ou seja, mais difícies se tornam de ser aproveitados para outras tarefas, o que ocorre às custas de um maior desempenho nas tarefas visadas.

A computação reconfigurável se insere neste contexto como o estudo da computação realizada em dispositivos capazes de serem *configurados* e *reconfigurados* para executarem determinada tarefa. Por configuração entende-se o processo de se alterar a estrutura

Figura 19: Gráfico mostrando a relação desempenhoxflexibilidade para as classes de máquinas computacionais.

interna do dispositivo, em geral ligando-se ou desligando-se determinados pontos de interconexão(COMPTON; HAUCK, 2002) de forma a atender da melhor forma possível uma determinada tarefa de computação, no momento de sua ligação. Respectivamente, por reconfiguração entende-se essa mesma alteração realizada em tempo de execução.

## 3.1 Arquiteturas de computação reconfigurável

Em (RADUNOVIC; MILUTINOVIC, 1998), um artigo relativamente antigo em relação aos últimos avanços da computação reconfigurável, é apresentada uma classificação das arquiteturas reconfiguráveis. A computação reconfigurável já existia mesmo antes do advento (e do grande avanço) dos FPGAs. Mas como já foi dito, apenas com estes últimos é que ganhou mais força. Para os autores, de uma forma geral, a arquitetura de um sistema reconfigurável pode ser descrita como uma rede reconfigurável de células lógicas básicas.

A taxonomia proposta por (RADUNOVIC; MILUTINOVIC, 1998) usa nomes da mitologia grega e faz a classificação dos sistemas usando os seguintes critérios:

• Objetivo do sistema reconfigurável. Duas ramificações foram identificadas aqui pelos autores: sistemas visando tolerância a falhas e sistemas visando maior desempenho;

- Granularidade do bloco de lógica reconfigurável. Os autores classificam os sistemas como de granularidade grossa, média e fina;

- Acoplamento com o sistema host. Aqui os sistemas podem ser dinâmicos, estáticos fortemente acoplados ou estáticos fracamente acoplados.

(MESQUITA, 2002) usou uma árvore para apresentar de maneira mais didática essa classificação, como se vê na Figura 20.

Figura 20: Classificação de (RADUNOVIC; MILUTINOVIC, 1998) em forma de árvore (retirado de (MESQUITA, 2002))

A próxima seção trata das arquiteturas classificadas por estes autores até a data de seu artigo, os quais trataremos por *primeiros sistemas reconfiguráveis*

## 3.1.1 Primeiros sistemas de computação reconfigurável

Os sistemas aqui apresentados excluem qualquer abordagem do ramo de tolerância a falhas. Todas as arquiteturas visam aumento de desempenho.

#### 3.1.1.1 MATRIX (MIRSKY; DEHON, 1996)

O sistema MATRIX pode ser compreendido como sendo de granularidade média, com rede de interconexão externa, estático e fracamente acoplado (RADUNOVIC; MILUTINOVIC, 1998). MATRIX é a sigla para Multiple ALU architecture with reconfigurable interconnect experiment, ou arquitetura experimental de múltiplas ULAs com interconexão reconfigurável. Trata-se de um esforço acadêmico para uma unidade que compreende uma matriz de unidades funcionais básicas (BFUs), onde cada uma contém uma ULA de 8 bits, uma memória de 256 palavras e lógica de controle. A ULA contém as operações aritméticas e lógicas padrão, além de um multiplicador. Uma cadeia de carry configurável entre ULAs adjacentes pode ser configurada para operações de palavras maiores. Há ainda estruturas lógicas especiais para reconfiguração da conexão da ALU com a rede de comunicação. Com essas características, uma unidade funcional básica pode funcionar como uma memória de instruções, memória de dados, uma ULA combinada com banco de registros ou ainda como uma ULA independente. As instruções podem ser roteadas para várias ULAs. A infraestrutura de roteamento provê três níveis de barramento de 8-bits. Oito ligações aos vizinhos mais próximos, quatro aos segundos vizinhos mais próximos e linhas globais ao longo de uma coluna ou linha inteira. Uma desvantagem dessa arquitetura é seu baixo desempenho para operações em nível de bit e byte.

#### 3.1.1.2 RAW (WAINGOLD et al., 1997)

De acordo com a classificação apresentada, este é um projeto voltado para mmaior desempenho, de granularidade grossa (os blocos configuráveis são processadores), com rede de interconexão externa. O projeto é baseado em uma unidade de processamento constituída de blocos<sup>1</sup> mais simples, altamente conectados e replicados. Cada um desses elementos possui também associado um *switch* com sua própria memória, controlando a reconfiguração da rede de interconexão (Figura 21).

O sistema RAW ocupa maior parte dos espaços com unidades de execução, procurando atingir maior grau de paralelismo e *clocks* mais altos. Isso também simplifica o processo de verificação. A presença de lógica de reconfiguração de granularidade fina (blocos CL da Figura 21) permite avaliação de operações em nível de *bit* e *byte* no próprio *tile*. Este sistema sofre de ineficiência no caso de computações altamente dinâmicas, ou seja, nos

<sup>&</sup>lt;sup>1</sup>Chamados em inglês de *tiles*, literalmente: ladrilhos (ou azulejos). Dá a idéia de vários pedaços idênticos que juntos compõem a unidade. O termo em geral é usado quando se refere a uma unidade equivalente a um processador simples

Figura 21: Um processador RAW é construído de múltiplos blocos idênticos. Cada bloco contém memória de instrução (IMEM), memória de dados (DMEM), unidade aritmética e lógica (ALU), registradores, lógica configurável(CL) e um *switch* programável associado com sua memória de instrução (SMEM).

casos em que as dependências de dados e de roteamento não podem ser resolvidas em tempo de compilação.

#### 3.1.1.3 RaPiD(EBELING; CRONQUIST; FRANKLIN, 1996)

RaPiD (reconfigurable pipelined datapath) é um representante das arquiteturas fortemente acopladas de granularidade média. Ele consiste de um vetor de células localizadas no caminho de dados (datapath). Todos os elementos estão conectados ao barramento de dados. Cada célula possui ULA, registradores, multiplicadores e memória. Assim como as outras arquiteturas apresentadas até aqui, possuem um maior desempenho para operações aritméticas complexas, devido à sua granularidade maior do que a dos FP-GAs(RADUNOVIC; MILUTINOVIC, 1998).

#### 3.1.1.4 Firefly(GOEKE et al., 1997)

O sistema Firefly é um sistema evolutivo baseado no modelo de autômatos celulares, que tende a produzir oscilações uniformes. Os princípios de computação evolutiva já foram usados em *software*. Este é um dos primeiros trabalhos a implementar estes princípios em *hardware*. Esta arquitetura pode ser classificada como de granularidade fina, com conexão externa e dinâmica.

#### 3.1.1.5 SPLASH-II(GOKHALE et al., 1990)

O sistema SPLASH-II é um sistema feito de vários FPGAs soldados em placas separadas e conectados para constituir um computador massivamente paralelo. Nessas placas, chamadas de array boards, os FPGAs podem ser reconfigurados para cumprir uma tarefa específica. Devido a esse tipo de ligação, trata-se de um sistema fracamente acoplado, porém de granularidade fina, com rede de interconexão externa e estático. Seu antecessor, SPLAH-I, foi um dos primeiros sistemas de computação reconfiguráveis. As array boards são conectadas a um host por uma placa de interface e um barramento de sistema. Cada placa possui 17 FPGAs, sendo 16 para processamento e 1 para implementação da interconexão.

Figura 22: Arquitetura SPLASH-II.(retirado de (BOBDA, 2007))

#### 3.1.1.6 DECPeRLe-1(VUILLEMIN et al., 2002)

DECPeRLe é também um projeto pioneiro da computação reconfigurável, que cai na mesma categoria do sistema SPLASH. É constituído por um *host*, conectado a uma placa com 16 FPGAs através de um barramento de entrada e saída. O acesso do *host* é similar a um acesso de memória, com escritas e leituras dos dados para processamento pelos FPGAs. A dificuldade de configuração e a falta de ferramentas de compilação são grandes desvantagens desse sistema(RADUNOVIC; MILUTINOVIC, 1998).

#### 3.1.1.7 PRISM(ATHANAS; SILVERMAN, 1993)

O PRISM-I foi desenvolvido para provar a viabilidade de se usar instruções configuráveis com um processador de propósito de geral. Para tanto foi construída uma placa com FPGAs, ligada através de um barramento ao processador principal. Apesar de o desempenho não ser satisfatório, devido à baixa velocidade de comunicação, a viabilidade de se ter instruções configuráveis foi demonstrada. A versão PRISM-II atacou os problemas de velocidade de comunicação, conseguindo resultados melhores. Este sistema pode pode ser considerado na mesma categoria de SPLASH e DECPeRLe. Foi também um pioneiro que abriu grande campo para o estudo das instruções configuráveis.

O projeto RENCO, que aqui será apenas citado, seguiu uma abordagem semelhante à dos projetos SPLASH, DECPeRLe e PRISM, sendo constituído por uma placa externa com quatro FPGAs, ligado a um *host*.