Projeto de um controlador PID para controle de ganho de uma câmera com sensor CMOS utilizando computação reconfigurável

Drausio Linardi Rossi

SERVIÇO DE PÓS-GRADUAÇÃO DO ICMC-USP

Data de Depósito: 10/01/2012

Assinatura:\_

# Projeto de um controlador PID para controle de ganho de uma câmera com sensor CMOS utilizando computaçãoo reconfigurável

#### Dráusio Linardi Rossi

Orientador: Prof. Dr. Eduardo Marques

Dissertação apresentada ao Instituto de Ciências Matemáticas e de Computação - ICMC-USP, como parte dos requisitos para obtenção do título de Mestre em Ciências de Computação e Matemática Computacional. VERSÃO REVISADA

USP – São Carlos Janeiro de 2012

# Ficha catalográfica elaborada pela Biblioteca Prof. Achille Bassi e Seção Técnica de Informática, ICMC/USP, com os dados fornecidos pelo(a) autor(a)

Rossi, Drausio Linardi

R831p

Projeto de um controlador PID para controle de ganho de uma câmera com sensor CMOS utilizando computação reconfigurável / Drausio Linardi Rossi; orientador Eduardo Marques -- São Carlos, 2011. 71 p.

Dissertação (Mestrado - Programa de Pós-Graduação em Ciências de Computação e Matemática Computacional) -- Instituto de Ciências Matemáticas e de Computação, Universidade de São Paulo, 2011.

1. CIÊNCIA DA COMPUTAÇÃO. 2. COMPUTAÇÃO RECONFIGURÁVEL. 3. CIRCUITOS FPGA. I. Marques, Eduardo, orient. II. Título.

Dedico este trabalho

## À Deus

Ao meu querido filho Hiago, e a minha esposa Márcia, pelo incentivo e compreenção.

À minha família

#### A sabedoria

Primeiro ela o conduzirá por caminhos tortuosos, causando-lhe medo e tremor, e o atormentará com sua disciplina, até que o homem confie nela e até que ela o tenha provado com suas exigências. Depois ela o reconduzirá pelo caminho reto, o alegrará e lhe manifestrá os seus segredos.

Eclesiástico 17-18

# Agradecimentos

Aos colegas do LCR, em especial ao Leandro Martinez, que se fez presente em horas difíceis.

À Whirlpool do Brasil, pelas horas cedidas, para que este trabalho fosse viabilizado.

Aos amigos Miguel Martins, Mario Luis Botêga Jr, Bruno Franciscon Mazzotti e Luiz Henrique Kiehn.

Ao orientador e amigo Professor Doutor Eduardo Marques, pela orientação, amizade e sobretudo pela confiança.

Ao Professor Doutor João Miguel Gago Pontes de Brito Lima da Universidade do Algarve, Portugal, pelo apoio na área de controladores PID, essencial na conclusão deste trabalho.

# Sumário

| 1        | Intr | oduçã  | 0                                                          | 1  |

|----------|------|--------|------------------------------------------------------------|----|

|          | 1.1  | Descri | ição do Sistema Proposto                                   | 1  |

|          | 1.2  | Objeti | ivos                                                       | 3  |

|          | 1.3  | Organ  | iização do Trabalho                                        | 4  |

| <b>2</b> | Fun  | damer  | ntação Teórica                                             | 5  |

|          | 2.1  | Sistem | nas de Controle                                            | 5  |

|          |      | 2.1.1  | Controladores Analógicos                                   | 6  |

|          |      | 2.1.2  | Controladores Digitais                                     | 6  |

|          | 2.2  | Contro | olador PID                                                 | 7  |

|          |      | 2.2.1  | Histórico                                                  | 7  |

|          |      | 2.2.2  | Conceito                                                   | 8  |

|          |      | 2.2.3  | Termo Proporcional                                         | 9  |

|          |      | 2.2.4  | Termo Integral                                             | 9  |

|          |      | 2.2.5  | Termo Derivativo                                           | 11 |

|          |      | 2.2.6  | Controlador PID Digital                                    | 12 |

|          |      | 2.2.7  | Ajuste do controlador PID                                  | 14 |

|          | 2.3  | Histog | grama                                                      | 14 |

|          |      | 2.3.1  | Conceito                                                   | 14 |

|          |      | 2.3.2  | Especificação direta de histograma                         | 20 |

|          | 2.4  | Tecno  | logia de Sensores de Imagem Digital                        | 22 |

|          |      | 2.4.1  | Introdução                                                 | 22 |

|          |      | 2.4.2  | Sensor de Imagem CCD                                       | 26 |

|          |      | 2.4.3  | Convertendo Fótons em carga elétrica - Efeito Fotoelétrico | 29 |

|          |      | 2.4.4  | Processo de Leitura de Carga                               | 30 |

|          |      | 2.4.5  | Arquitetura da Matriz de <i>Pixels</i> CCD                 | 31 |

|          |      | 2.4.6  | Sensor de Imagem CMOS                                      | 33 |

|          |      | 2.4.7  | Processo de Leitura de Carga                               | 36 |

|          |      | 2.4.8  | Fatores que Comprometem a Qualidade da Imagem              | 36 |

| 2.5       Computação Reconfigurável       4         2.5.1       FPGAs       4         2.5.2       Estruturas das FPGAs       4         3       Plataforma de Desenvolvimento       4         3.1       Kit de Desenvolvimento DE2 70       4         3.1.1       Placa de Desenvolvimento DE2 70       5         3.1.2       Ferramentas de Desenvolvimento de Software Embarcado       5         3.1.3       Processador RISC Customizável       5         3.1.4       Ferramentas GNUpro para Software Embarcado       5         3.2       Módulo da Câmera CMOS       5         3.3       Conexão da Câmera com a Placa de Desenvolvimento D2 - 70       5         3.4       Monitoramento da Imagem no Sistema       5         4       Implementação do Sistema Proposto       5         4       Cálculo do histograma e cálculo do erro       6         6       Conclusão       6          | SU | JMÁI | RIO    |                                                                         | viii |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------|--------|-------------------------------------------------------------------------|------|

| 2.5.1       FPGAs       4         2.5.2       Estruturas das FPGAs       4         3       Plataforma de Desenvolvimento       49         3.1       Kit de Desenvolvimento DE2 70       4         3.1.1       Placa de Desenvolvimento DE2 70       50         3.1.2       Ferramentas de Desenvolvimento de Software Embarcado       5         3.1.3       Processador RISC Customizável       5         3.1.4       Ferramentas GNUpro para Software Embarcado       5         3.2       Módulo da Câmera CMOS       5         3.3       Conexão da Câmera com a Placa de Desenvolvimento D2 - 70       5         3.4       Monitoramento da Imagem no Sistema       5         4       Implementação do Sistema Proposto       5         4.0.1       Cálculo do histograma e cálculo do erro       6         5       Resultados do Sistema Proposto       6         6       Conclusão       6 |    |      | 2.4.9  | Comparativo entre CCD e CMOS                                            | 37   |

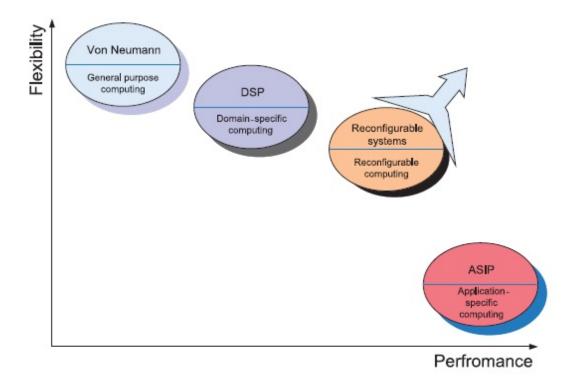

| 2.5.2       Estruturas das FPGAs       4         3       Plataforma de Desenvolvimento       49         3.1       Kit de Desenvolvimento DE2 70       4         3.1.1       Placa de Desenvolvimento DE2 70       50         3.1.2       Ferramentas de Desenvolvimento de Software Embarcado       5         3.1.3       Processador RISC Customizável       5         3.1.4       Ferramentas GNUpro para Software Embarcado       5         3.2       Módulo da Câmera CMOS       5         3.3       Conexão da Câmera com a Placa de Desenvolvimento D2 - 70       5         3.4       Monitoramento da Imagem no Sistema       5         4       Implementação do Sistema Proposto       5         4.0.1       Cálculo do histograma e cálculo do erro       6         5       Resultados do Sistema Proposto       6         6       Conclusão       6                                   |    | 2.5  | Comp   | utação Reconfigurável                                                   | 41   |

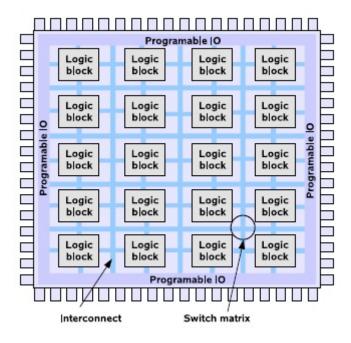

| 3 Plataforma de Desenvolvimento       49         3.1 Kit de Desenvolvimento DE2 70       40         3.1.1 Placa de Desenvolvimento DE2 70       50         3.1.2 Ferramentas de Desenvolvimento de Software Embarcado       50         3.1.3 Processador RISC Customizável       50         3.1.4 Ferramentas GNUpro para Software Embarcado       50         3.2 Módulo da Câmera CMOS       50         3.3 Conexão da Câmera com a Placa de Desenvolvimento D2 - 70       50         3.4 Monitoramento da Imagem no Sistema       50         4 Implementação do Sistema Proposto       50         4.0.1 Cálculo do histograma e cálculo do erro       60         5 Resultados do Sistema Proposto       60         6 Conclusão       60                                                                                                                                                       |    |      | 2.5.1  | FPGAs                                                                   | 44   |

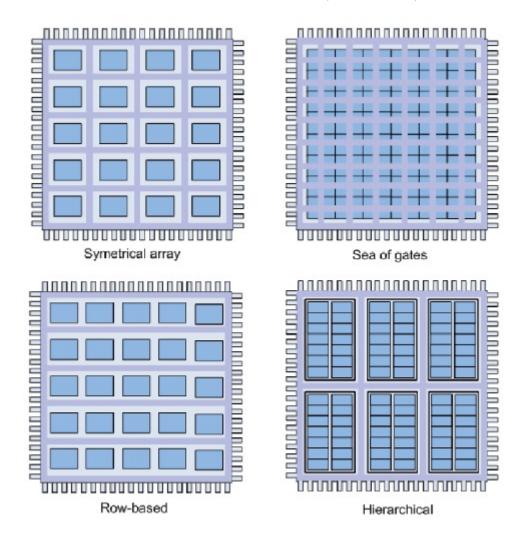

| 3.1 Kit de Desenvolvimento DE2 70       4         3.1.1 Placa de Desenvolvimento DE2 70       5         3.1.2 Ferramentas de Desenvolvimento de Software Embarcado       5         3.1.3 Processador RISC Customizável       5         3.1.4 Ferramentas GNUpro para Software Embarcado       5         3.2 Módulo da Câmera CMOS       5         3.3 Conexão da Câmera com a Placa de Desenvolvimento D2 - 70       5         3.4 Monitoramento da Imagem no Sistema       5         4 Implementação do Sistema Proposto       5         4.0.1 Cálculo do histograma e cálculo do erro       6         5 Resultados do Sistema Proposto       6         6 Conclusão       6                                                                                                                                                                                                                    |    |      | 2.5.2  | Estruturas das FPGAs                                                    | 46   |

| 3.1.1 Placa de Desenvolvimento DE2 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3  | Plat | taform | a de Desenvolvimento                                                    | 49   |

| 3.1.2 Ferramentas de Desenvolvimento de Software Embarcado 5 3.1.3 Processador RISC Customizável 5 3.1.4 Ferramentas GNUpro para Software Embarcado 5 3.2 Módulo da Câmera CMOS 5 3.3 Conexão da Câmera com a Placa de Desenvolvimento D2 - 70 5 3.4 Monitoramento da Imagem no Sistema 5 4 Implementação do Sistema Proposto 4.0.1 Cálculo do histograma e cálculo do erro 6 5 Resultados do Sistema Proposto 6 6 Conclusão 6 6 Conclusão 6                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    | 3.1  | Kit de | Desenvolvimento DE2 70                                                  | 49   |

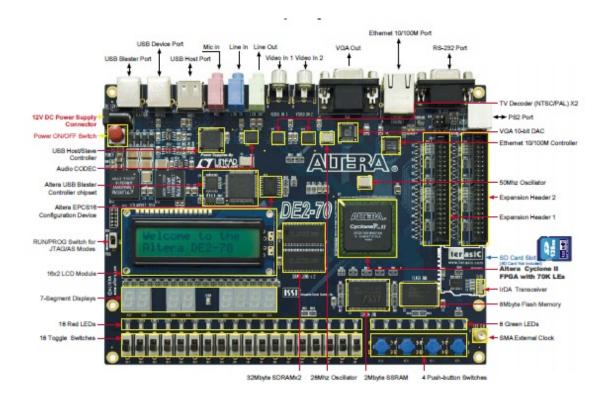

| 3.1.3 Processador RISC Customizável       5         3.1.4 Ferramentas GNUpro para Software Embarcado       5         3.2 Módulo da Câmera CMOS       5         3.3 Conexão da Câmera com a Placa de Desenvolvimento D2 - 70       5         3.4 Monitoramento da Imagem no Sistema       5         4 Implementação do Sistema Proposto       5         4.0.1 Cálculo do histograma e cálculo do erro       6         5 Resultados do Sistema Proposto       6         6 Conclusão       6                                                                                                                                                                                                                                                                                                                                                                                                       |    |      | 3.1.1  | Placa de Desenvolvimento DE2 70                                         | 50   |

| 3.1.4 Ferramentas GNUpro para Software Embarcado                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |      | 3.1.2  | Ferramentas de Desenvolvimento de Software Embarcado                    | 51   |

| 3.2 Módulo da Câmera CMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |      | 3.1.3  | Processador RISC Customizável                                           | 52   |

| 3.3 Conexão da Câmera com a Placa de Desenvolvimento D2 - 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |      | 3.1.4  | Ferramentas GNUpro para Software Embarcado                              | 55   |

| 3.4 Monitoramento da Imagem no Sistema                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    | 3.2  | Módul  | o da Câmera CMOS                                                        | 55   |

| 4 Implementação do Sistema Proposto 4.0.1 Cálculo do histograma e cálculo do erro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    | 3.3  | Conex  | ão da Câmera com a Placa de Desenvolvimento D2 - 70 $\ \ldots \ \ldots$ | 58   |

| 4.0.1 Cálculo do histograma e cálculo do erro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    | 3.4  | Monito | oramento da Imagem no Sistema                                           | 58   |

| 5 Resultados do Sistema Proposto 6 Conclusão 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4  | Imp  | lemen  | tação do Sistema Proposto                                               | 59   |

| 6 Conclusão 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |      | 4.0.1  | Cálculo do histograma e cálculo do erro                                 | 60   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5  | Res  | ultado | s do Sistema Proposto                                                   | 64   |

| 7 Trabalhos Futuros 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6  | Con  | clusão |                                                                         | 68   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7  | Tra  | balhos | Futuros                                                                 | 70   |

**72**

Referências Bibliográficas

# Lista de Figuras

| 1.1  | Fluxo de Dados na Detecção de Pedestres (de Holanda, 2010)                              | 2  |

|------|-----------------------------------------------------------------------------------------|----|

| 1.2  | Caminho do sinal analógico-digital e realimentação do ganho analógico,                  |    |

|      | adaptada de (www.terasic.com, 2008)                                                     | 3  |

| 2.1  | Sistema de Controle Digital, adaptada de (Ahmed, 1997)                                  | 7  |

| 2.2  | Controlador PID contínuo, paralelo de malha fechada (Åström e Hägglund,                 |    |

|      | 2006)                                                                                   | 8  |

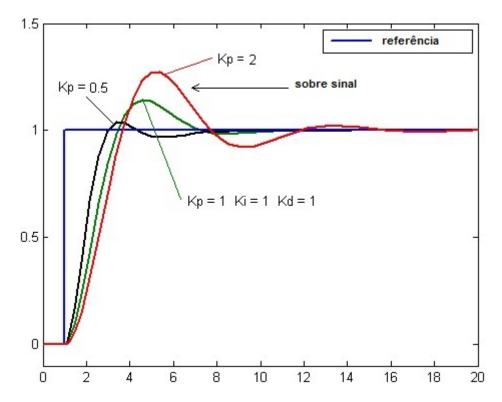

| 2.3  | Resposta de um controlador PID para variações de ganho proporcional Kp                  | 10 |

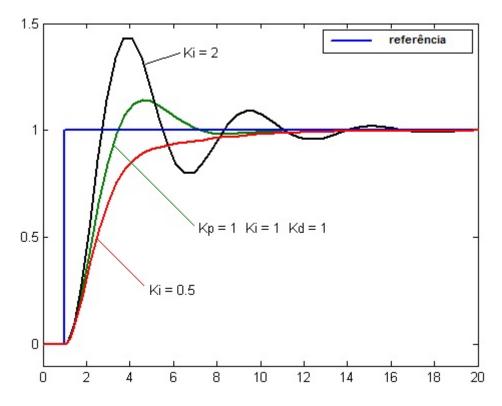

| 2.4  | Resposta de um controlador PID para variações de ganho Integral Ki $\ .\ .\ .$          | 11 |

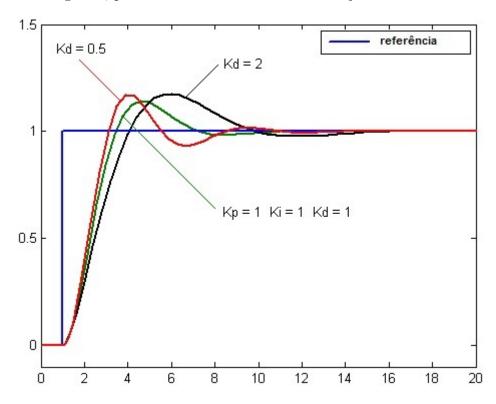

| 2.5  | Resposta de um controlador PID para variações de ganho Derivativo Kd $$ .               | 12 |

| 2.6  | Exemplo de valores de conversão $\mathrm{A}/\mathrm{D}$ de 8 bits para imagem com cinco |    |

|      | níveis de cinza                                                                         | 15 |

| 2.7  | Exemplo de histograma para imagem com oito níveis de cinza (Filho e                     |    |

|      | Neto, 1999)                                                                             | 17 |

| 2.8  | Exemplo de histogramas (Filho e Neto, 1999)                                             | 18 |

| 2.9  | Imagens correspondentes aos histogramas da figura 2.8 (Filho e Neto, 1999)              | 19 |

| 2.10 | Gráfico: Diâmetro da Pupila em Função da Luminância (Moon e Spencer,                    |    |

|      | 1944)                                                                                   | 22 |

| 2.11 | Sistema digital de imagem (A. El Gamal, 2005)                                           | 25 |

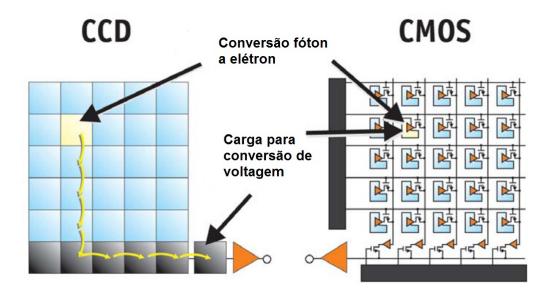

| 2.12 | Sensores CCD movem a carga gerada pelos fótons de pixel a pixel até                     |    |

|      | convertê-la em voltagem em uma saída. Sensores CMOS convertem a carga                   |    |

|      | em voltagem dentro de cada pixel (Litwiller, 2005)                                      | 25 |

| 2.13 | Anatomia de um Sensor CCD (www.circuitstoday.com, 2010)                                 | 28 |

| 2.14 | Conjunto Sensor CCD mais circuito de câmera (http://sensorcleaning.com,                 |    |

|      | 2010)                                                                                   | 28 |

| 2.15 | Interação Fótons, Comprimento de Onda e Silício (Company, 2008b) $$                     | 30 |

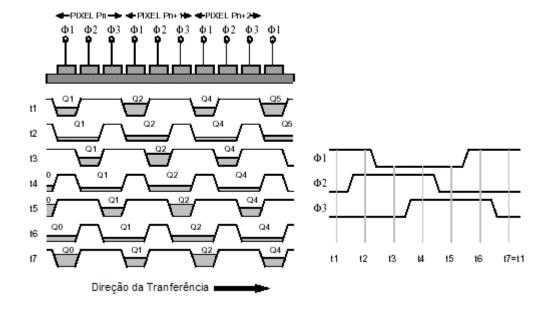

| 2.16 | Técnica three-phases de transferência de carga (Company, 2008b) $\ \ldots \ \ldots$     | 31 |

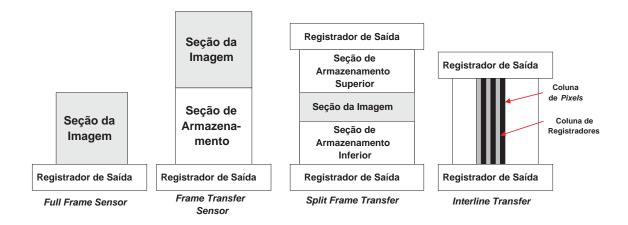

| 2.17 | Arquitetura de dispositivos CCD (Taylor, 1998)                                          | 32 |

LISTA DE FIGURAS x

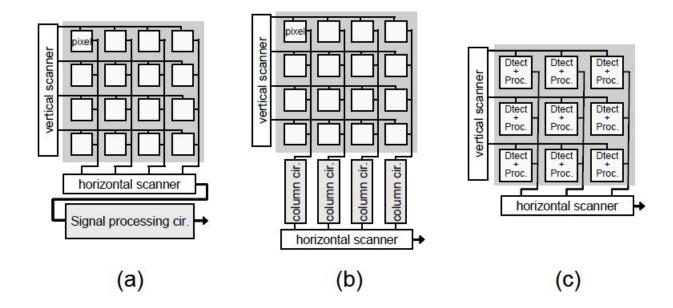

| 2.18 | Conceito básico dos sensores CMOS inteligentes. (a) Processamento a nível              |         |

|------|----------------------------------------------------------------------------------------|---------|

|      | de Chip , (b) Processamento a nível de coluna, e (c) processamento a nível             |         |

|      | de píxel Ohta (2008)                                                                   | 33      |

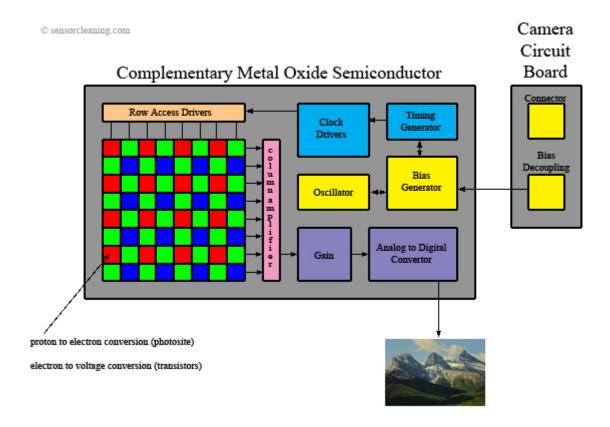

| 2.19 | Conjunto Sensor CMOS mais circuito de câmera (http://sensorcleaning.com,               |         |

|      | 2010)                                                                                  | 35      |

| 2.20 | Flexibilidade versus Performance de classes de processadores (Bobda, 2007).            | 44      |

| 2.21 | Estrutura de uma FPGA (Bobda, 2007)                                                    | 45      |

| 2.22 | Quatro tipos básicos de estruturas de FPGAs (Bobda, 2007) $\ \ldots \ \ldots \ \ldots$ | 47      |

| 3.1  | Placa de desenvolvimento DE2 70 (www.terasic.com, 2008)                                | 52      |

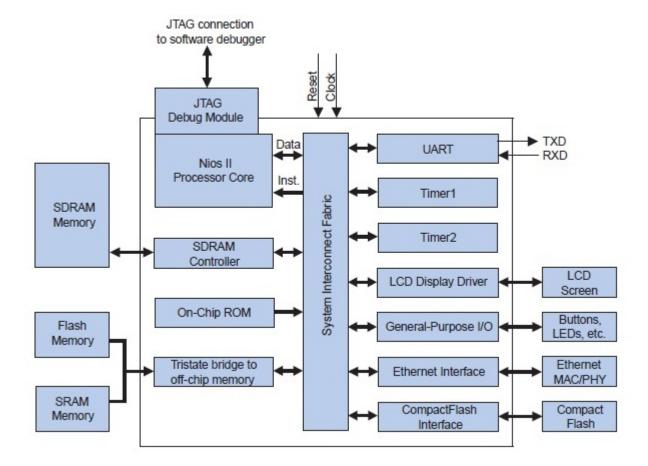

| 3.2  | Componentes do sistema com processador Nios II                                         | 54      |

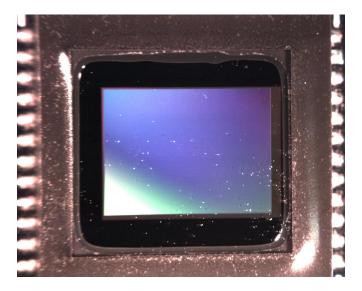

| 3.3  | Sensor CMOS Visto ao Microscópio                                                       | 56      |

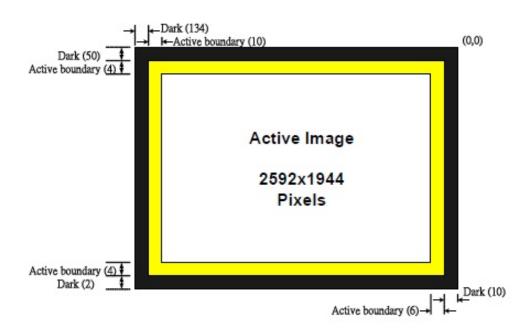

| 3.4  | Descrição do Vetor de Pixels (www.terasic.com, 2008)                                   | 56      |

| 3.5  | Câmera CMOS D5M conectada à placa de desenvolvimento DE2-70 (www.tera                  | sic.com |

|      | 2008)                                                                                  | 57      |

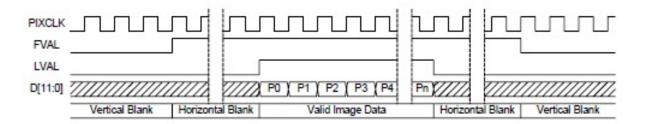

| 3.6  | Temporização Default de Saída do Frame (www.terasic.com, 2008)                         | 58      |

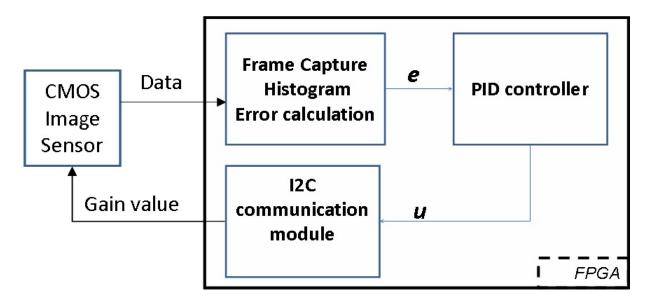

| 4.1  | Implementação do sistema utilizando FPGA                                               | 60      |

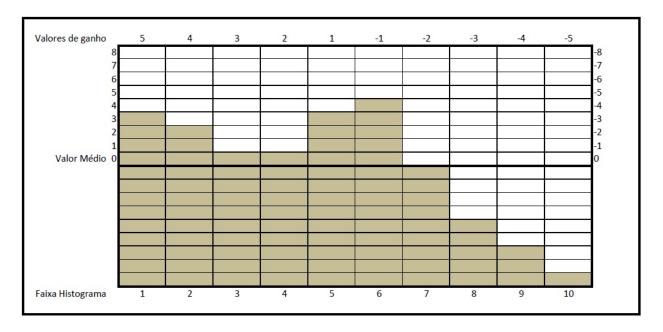

| 4.2  | Cálculo do Erro Através da Análise do Histograma                                       | 61      |

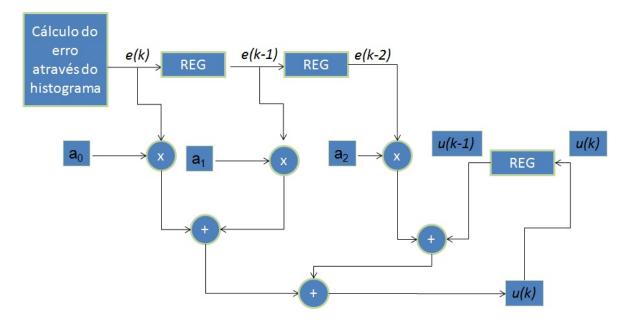

| 4.3  | Arquitetura simplificada do controlador PID                                            | 62      |

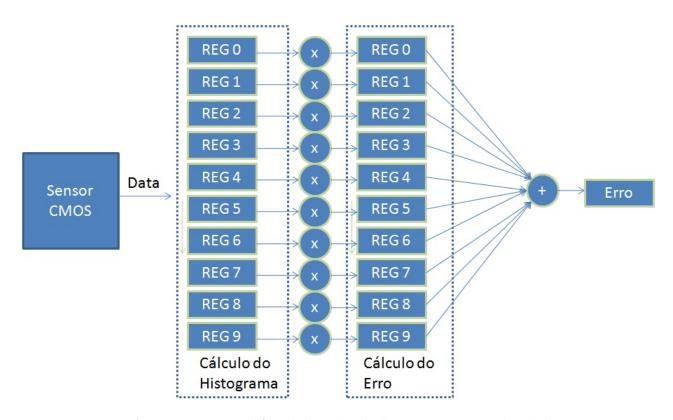

| 4.4  | Arquitetura simplificada do cálculo do histograma e cálculo do erro                    | 63      |

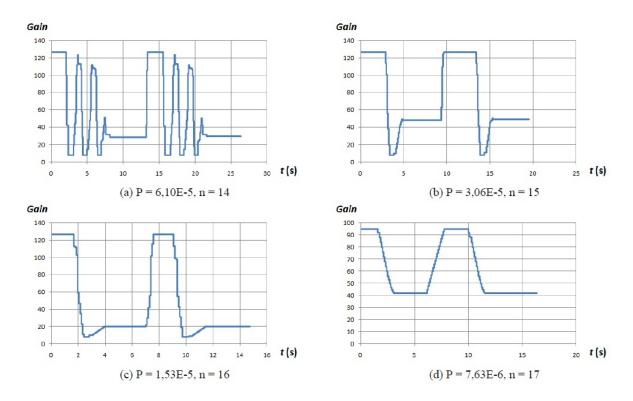

| 5.1  | Resposta do Sistema com variação do Ganho Proporcional                                 | 65      |

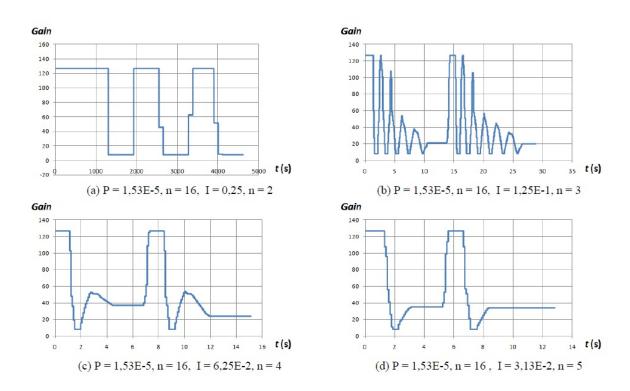

| 5.2  | Resposta do Sistema com variação do Ganho Integral                                     | 66      |

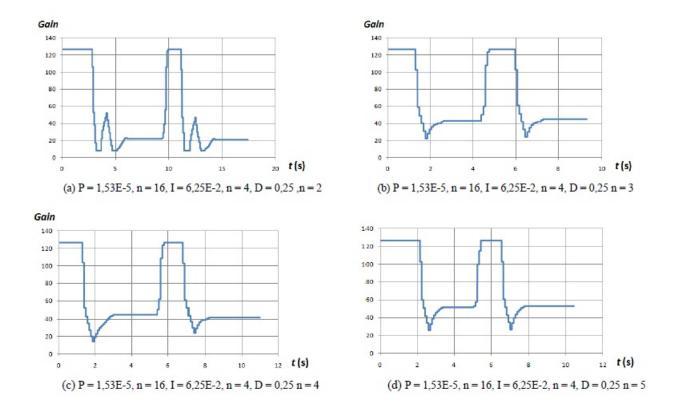

| 5.3  | Resposta do Sistema com variação do Ganho Derivativo                                   | 67      |

# Lista de Tabelas

| 2.1 | Exemplo de histograma (Filho e Neto, 1999)                          | 16 |

|-----|---------------------------------------------------------------------|----|

| 2.2 | CCD vs CMOS (Litwiller, 2005)                                       | 37 |

| 2.3 | Performance CCD vs CMOS (Litwiller, 2005)                           | 37 |

| 2.4 | O Caminho Tortuoso do Desenvolvimento dos Sensores CMOS (Litwiller, |    |

|     | 2005)                                                               | 38 |

| 3.1 | Características do dispositivo EP2C70F896C6N                        | 50 |

# Resumo

Este trabalho propõe um controlador PID (Proporcional, Integrador, Derivativo), implementado em hardware reconfigurável, para controle de ganho de uma câmera com sensor CMOS. O conceito utilizado é o de sistemas SoC (System-on-a-Chip). As principais funções realizadas pelo sistema são: Aquisição da imagem, montagem do histograma, análise do histograma, controle de ganho baseado na análise do histograma.

O sistema proposto tem como objetivo conter algumas funções básicas de controle de ganho que possam servir de base para construção de sistemas de visão computacional que possibilitem a otimização do tempo gasto na construção de novos sistemas, deixando o projetista concentrado na parte mais específica do sistema. O algoritmo de controle de ganho através da análise de histograma demonstrou ser além de funcional, altamente flexível, pois pode ser aplicado a qualquer câmera, independente do tipo do sensor. Este algoritmo pode ser aplicado a tipos diferentes de sensores, com diferentes taxas de aquisição e transmissão de imagens.

Este ambiente baseado em computação reconfigurável proporciona alta performance e flexibilidade no modo de implementação, possibilitando que o hardware seja configurado para satisfazer situações que exigem alto desempenho, que pode ser obtido através do paralelismo de operações. Esta arquitetura ainda possibilita a configuração de processadores que executam operações em software em conjunto com operações executadas em hardware.

O sistema final controla a câmera CMOS de maneira adequada às aplicações robóticas de tempo real.

# **Abstract**

This paper proposes a PID controller (Proportional, Integrator, Derivative), implemented in reconfigurable hardware to control a CMOS sensor camera gain. The concept used is the system SoC (System-on-a-Chip). The main functions performed by the system are: image acquisition, assembly of the histogram, histogram analysis, gain control based analysis of the histogram.

The proposed system aims to contain some basic gain control functions. These functions may serve as a basis for future construction of computer vision systems. This work will optimize the time spent in building new systems, leaving the designer free to concentrate on more specific development. The gain control algorithm through the analysis of histogram proved be functional, highly flexible, and it can be applied to any camera, regardless of the type of sensor. This algorithm can be applied to different types of image sensors with different acquisition and transmission rates.

This environment-based reconfigurable computing provides high performance and flexibility in implementation, enabling the hardware to be configured to meet situations that require high performance, which can be obtained through parallelism of operations. This architecture also enables the configuration of processors that perform software operations in conjunction with hardware operations.

The final system controls the CMOS camera accordingly to real-time robotic applications.

Capítulo

$\mathcal{I}$

# Introdução

Implementar um controlador de ganho geral para uma câmera CMOS demonstrou ser uma tarefa desafiadora, visto que a maioria das propostas e implementações apresentam abordagens diferentes como controladores de ganho a nível de pixel. Outro desafio se encontra na escassa literatura a respeito de controladores de ganho de câmeras com sensores CMOS, uma vez que a maioria dos métodos são de e de propriedade dos fabricantes, e que na sua maioria, já os oferece como funções automáticas para as câmeras.

### 1.1 Descrição do Sistema Proposto

O projeto propôs a implementação e a análise de um controlador PID (*Proporcional*, *Integral*, *Derivativo*) para controlar o ganho analógico de uma câmera CMOS de baixo custo. (R. Drausio, 2011)

O sinal de erro do controlador foi baseado na análise do histograma da imagem aquisitada pelo sensor.

Foi utilizada a placa de desenvolvimento DE2 70 da Terasic e uma câmera TRDBD5M, também da Terasic, que possui um sensor CMOS de 5 mega pixels. A arquitetura utilizada é reconfigurável, o que torna o seu desenvolvimento flexível.

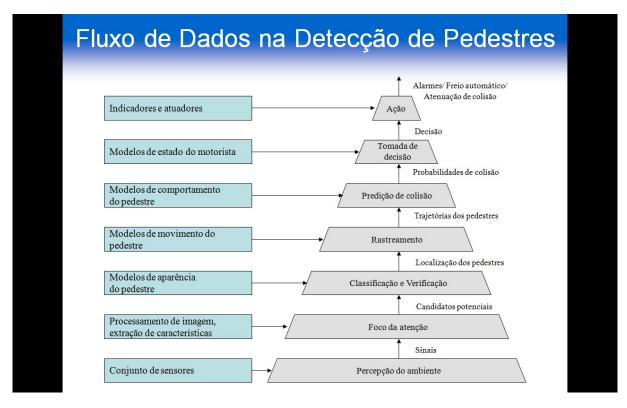

O controlador baseado em arquitetura SoC para controle de ganho será integrado a um ambiente para projeto e implementação de controle evolucionário embarcado de detecção de pedestres, como é mostrado na figura 1.1. Este ambiente vem sendo desenvolvido pelo Laboratório de Computação Reconfigurável - LCR do Instituto de Ciências Matemáticas e de Computação da Universidade de São Paulo. A base da pirâmide representa a percepção do ambiente e é constituída por um conjunto de sensores que são responsáveis pela percepção das condições ambientais. Esta etapa é de suma importância, pois é a base para o processamento futuro dos dados e a aplicação dos modelos propostos. O sistema de visão necessita lidar com diferentes condições como chuva, sol, neblina, faróis de automóveis, além de mudanças bruscas nestas condições, como situações de sobra como entrada e saída de túneis, sombras, etc.

Figura 1.1: Fluxo de Dados na Detecção de Pedestres (de Holanda, 2010)

O sistema proposto será divido em 4 etapas: a primeira realiza a montagem do histograma da imagem, a segunda analisa o histograma, a terceira é realizada pelo controlador PID que calcula o ganho necessário para a câmera e a quarta realiza a realimentação do ganho no sensor CMOS. Para cada função descrita acima, módulos específicos foram implementados em computação reconfigurável, sendo um módulo para cada função do sistema.

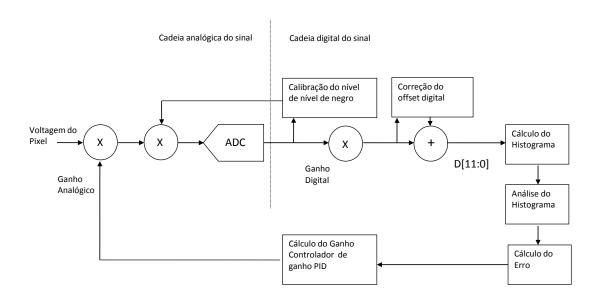

O caminho do sinal e do controle de ganho é mostrado na figura 1.2 Cada pixel do sensor realiza a leitura da luz ambiente, e o seu valor é transferido para um conversor analógico digital, passando por um multiplicador de ganho analógico, que é o nosso foco neste trabalho. Todas as outras etapas de controle de ganho, como calibração de nível de negro, ganho digital e correção de offset digital, foram desabilitadas.

Figura 1.2: Caminho do sinal analógico-digital e realimentação do ganho analógico, adaptada de (www.terasic.com, 2008)

## 1.2 Objetivos

Os Objetivos principais deste trabalho são:

Desenvolver um controlador PID em dispositivo FPGA, aplicado ao controle de ganho de uma câmera dotada de um sensor CMOS com a finalidade de servir de base para o desenvolvimento de módulos de visão computacional mais específicos aplicados a robôs móveis.

- 4

- Dominar a tecnologia da câmera CMOS (Complementary Metal Oxide Semiconductor), e dominar a tecnologia, linguagens e técnicas de programação de dispositivos reconfiguráveis;

- Contribuir com a evolução do ambiente para projeto e implementação de controle evolucionário embarcado de robôs móveis reconfiguráveis dinamicamente, que vem sendo desenvolvido pelo Laboratório de Computação Reconfigurável LCR do Instituto de Ciências Matemáticas e de Computação da Universidade de São Paulo;

## 1.3 Organização do Trabalho

O capítulo 2 apresenta a fundamentação teórica necessária para o desenvolvimento deste trabalho. Os assuntos abordados são referentes a controladores PID, histogramas, tecnologia de câmeras e hardware reconfigurável. O capítulo 3 descreve os recursos de hardware e software que são utilizados para a implementação e validação do sistema proposto. O capítulo 4 apresenta os módulos de análise de histograma e controle de ganho projetados para o trabalho e o capítulo 5 apresenta os resultados obtidos. No final são apresentadas as conclusões e sugestões para trabalhos futuros.

Capítulo

5 )) \_\_\_\_\_\_

# Fundamentação Teórica

Este capítulo apresenta, de maneira resumida, a fundamentação teórica dos temas predominantes deste projeto.

Os temas abordados são: controlador PID (Proporcional, Integrador, Derivativo), que é utilizado para o controle de ganho do sensor; histograma; tecnologia de sensores CMOS (Complementary Metal Oxide Semiconductor); tecnologia de hardware reconfigurável, com ênfase em dispositivos FPGA (Field Programmable Gate Array), sendo esta a tecnologia de hardware adotada para a implementação deste trabalho.

#### 2.1 Sistemas de Controle

Um sistema de controle é um conjunto de componentes que atuam conjuntamente e realizam comandos ou regulam um processo de forma a atingir uma saída desejada. Um sistema de controle é formado por três componentes principais: sensores, atuadores e um controlador. Os sensores medem as variváeis do processo ou do sistema e proveem informações de realimentação. Em controle digital, os sensores são qualquer componente capaz de converter uma grandeza física em uma tensão, que é então transformada em um valor digital e realimentada ao controlador. O controlador gera comandos que atuam em

resposta às informações recebidas e consiste em elementos computacionais que processam informações afim de atingir uma determinada resposta de todo o sistema. A função do controlador é assegurar que o sistema responda o mais rápido possível e ao mesmo tempo, permaneça estável sob todas as condições de operação. Os atuadores são responsáveis em transformar as respostas do controlador em ações de controle. Podem ser mecânicos, elétricos, eletro-mecânicos, químicos, etc. (Irfan, 1997).

#### 2.1.1 Controladores Analógicos

Sistemas de controle foram inicialmente implementados usando componentes analógicos como amplificadores operacionais, resistore e capacitores. A combinação destes elementos implementam estruturas semelhantes a filtros que modificam a frequência de resposta do sistema. Embora elementos de processamento analógico mais poderosos estejam disponíveis, como multiplicadores, eles não são geralmente usados devido ao seu elevado custo. Apesar de possuir elementos mais simples, controladores analógicos podem ser usados em sistemas de alta performance.

#### 2.1.2 Controladores Digitais

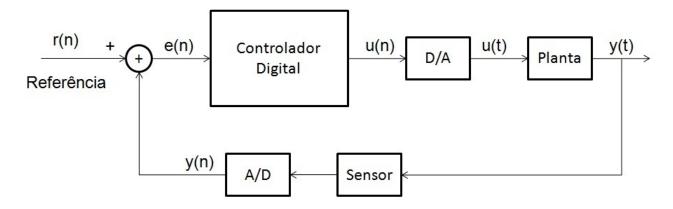

Com a performance e a confiabilidade inerente aos componentes digitais utilizados, como microcontroladores, microprocessadores, DSPs e FPGAs, controladores digitais estão cada vez mais presentes em nosso meio. Em um sistema de controle digital, o controlador é implementado em um circuito integrado que é responsável pelo processamento de sinal do sistema. No entanto os comandos do controlador são digitais e necessitam ser convertidos em sinais analógicos por um conversor Digital-Analógico. Da mesma maneira, as medidas dos sensores necessitam ser convertidas para um valor digital por um conversor Analógico-Digital. A figura 2.1 mostra o diagrama de blocos de um sistema de controle digital. O conversor D/A converte a saída digital do Controlador Digital, u(n), em um sinal analógico, u(t). A saída u(t), do conversor D/A necessita na maioria das vezes de amplificação de potência para levar a planta até o ponto de referêcia, r(n). A saída da Planta, y(t), é medida através de um sensor e convertida em um sinal digital, y(n), pelo conversor A/D. O sinal de realimentação é então subtraído do sinal de referência r(n) para

criar o sinal de erro e(n). O sinal de erro, e(n), é usado pelo controlador para calcular a correspondente ação de controle u(n).

Figura 2.1: Sistema de Controle Digital, adaptada de (Ahmed, 1997).

#### 2.2 Controlador PID

#### 2.2.1 Histórico

Nos últimos 70 anos controladores PID tem sido amplamente utilizados. Isto esta documentado no guia de referencia Muhidin e Zoran (L. Muhidin, 2000). A pesquisa e desenvolvimento de aplicações usando este tipo de controlador mostra uma dinâmica muito vasta. É estimado que na década passada foram publicados mais de 300 papers em jornais sobre teoria e aplicações de controladores PID.

A literatura sobre controladores PID e sua regulação é muito ampla. Uma breve referência aos desenvolvimentos feitos nas décadas recentes pode ser o trabalho de Morari e Zafíriou (M. Morari, 1989), onde os autores mostram que as tecnologias que usam Controle de Modelo Interno (IMC) levam ao controlador PID para a maioria dos modelos dos processos. Um controlador IMC PID equivalente pode ser conseguido através do uso da resposta em freqüência e do algoritmo dos últimos quadrados; isto foi provado por Wang ET AL (Q. G. Wang, 2000). Em 2001, Katebi e Moradi (M. R. Katebi, 2001) desenvolveram um controlador PID preditivo para processos SISO baseado no método de controle preditivo generalizado (GPC), a generalizacao para processos MIMO com representacoes polinomiais, foi feita em 2002 (M. H. Moradi, 2002). O desenvolvimentos desta tecnica foi realizada por Moradi e Johnson (M. H. Moradi, 2010). O uso de computação recon-

figurável no auto ajuste de controladores PID tem sido investigado com sucesso (Lima, 2004). Especificamente, podemos apontar a habilidade de redes neurais para modelar plantas, juntamente com algoritmos genéticos para a otimização dos critérios de controle.

Apesar de novos métodos específicos de regulação do controlador PID terem sido apresentados, para problemas específicos, técnicas clássicas como Ziegler and Nichols, 1942(J. G. Ziegler, 1942), ainda são amplamente utilizadas em uma grande gama de aplicações. Este método também é apontado como referência, por exemplo, pelo método desenvolvido em 1952 por Cohen e Coon, ou no método de feedback de Aström e Hägglund. Os algoritmos desenvolvidos usam tanto respostas temporais quanto resposta em freqüência do processo a ser controlado. Estas técnicas são freqüentemente usadas como referência para comparação de metodologias recentes.

#### 2.2.2 Conceito

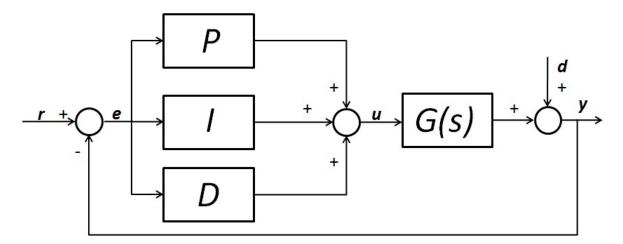

Um controlador típico PID paralelo, contínuo e de malha fechada é mostrado na figura 2.2

Os sinais r, e, u, d e y representam a referência r, o erro e, o sinal de controle u, o sinal de distúrbio d, e a saída do sistema y, respectivamente.

O bloco G(s) representa o sistema que queremos controlar.

Figura 2.2: Controlador PID contínuo, paralelo de malha fechada (Åström e Hägglund, 2006)

A lei de controle do controlador PID é definida em termos de 3 parâmetros, o ganho proporcional  $k_c$  o tempo integral  $t_i$  e o tempo derivativo  $t_d$ . No domínio do tempo, o

controlador PID pode ser descrito como a relação entre o sinal de controle e os sinais de erro, como mostra a equação 2.1

$$u(t) = k_c e(t) + \frac{1}{t_i} \int_0^t e(t)d(t) + t_d \frac{d}{dt} e(t)$$

(2.1)

#### 2.2.3 Termo Proporcional

O termo proporcional faz uma alteração na saída que é proporcional ao valor de erro atual. A resposta proporcional é ajustada, multiplicando-se o erro e(t) pela constante  $k_c$ , chamada de ganho proporcional.

O termo proporcional é dado por 2.2

$$k_c.e\left(t\right) \tag{2.2}$$

A alta do ganho proporcional resulta em uma grande mudança na saída para uma dada mudança no erro. Se o ganho proporcional é muito alto, o sistema pode se tornar instável. Em contraste, se o ganho proporcional é muito baixo, a ação de controle pode ser pequena ao responder a perturbações do sistema. Na maioria dos controladores existentes, o termo proporcional contribui com a maior parte da mudança de saída.

A figura 2.3 mostra a resposta de um sistema controlado por um controlador PID onde somente o ganho proporcional é variado. A referência representa o ponto de ajuste desejado para o sistema. As outras três curvas do gráfico representam a saída do sistema. Pode ser observado, que a medida em que o ganho aumenta, há uma diminuição do tempo de resposta e uma redução do erro de regime estacionário. Nota-se também, que dependendo do aumento no ganho, pode haver a formação de sobre-sinal.

#### 2.2.4 Termo Integral

A contribuição do termo integral é proporcional à magnitude do erro e da duração do erro. A integral em um controlador PID é a soma do erro instantânea ao longo do tempo e da compensação acumulada que deveria ter sido corrigido anteriormente. O erro acumulado é então multiplicado pelo ganho integral  $1/t_i$  e acrescentada à saída do

Figura 2.3: Resposta de um controlador PID para variações de ganho proporcional Kp controlador.

O termo integral é dada por 2.3

$$\frac{1}{t_i} \int_0^t e(t)d(t) \tag{2.3}$$

O termo integral acelera o movimento do processo no sentido de setpoint e elimina o erro de estado estacionário residual que ocorre com um controlador proporcional puro. No entanto, uma vez que o termo integral responde a erros acumulados do passado, pode levar o valor presente a ultrapassar o valor de referência.

A figura 2.4 mostra a resposta de um sistema controlado por um controlador PID onde somente o ganho integral é variado. O setpoint representa o ponto de ajuste desejado para o sistema. As outras três curvas do gráfico representam a saída do sistema. Pode ser observado, que a medida em que o ganho integral aumenta, há uma diminuição do tempo de resposta e uma redução do erro de regime estacionário. Quando o sensor de um sistema é susceptível a ruídos ou à interferência elétrica, ações de controle derivativas podem causar grandes flutuações de saída do sistema. Nestas circunstâncias, a melhor escolha de controlador seria o do tipo PI (proporcional mais integral) (Giorgini, 2001).

Figura 2.4: Resposta de um controlador PID para variações de ganho Integral Ki

#### 2.2.5 Termo Derivativo

O termo derivativo do controlador é calculado através da multiplicação do ganho derivativo  $t_d$  pela taxa de declividade do erro ao longo do tempo.

O termo derivativo é dado por 2.4

$$t_{d}\frac{d}{dt}e\left(t\right)\tag{2.4}$$

O termo derivado diminui a taxa de variação da saída do controlador. Controle derivativo é usado para reduzir a magnitude do sobre sinal produzida pelo componente integral e melhorar a estabilidade do controlador de processo combinado. No entanto, como podemos observar na figura 2.5 o termo derivado retarda a resposta transitória do controlador. Além disso, a diferenciação de um sinal amplifica o ruído e, portanto, este termo no controlador é altamente sensível ao ruído no sinal de erro, e pode causar um processo para tornar-se instável se o ruído e o ganho derivativo forem suficientemente grandes. Por isso uma aproximação para um diferencial com uma largura de banda limitada é mais comumente usado.

Os problemas de estabilidade e de sobre-sinal apresentados por controladores propor-

cionais com alto ganho, podem ser minimizados com a adição de um termo derivativo.

Figura 2.5: Resposta de um controlador PID para variações de ganho Derivativo Kd

## 2.2.6 Controlador PID Digital

Como ja mostrado, o controlador PID pode ser descrito como a relação entre o sinal de controle e os sinais de erro 2.5

$$u(t) = k_c e(t) + \frac{1}{t_i} \int_0^t e(t)d(t) + t_d \frac{d}{dt} e(t)$$

(2.5)

Para convertermos o controlador para sua forma discreta, afim de ser implementado em um sistema digital, o termo integral é aproximado por 2.6

$$\int edt = \sum e_i T \tag{2.6}$$

Fazendo o intervalo de amostragem pequeno suficiente podemos aproximar o termo diferencial por 2.7 onde e(n) e e(n-1) são os valores do sinal de erro para os intervalos de tempo n e n-1.

$$\frac{de}{dt} = \frac{e(n) - e(n-1)}{T} \tag{2.7}$$

Para tempos de amostragem pequenos  $t\theta$  a equação 2.5 pode ser expressa de forma discreta por equações diferenciais. O termo derivativo é simplesmente substituído pela equação diferença de primeira ordem e o termo integral é substituído por uma soma. A integração contínua pode ser discretizada tanto por aproximação retangular quanto por aproximação trapezoidal.

Integrando-se por aproximação retangular tem-se a equação 2.8:

$$u(n) = k_c[e(n) + \frac{t_0}{t_i} \sum_{i=0}^{n-1} e(i) + \frac{t_d}{t_0} (e(n) - e(n-1))]$$

(2.8)

Esta equação representa o algoritmo não recursivo de controle. Para a programação do controlador PID um algoritmo recursivo seria mais apropriado. O algoritmo recursivo se caracteriza por calcular a variável atual, u(n), baseada na variável calculada no tempo anterior, u(n-1) mais os termos de correção (ISERMANN, 1989).

Para se derivar a equação recursiva deve-se subtrair 2.9 de 2.8 representada a seguir.

$$u(n-1) = k_c[e(n-1) + \frac{t_0}{t_i} \sum_{i=0}^{n-2} e(i) + \frac{t_d}{t_0} (e(n-1) - e(n-2))]$$

(2.9)

Como resultado obtém-se 2.10 para o algoritmo recursivo do controlador PID.

$$u(n) = u(n-1) + a_0 e(n) + a_1 e(n-1) + a_2 e(n-2)$$

(2.10)

onde

$$a_0 = K_c (1 + \frac{t_d}{t_s}) (2.11)$$

$$a_1 = -K_c(1 + 2\frac{t_d}{t_s} - \frac{t_s}{t_i}) \tag{2.12}$$

$$a_2 = -K_c \frac{t_d}{t_c} \tag{2.13}$$

Os parêmetros Kc, ti e td são os parâmetros para ajuste do controlador PID, e t0 é o período de amostragem em segundos (K. Åström, 1995).

#### 2.2.7 Ajuste do controlador PID

Os métodos de avaliação dos parâmetros de ganho proporcional kc, do tempo integral ti e do tempo derivativo td são chamados métodos de ajuste do controlador PID

A sintonia do controlador PID digital pode ser feita aplicando técnicas para sistemas contínuos e discretizando os blocos, tendo em conta um determinado período de amostragem ou o tempo discreto de processamento do controlador.

A implementação de controladores digitais em FPGA permite atingir alguns requisitos como desempenho, baixo custo e facilidade de reconfiguração, que ainda não foram observados em DSPs (Processador Digital de Sinais). A abordagem endereça a solução de um tipo de SoC (Sistema em chip)(Åström e Hägglund, 2006).

Existem várias classes de ajustes de controladores PID, como Ziegler-Nichols, Cohen-Coon, etc. No desenvolvimento deste trabalho o controlador foi ajustado empíricamente, (tentativa e erro). O ajuste do controlador através de algum método já consagrado, pode ser alvo de um trabalho futuro.

### 2.3 Histograma

#### 2.3.1 Conceito

Compreender o que são, como funcionam e se familiarizar com os histogramas são provavelmente os passos mais importantes para trabalhar com imagens de uma câmera digital. Um histograma pode dizer se a imagem foi exposta corretamente, se o tipo de luz era dura ou suave e quais ajustes funcionam melhor em sua câmera. Esse conhecimento é essencial para se trabalhar com imagens digitais.

O histograma é possivelmente a ferramenta mais importante disponível para trabalhar com imagem digital.

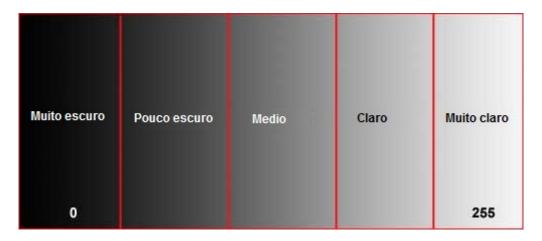

A figura 2.6 mostra uma classificação de níveis de brilho de uma imagem. Esta é a mesma classificação de um histograma onde os valores de conversão analógico digital são de 8 bits para uma imagem com cinco níveis de cinza. O valor máximo que um pixel pode atingir é 255, que indica um valor de alto brilho, e este é classificado no lado mais

a direita do histograma. Valores de baixo brilho (escuros) são colocados à esquerda do histograma, indicando baixos valores do conversor analógico digital para aquele pixel. O número de divisões é determinado pelo uso do histograma, e pelo número de bits do conversor analógico digital do sensor. Um histograma de um sensor que utiliza 8 bits pode ter ao máximo 255 faixas de valores, onde cada faixa indica um valor do conversor analógico digital para um dado pixel.

Figura 2.6: Exemplo de valores de conversão A/D de 8 bits para imagem com cinco níveis de cinza

O histograma de uma imagem é simplesmente um conjunto de números indicando o percentual de pixels naquela imagem que apresentam um determinado nível de cinza. Estes valores são normalmente representados por um gráfico de barras que fornece para cada nível de cinza o número (ou o percentual) de pixels correspondentes na imagem. Através da visualização do histograma de uma imagem obtemos uma indicação de sua qualidade quanto ao nível de contraste e quanto ao seu brilho médio (se a imagem é predominantemente clara ou escura). Cada elemento deste conjunto é calculado como na equação 2.14:

$$p_r(r_k) = \frac{n_k}{n} \tag{2.14}$$

onde:

$0 \le rk \le 1$

k = 0, 1, ..., L-1, onde L é o número de níveis de cinza da imagem digitalizada;

n = número total de pixels na imagem;

pr(rk) = probabilidade do k-ésimo nível de cinza;

nk = número de pixels cujo nível de cinza corresponde a k.

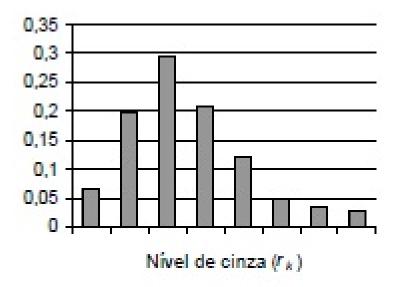

Os dados da tabela 2.1 correspondem a uma imagem de 128 x 128 pixels, com 8 níveis de cinza. O número de pixels correspondentes a um certo tom de cinza está indicado na segunda coluna, enquanto as respectivas probabilidades pr(rk) aparecem na terceira coluna. A representação gráfica equivalente deste histograma é mostrada na figura2.7. Um histograma apresenta várias características importantes. A primeira delas é que cada pr(rk) fornece, como sugere a notação, a probabilidade de um pixel da imagem apresentar nível de cinza rk. Portanto, um histograma nada mais é que uma função de distribuição de probabilidades e como tal deve obedecer aos axiomas e teoremas da teoria de probabilidade. Por exemplo, é possível verificar que na tabela 2.1 a soma dos valores de pr(rk) é 1, o que já era esperado (Filho e Neto, 1999).

| Nível de cinza (rk) | nk    | pr(rk) |

|---------------------|-------|--------|

| 0                   | 1120  | 0,068  |

| 1/7                 | 3214  | 0,196  |

| 2/7                 | 4850  | 0,296  |

| 3/7                 | 3425  | 0,209  |

| 4/7                 | 1995  | 0,122  |

| 5/7                 | 784   | 0,048  |

| 6/7                 | 541   | 0,033  |

| 1                   | 455   | 0,028  |

| Total               | 16384 | 1      |

Tabela 2.1: Exemplo de histograma (Filho e Neto, 1999).

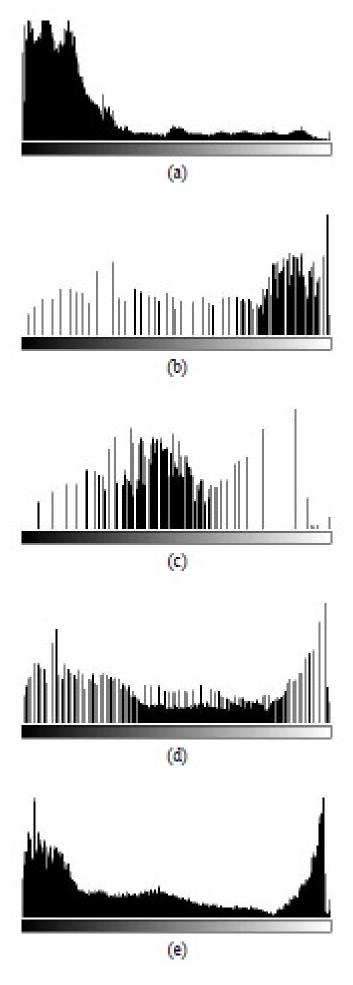

A figura 2.8 apresenta cinco exemplos de tipos de histogramas freqüentemente encontrados em imagens. O histograma (a) da figura 2.8 apresenta grande concentração de pixels nos valores mais baixos de cinza, correspondendo a uma imagem predominantemente escura. No histograma (b) da figura 2.8 os pixels estão concentrados em valores próximos ao limite superior da escala de cinza, caracterizando uma imagem clara. Na parte (c) da figura 2.8, os pixels estão agrupados em torno de valores intermediários de cinza, correspondendo a uma imagem de brilho médio. Na figura 2.8 nos histogramas (a), (b) e (c) a maioria dos pixels está concentrada em uma estreita faixa da escala de cinza, significando que as imagens correspondentes apresentam baixo contraste. A figura 2.8 (d) corresponde a uma imagem com pixels distribuídos ao longo de toda a escala de cinza. É comum dizer que uma imagem com estas características apresenta um bom contraste.

Figura 2.7: Exemplo de histograma para imagem com oito níveis de cinza (Filho e Neto, 1999)

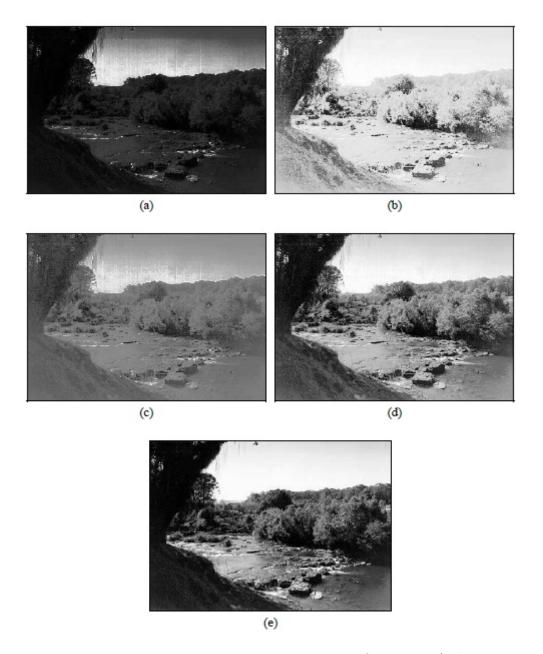

A figura 2.8 (e) mostra um histograma tipicamente bimodal, isto é, apresentando duas concentrações de pixels, uma delas em torno de valores escuros e outra na região clara do histograma. Pode-se dizer que a imagem correspondente apresenta alto contraste entre as duas concentrações, uma vez que elas se encontram razoavelmente espaçadas. Para verificar a relação entre imagens e respectivos histogramas, a figura 2.9 mostra cinco imagens monocromáticas cujos histogramas são aqueles da figura 2.8.

O conceito de histograma também é aplicável a imagens coloridas. Neste caso, a imagem é decomposta de alguma forma (por exemplo, em seus componentes R, G e B) e para cada componente é calculado o histograma correspondente.

Para computar o histograma de uma imagem monocromática, inicializa-se com zero todos os elementos de um vetor de L elementos, onde L é o número de tons de cinza possíveis. Em seguida, percorre-se a imagem, pixel a pixel, e incrementa-se a posição do vetor cujo índice corresponde ao tom de cinza do pixel visitado. Após toda a imagem ter sido percorrida, cada elemento do vetor conterá o número de pixels cujo tom de cinza equivale ao índice do elemento. Estes valores poderão ser normalizados, dividindo cada um deles pelo total de pixels na imagem.

Convém enfatizar que, embora o histograma de uma imagem forneça diversas informações qualitativas e quantitativas sobre ela (e.g. nível de cinza mínimo, médio e

Figura 2.8: Exemplo de histogramas (Filho e Neto, 1999)

Figura 2.9: Imagens correspondentes aos histogramas da figura 2.8 (Filho e Neto, 1999)

máximo, predominância de pixels claros ou escuros etc.), outras conclusões de caráter qualitativo (e.g. qualidade subjetiva global da imagem, presença ou não de ruído etc.) somente podem ser extraídas dispondo-se da imagem propriamente dita. (Filho e Neto, 1999)

#### 2.3.2 Especificação direta de histograma

Vamos entrar mais detalhadamente neste tópico, pois o sistema proposto baseia-se na análise direta do histograma da imagem, para determinar o erro do controlador e consequentemente o ganho do sensor CMOS. A teoria deste tópico é ligada ao trabalho e maiores detalhes serão fornecidos neste capítulo. O resultado final de avaliação do controle de ganho realizado, tem como base parâmetros do histograma.

Apesar de sua grande utilização em situações de aprimoramento de contraste de imagens, a equalização de histograma apresenta como principal limitação o fato de não permitir a especificação de nenhum parâmetro, a não ser a função de transformação, que, como vimos na Seção anterior, costuma ser a cdf da distribuição de probabilidade original. Existem situações, entretanto, em que seria desejável poder especificar que tipo de mudança se deseja sobre o histograma. Nestes casos, uma das possíveis técnicas é a especificação direta de histograma. Dada uma imagem (e seu histograma original) e o novo histograma desejado, o procedimento da especificação direta de histograma consiste em:

1) equalizar os níveis da imagem original usando a *cdf* discreta:

$$S_k = T(r_k) = \sum_{j=0}^k \frac{n_j}{n} = \sum_{j=0}^k p_r(r_j)$$

(2.15)

2) equalizar a função densidade de probabilidade discreta (isto é, o histograma) desejada(o):

$$v_k = G(z_k) = \sum_{j=0}^k p_z(z_j)$$

(2.16)

3) aplicar a função de transformação inversa aos níveis obtidos no passo 1:

$$Z = G^{-1}(s) (2.17)$$

No trabalho desenvolvido, o objetivo do controlador é obter um histograma cuja distribuição seja equalizada.

## 2.4 Tecnologia de Sensores de Imagem Digital

#### 2.4.1 Introdução

Em visão biológica, a retina é o sensor de imagem. A retina não apenas detecta sinais de imagem, mas também processa tarefas limitadas de baixo nível, com o intuito de melhorar a performance e o processamento de tarefas de outros estágios. Baseado em sistemas biológicos, a integração de processamento e sensoriamento para aumentar a performance do sistema é factível. Na figura 2.10 podemos ver a curva característica do diâmetro da pupila humana, em mm, pela luminância, dada em log de cândela por metro quadrado. Esta pode ser considerada a curva de controle do sistema de controle do nosso sensor de visão. Tradicionalmente, um sistema de processamento de visão é composto por módulos discretos; um sensor de imagem (normalmente uma âmera com sensor CCD ou CMOS), um sistema de conversão Analógico/Digital e um sistema de processamento digital.

Figura 2.10: Gráfico: Diâmetro da Pupila em Função da Luminância (Moon e Spencer, 1944)

Sensores computacionais (sensores de visão em outras palavras) são sistemas integrados muito pequenos, nos quais sensoriamento e processamento são unificados em um único circuito integrado VLSI (Integração de larga escala). Este circuito é projetado para uma aplicação específica, e muitas pesquisas tem sido realizadas sobre estes sensores. Existem várias propostas e implementações de sensores computacionais. Primeiramente, suas qualidades são sumarizadas a partir de vários pontos de vista, como vantagens vs. desvantagens, neurais vs. funcionais, tipo de arquitetura, analógico vs. digital, processamento global vs local, processamento vs. tamanho, e alguns novos paradigmas. Existem vários exemplos, entre eles processadores espaciais, temporais, conversores Analógico-Digital e sensores computacionais programáveis (KIYOHARU AIZAWA, 2004).

O desenvolvimento de tecnologias *VLSI* (Integração de larga escala) tem levado a produção de uma nova geração de sensores de imagem que integram processamento e sensoriamento em um único chip, e são chamados de sensores computacionais, sensores inteligentes ou circuitos de visão. Sensores computacionais são projetados para aplicações específicas.

Sensoriamento e processamento possuem interações de baixo nível. A maior vantagem dos sensores computacionais são seu tamanho e sua velocidade. Diferentemente do sistemas convencionais de processamento de imagens que são compostos por sistemas modulares e seguem o paradgima sensoriamento-processamento, a integração sensoriamento-processamento realiza uma integração em um system on a chip (Sistema dentro de um Circuito Integrado). A velocidade não é mais limitada pela taxa de video padrão, o que traz um impacto significante em aplicações de imagem em tempo real. Por exemplo, vamos citar as aplicações de estimação de movimento, que requerem um processamento pesado e que são limitadas a taxa convencional de transmissão de 30Hz, que é o gargalo da comunicação entre o sensor e o processador. Por causa da complexidade da estimação de movimento, que é determinada pelas dimensões do espaço de busca, uma taxa mais rápida de frames pode diminuir a dificuldade da tarefa. Se esta taxa pode ser muito mais alta que a taxa de transmissão de vídeo, a área de procura pode ser muito menor e a estimação de movimento pode se tornar muito mais fácil.

A tecnologia dos sensores de imagem também esta mudando. Até agora sensores

CCDs tem predominado, mas os sensores CMOS com pixels ativos estão emergindo como uma tecnologia competitiva. Embora os sensores CMOS passivos já tenham existido, os senores ativos são relativamente novos (T.Kobayashi e S.Ozawa, 1990) (K.Nohsoh e S.Ozawa, 1993).

A tecnologia dos sensores de imagem CCD e CMOS foi inventada no final dos anos 60, e início dos anos 70. Na época, a performance dos sensores CMOS era limitada pela tecnologia de litografia disponível, o que permitiu que os sensores CCDs dominassem os primeiros 25 anos seguintes. O argumento original para a renovação dos sensores CMOS como competidores dos sensores CCDs foi baseada em algumas idéias:

- 1 Os processos de litografia e o controle dos processos de fabricação atingiram níveis que logo permitirão aos sensores CMOS fornecerem uma qualidade de imagem próxima a dos sensores CCD.

- 2 A capacidade de integração de funções em um único componente criando uma camera-on-a-chip ou um sistema em um único chip.

- 3 Baixo consumo de energia.

- 4 Sistema de aquisição de imagem com tamanho reduzido, como resultado da integração de componentes e consumo de energia.

- 5 A possibilidade de utilizar a mesma linha de produção CMOS para fabricar as funções lógicas principais e a memória de maneira integrada, o que gera uma grande economia de escala para os fabricantes de sensores CMOS.

- 6 Outros argumentos que favorecem a tecnologia CMOS incluem a operação com uma única fonte de energia, e a possiblidade de fabricação das regiões dos elementos de leitura juntamente a outros componentes do sistema.

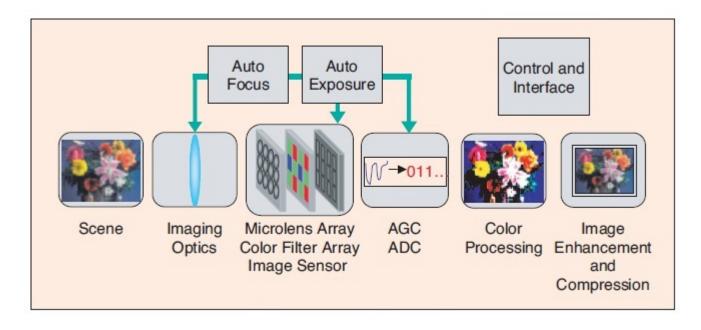

Um diagrama de blocos de um sistema de imagem digital é mostrado na figura 2.11, e um esquemático com as principais características dos senores CCD e CMOS são mostrados na figura 2.12.

Primeiro a cena é focada no sensor através das lentes do sensor. O sensor composto por um vetor bi-dimensional de pixels converte a luz incidente na sua superfície em um vetor de sinais eletrônicos. Estes sinais eletrônicos são lidos do sensor e digitalizados por um conversor analógico-digital (ADC). Um processamento de sinais considerável é

Figura 2.11: Sistema digital de imagem (A. El Gamal, 2005)

Figura 2.12: Sensores CCD movem a carga gerada pelos fótons de pixel a pixel até convertê-la em voltagem em uma saída. Sensores CMOS convertem a carga em voltagem dentro de cada pixel (Litwiller, 2005)

empregado para processar a cor, a qualidade, e a compressão da imagem. Outros tipos de processamento e controle são empregados para realizar o auto-foco, auto-exposição e controles gerais da câmera. Apesar de cada componente mostrado na figura ter um papel importante, o sensor é o componente chave para determinar o limite de performance final(A. El Gamal, 2005).

Atualmente existem diversos tipos de sensores disponíveis no mercado, sendo que cada qual é caracterizado pela tecnologia que utiliza, consumo de energia, qualidade da imagem, velocidade de captura de *frames*, tamanho, custo e etc.. Dentre os sensores de imagem mais utilizados atualmente estão os de tecnologia CCD e CMOS (Company, 2008a) que são apresentados nas seções seguintes.

# 2.4.2 Sensor de Imagem CCD

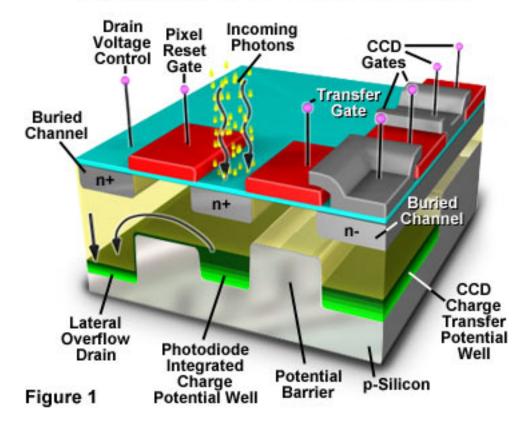

CCD é a abreviação para *charge-coupled device* (dispositivo de carga acoplado). Sensores de imagem CCD são circuitos integrados feitos de silício, e consistem de uma densa matriz de fotodiodos, que operam convertendo energia da luz, na forma de fótons, em carga elétrica (Flora M. Li, 2004).

Como muitas tecnologias, os sensores CCD (Dispositivo de Carga Acoplada) começaram como um tipo de desenvolvimento e terminaram em algo completamente diferente do proposto inicialmente. Inventado no final dos anos 60, por pesquisadores dos Laboratórios Bell, era inicialmente um novo tipo de circuito de memória de computador, e foi apresentado em 1970 para essa finalidade. Logo ficou claro que os dispositivos CCD tinham várias outras aplicações potenciais, incluindo processamento de sinais e imagem. Quanto ao campo de imagens, a sensibilidade à luz do silício, que responde a comprimentos de onda menores que 1.1um ( a luz visível fica entre 0.4um e 0.7um). A promessa que o circuito CCD serviria para a construção de memórias desapareceu, mas sua habilidade de detectar a luz tornou a tecnologia CCD a primeira a ser usada em sensores de imagem. De maneira similar ao circuitos integrados (IC), CCDs começaram como finas camadas de silício que são processadas em uma série de processos elaborados, que definem várias funções dentro do circuito. Cada fatia contém vários circuitos integrados (IC) idênticos, cada qual pode ser montado em um dispositivo funcional. Circuitos selecionados, basea-

dos em uma variedade de testes iniciais, são cortados a partir desta fatia e acoplados a outros circuitos ou sistemas (Company, 2008a).

Quando um fóton ultravioleta, visível ou infravermelho chega a um átomo do silício na foto célula (fotodiodo ou pixel) do CCD, produzirá normalmente um elétron livre e um vazio criado pela ausência momentânea do elétron na malha cristalina do silício. O elétron livre mantêm-se então num poço potencial (situado dentro da área do silício conhecida como a camada do depleção), enquanto que o vazio é transferido e eventualmente deslocado para o substrato do silício. Os pixéis são isolados electronicamente dos seus vizinhos por canais de paragem, que se formam por disseminação de ións de Boro através de uma máscara num substrato de silício do tipo p.

Esta ação permite a transmissão dos elétrons gerados através dos registradores até que encontrem o circuito de leitura. O sinal de saida é então transferido para um computador para a geração ou processamento da imagem.

A figura 2.13 mostra a construção típica de um sensor CCD, que consiste em camadas de semi-condutores que são conectadas por uma rede de controle de transferência de sinal, que realiza a transferência de cargas dos pixels para o circuito de saída.

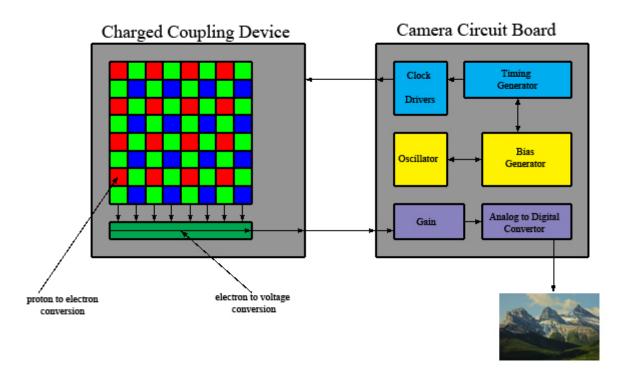

A tecnologia de sensores de imagem CCD foi inventada em 1970 por Willard Boyle e George Smith no laboratório da Bell, nos Estados Unidos (Boyle e Smith, 1970). Deste então, vem sendo utilizada em grande escala em produtos, incluindo máquina de fax, fotocópias, câmeras, scanners e celulares. A figura 2.14 mostra um conjunto sensor CCD mais hardware genérico de uma câmera.

O CCD é composto por milhares (ou milhões) de *pixels* ou células sensitivas à luz que são capazes de produzir uma carga elétrica proporcional ao montante da luz que elas recebem. Normalmente, os *pixels* são organizados em uma simples linha ou numa matriz bi-dimensional composta por linhas e colunas. Em scanners, por exemplo, os *pixels* são organizados numa linha, neste caso, é necessário mover o CCD sobre a imagem (ou vice versa). Já as câmeras digitais são formadas por uma matriz de *pixels* bi-dimensional, dessa forma, uma imagem bi-dimensional pode ser capturada numa única revelação.

Um dos principais parâmetros de um CCD é a resolução, que é igual ao número total de *pixels* existentes na área sensitiva à luz do dispositivo. Um dos primeiros dispositivos

# Anatomy of a Charge Coupled Device (CCD)

Figura 2.13: Anatomia de um Sensor CCD (www.circuitstoday.com, 2010)

© sensorcleaning.com

Figura 2.14: Conjunto Sensor CCD mais circuito de câmera (http://sensorcleaning.com, 2010)

CCD de matriz, desenvolvido por Fairchild em 1974, possuía resolução de 100x100 pixels (de Oregon, 2003). Atualmente, encontram-se dispositivos com resolução de aproximadamente 9000x7000, ou seja, 63 milhões de pixels.

Dispositivos CCD são circuitos integrados que possuem uma janela de vidro que permite a luz chegar até o silício do chip. Os CCD são fabricados utilizando a tecnologia MOS (Metal-Oxide-Semiconductor), onde cada *pixel* pode ser pensado como sendo um capacitor MOS que converte fótons (luz) em carga elétrica (elétron), sendo esta carga armazenada para uma leitura posterior.

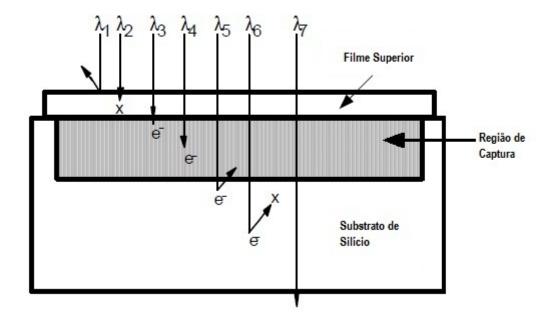

# 2.4.3 Convertendo Fótons em carga elétrica - Efeito Fotoelétrico

Uma imagem é aquisitada quando luz, em forma de fótons, atinge o vetor de pixels. A energia associada a cada fóton é absorvida pelo silício e provoca uma reação. Esta reação leva a criação de um vazio elétrico O funcionamento dos sensores CCD baseiase no efeito fotoeléctrico. Algumas substâncias têm a propriedade de absorver fótons e libertar no processo um elétron Quando um elétron recebe uma energia luminosa ele se excita e emite um fóton luminoso Na verdade, a oscilação do nível de energia do elétron quando recebe a partícula de luz é que origina a diferença de potencial que gera corrente elétrica nos eletródos do CCD O número de elétrons coletados por cada pixel é linearmente dependente do nível de luz e do tempo de exposição e é não-linearmente dependente do comprimento de onda da luz. Muitos fatores podem afetar a habilidade de detectar um fóton. Filmes finos de materiais depositados intencionalmente no silício durante a fabricação podem criar uma maior tendência a absorvição ou reflexão da luz. Fótons são absorvidos em diferentes profundidades dentro do silício, dependendo de seu comprimento de onda. Existem situações nas quais os elétrons excitados pelos fótons não podem ser detectados por causa da localização em que foram criados dentro do silício. A figura 2.15 mostra a interação dos fótons e seus respectivos comprimentos de onda com o substrato de silício.

Figura 2.15: Interação Fótons, Comprimento de Onda e Silício (Company, 2008b)

# 2.4.4 Processo de Leitura de Carga

O processo de leitura de carga é realizado em dois estágios, primeiro a carga do *pixel* é transferida através da matriz de *pixels* e depois a carga do *pixel* é armazenada em um registrador antes de ser digitalizada (Taylor, 1998).

O primeiro processo, a transferência de carga depende do número de *gates* de que cada *pixel* é composto. Assim, as técnicas de transferência são chamadas de *two-phases* (dois *gates*), *three-phases* (três *gates*) ou *four-phases* (quatro *gates*).

Tomando como exemplo o processo three-phases (Company, 2008a), visto na figura 2.16, a carga está armazenada no gate  $\emptyset 1$  enquanto que os gates  $\emptyset 2$  e  $\emptyset 3$  estão no estado bloqueado. O gate  $\emptyset 2$  é trazido para o nível alto e logo em seguida o gate  $\emptyset 1$  vai para o nível baixo. Agora, a carga está armazenada no gate  $\emptyset 2$  e é transferida para o gate  $\emptyset 3$ , manipulando os gates  $\emptyset 2$  e  $\emptyset 3$  da mesma maneira que foi realizada anteriormente. O ciclo de transferência é completado quando a carga é transportada para o gate  $\emptyset 1$  do próximo pixel.

Já o segundo estágio do processo de leitura de carga ocorre após cada linha de *pixels* ter sua carga transferida para a próxima linha. Além das linhas de *pixels*, existe no topo e/ou na base da matriz de *pixels* uma linha adicional chamada de registrador de leitura, que

Figura 2.16: Técnica three-phases de transferência de carga (Company, 2008b)

armazena as cargas dos *pixels* localizados no topo da matriz quando uma transferência entre linhas é realizada. A carga armazenada no registrador de leitura é enviada para um conversor ADC (Analog to Digital Converter) e posteriormente armazenada numa memória.

# 2.4.5 Arquitetura da Matriz de Pixels CCD

Geralmente as arquiteturas dos dispositivos CCD pertencem a uma das quatro categorias: full frame, frame transfer, split frame transfer e interline transfer (Taylor, 1998). A seguir estas quatro categorias são descritas e apresentadas através da figura 2.17.

- Full Frame: A imagem é transferida diretamente da seção da imagem do sensor ao registrador de leitura. No entanto, somente uma simples linha de pixels por vez pode ser transferida para o registrador de leitura, enquanto que o restante dos pixels da imagem deve aguardar. Durante este período, os pixels que ainda não foram lidos da matriz continuam armazenando informações da imagem, isso pode distorcer e borrar a imagem. Uma solução para este problema é proteger da luz a região de captura da imagem mecanicamente através de uma cobertura (Company, 2008a).

- Frame Transfer: O dispositivo com esta arquitetura utiliza uma seção de armazenamento protegida da luz do mesmo tamanho da matriz de pixels. Após o tempo de

integração da imagem, a imagem capturada é transferida para a seção adjacente de armazenamento. Enquanto a próxima cena está sendo capturada, a cena capturada anteriormente é transferida para o registrador de saída (paralelismo de operações). Durante a transferência da imagem capturada para a seção de armazenamento, é necessário proteger a matriz de *pixels* da luz para evitar os mesmo problemas citados na *full frame*.

- Split Frame Transfer: Este tipo de dispositivo é semelhante ao frame transfer, exceto pelo fato de que a seção de armazenamento é dividida em duas partes, sendo que cada parte contém um registrador de saída. Esta arquitetura é vantajosa, pois permite transferir a imagem da seção de armazenamento ao registrador de saída com a metade do tempo gasto na arquitetura frame transfer.

- Interline Transfer: Nesta arquitetura o dispositivo é composto por colunas de pixels e por colunas de registradores protegidos da luz de forma intercalada. No final do tempo de integração, a imagem capturada é transferida rapidamente para as colunas de registradores. Enquanto um novo frame é capturado, a carga armazenada nas colunas de registradores são transferidas para os registradores de saída. Este tipo de arquitetura não requer o uso de mecanismos para proteção da luz, visto que a imagem capturada é transferida diretamente às colunas de registradores.

Figura 2.17: Arquitetura de dispositivos CCD (Taylor, 1998)

# 2.4.6 Sensor de Imagem CMOS