LUCAS COMPASSI SEVERO

ULV and ULP active-RC filters combining single-stage OTA and negative input transconductance for low energy RF receivers

> São Paulo 2019

LUCAS COMPASSI SEVERO

### ULV and ULP active-RC filters combining single-stage OTA and negative input transconductance for low energy RF receivers

Thesis presented to the Polytechnic School of the University of São Paulo in partial fulfillment of the requirements for the degree of Doctor of Science.

Concentration Area: Microelectronics

Supervisor: Prof. Dr. Wilhelmus A. M. Van Noije Autorizo a reprodução e divulgação total ou parcial deste trabalho, por qualquer meio convencional ou eletrônico, para fins de estudo e pesquisa, desde que citada a fonte.

|         |                   | ado e corrigido em relação à versão original, sob<br>a do autor e com a anuência de seu orientador. |

|---------|-------------------|-----------------------------------------------------------------------------------------------------|

| São Pa  | ulo, <u>18</u> de | Felereite de 2019                                                                                   |

| Assinat | ura do autor:     | Lucos C. Servis                                                                                     |

| Assinat | ura do orientad   | or:                                                                                                 |

#### Catalogação-na-publicação

Severo, Lucas Compassi ULV and ULP active-RC filters combining single-stage OTA and negativeinput transconductance for low energy RF receivers / L. C. Severo – versão corr. – São Paulo, 2019.

158 p.

Tese (Doutorado) - Escola Politécnica da Universidade de São Paulo. Departamento de Engenharia de Sistemas Eletrônicos.

1.Ultra-low voltage 2.Ultra-low power 3.Single-stage unbuffered amplifiers 4.Negative input transconductor 5.Low Energy RF receivers I.Universidade de São Paulo. Escola Politécnica. Departamento de Engenharia de Sistemas Eletrônicos II.t. LUCAS COMPASSI SEVERO

### Filtros RC-Ativo ULV e ULP combinando OTA de único estágio e transcondutância negativa de entrada para receptores RF de baixa energia

Tese de doutorado apresentada à Escola Politécnica da Universidade de São Paulo como requisito parcial para a obtenção do título de Doutor em Ciências.

Área de Concentração: Microeletrônica

Orientador: Prof. Dr. Wilhelmus A. M. Van Noije

This work is dedicated to my son Thomas, my wife Tanísia, my parents Altamir and Marli, and my sister Tamíris.

## Acknowledgements

I would like to thanks to Professor Wilhelmus Adrianus Maria Van Noije for the opportunity in work as a Ph.D. candidate at the Polytechnic School of the University of São Paulo and by all the challenges imposed to me that have collaborated significantly in the improvements of my professional abilities.

I would like to thanks to the Federal University of Pampa for the opportunity of being on leave from the university by 3.5 years that made possible working full time in the Ph.D. studies and to the CNPq research agency for support to this work.

I would also like to thanks to professors João A. Martino e Paula G. Der Agopian for all the help in the CMOS transistor characterization, to the IMEC Free-mini@asic and to the MOSIS Educational programs for the free integrated circuit fabrications and to professors João N. Soares Júnior and Márcio C. Schneider for all the suggestions gave me at the qualification exam.

I would like to thanks to all the members of the DMPSV department of the LSI at USP, especially to Silvana, for all the conversations at the coffee time and commemoration during my stay in São Paulo. Finally, I thanks to my wife Tanísia for all the help and understanding during this shortage of time phase of my life.

Available energy is the main object at stake in the struggle for existence and the evolution of the world. Ludwig Edward Boltzmann

## Resumo

Este trabalho propõe novas topologias de circuitos e técnicas de projeto para filtros ativos e amplificadores de ganho programável (PGA) com operação em ultra baixa tensão (ULV) e ultra-baixa potência (ULP). Os receptores de RF do tipo Bluetooth de baixa energia (BLE), utilizados nos circuitos de internet das coisas (IoT), são as aplicações alvo dos circuitos propostos neste trabalho. Na faixa de ULV são utilizados filtros do tipo RC-ativo, uma vez que possuem uma maior linearidade em relação aos filtros do tipo  $q_m$ C. A operação em ULP é alcançada neste trabalho utilizando uma nova topologia de amplificador operacional de transcondutância (OTA), com único estágio, que apresenta uma alta eficiência e reduzida sensibilidade às variações de processo, tensão e temperatura (PVT). O baixo ganho de tensão do amplificador de estágio único e os efeitos das cargas resistivas de realimentação são compensados usando um transcondutor negativo, robusto a variações em PVT, conectado às entradas do OTA. A faixa dinâmica dos circuitos é elevada usando topologias totalmente diferenciais e as taxas de rejeição de modo comum e de fonte de alimentação são melhoradas utilizando circuitos de realimentação de modo-comum. Para possibilitar a operação na faixa de ULV todos os circuitos usam apenas dois transistores empilhados e o nível de inversão do canal é elevado através da polarização direta do substrato. Neste trabalho são propostas também uma ferramenta de análise do ponto de operação do transistor, baseando-se na simulação elétrica, e algumas metodologias de projetos para circuitos operando em ULV. Os circuitos e metodologias desenvolvidos foram utilizados para o projeto de um filtro passa-faixa complexo RC-ativo de terceira ordem, um amplificador de ganho programável e um filtro biquadrático do tipo Tow-Thomas com ganho programável, compatíveis com receptores de RF do padrão BLE. Para a implementação do PGA, uma nova topologia de transconductor negativo programável foi desenvolvida para permitir a compensação ótima do amplificador operacional em todos os modos de ganho. Todos os circuitos foram projetados para operar com uma tensão de alimentação de 0,4 V e foram prototipados em processos de fabricação CMOS e BiCMOS de 180 nm e 130 nm, respectivamente. Os resultados experimentais e de simulação pós-layout demonstram uma operação adequada em 0,4 V, uma ultra-baixa dissipação de potência, atingindo o mínimo de 10.9  $\mu$ W/polo, e a melhor figura-de-mérito (FoM) em relação aos outros filtros ativos e amplificadores disponíveis na literatura.

**Palavras-chaves**: Ultra-Baixa Tensão, Ultra-Baixa Potência, Ampificador de estágio único, transconductor negativo de entrada, Robustez às variações PVT, Receptores RF de baixa energia, Internet das coisas.

### Abstract

This thesis proposes novel circuit topologies and design techniques of ultra-low voltage (ULV) and ultra-low power (ULP) active-filters and programmable gain amplifiers (PGA) suitable for the Bluetooth low energy (BLE) RF receivers used in the Internet of Things (IoT) applications. The active-RC filters are preferred to the  $g_m$ -C topologies at the ULV operation due to its improved linearity. However, the closed-loop operation increases the operational amplifier required voltage gain and its capacity to drive the resistive feedback load. In this work, the ULP dissipation is obtained by proposing a very efficient single-stage inverter-based operational transconductance amplifier (OTA) and a proper forward bulk biasing to reduce the sensitivity to process, voltage and temperature (PVT) variations. The low voltage gain and the resistive load effects on the single-stage OTA are completely compensated by using a PVT robust negative transconductor connected at the OTA inputs. The dynamic range is increased by using fully-differential topologies and common-mode feedback to improve the common-mode and power supply rejection rates. The operation at the ULV range is reached by using only two-stacked transistors in all the circuit implementations and bulk forward bias in some transistors to reduce the threshold voltage and to increase the channel inversion level. An operation point simulation-based tool and some design methodologies are also proposed in this work to design the ULV circuits. The proposed circuits were used to design a third-order active-RC complex band-pass filter (CxBPF), a programmable gain amplifier (PGA) and a Tow-Thomas biquad, with integrated programmable gain capability, suitable for BLE RF receivers. The PGA implementation uses a new programmable input negative transconductor to obtain the optimal closed-loop amplifier compensation in all the gain modes. The circuits were designed to operate at the power supply voltage of 0.4 V and are prototyped in 180 nm and 130 nm low-cost CMOS and BiCMOS process, respectively. The experimental and post-layout simulation results have demonstrated the proper ULV operation at 0.4 V, the ultra-low power dissipation down to 10.9  $\mu W/pole$  and the best figure-of-merit (FoM) among the state-of-the-art active-filters and amplifiers from the literature.

**Key-words**: Ultra-low Voltage, Ultra-low Power, Single-stage unbuffered amplifiers, Negative input transconductor, PVT robust, Low Energy RF receivers, Internet of Things.

# List of Figures

| Typical RF receiver architectures: (a) Zero-IF, and (b) Low-IF                          | 25                                                                                                                             |

|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| The basic cell of an active-RC filter implementation using operational                  |                                                                                                                                |

| amplifiers: (a) single-ended and (b) fully-differential                                 | 29                                                                                                                             |

| The measured drain current density $(I_D/(W/L))$ related to the $V_{GS}$ and            |                                                                                                                                |

| $V_{DS}$ voltages of the test transistors M1 and M2: (a) $I_D/(W/L) \times V_{GS}$      |                                                                                                                                |

| linear, (b) $I_D/(W/L) \times V_{GS}$ logarithmic, (c) $I_D/(W/L) \times V_{DS}$ linear |                                                                                                                                |

| and (d) $I_D/(W/L) \times V_{DS}$ logarithmic.                                          | 30                                                                                                                             |

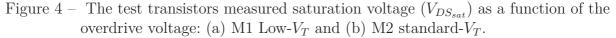

| The test transistors measured saturation voltage $(V_{DS_{sat}})$ as a function         |                                                                                                                                |

| of the overdrive voltage: (a) M1 Low- $V_T$ and (b) M2 standard- $V_T$                  | 33                                                                                                                             |

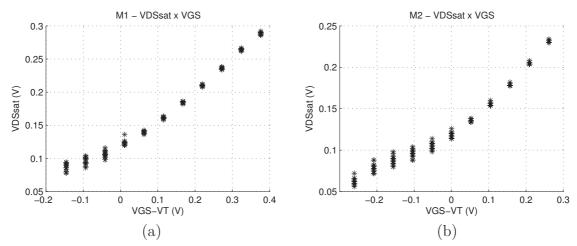

| The test transistors threshold voltage $(V_T)$ as a function of the $V_{BS}$            |                                                                                                                                |

| voltage, considering the measured results and Eq. 2.4 with $\gamma$ equal to            |                                                                                                                                |

| 0.35 $V^{1/2}$ : (a) M1 Low- $V_T$ and (b) M2 standard- $V_T$ .                         | 34                                                                                                                             |

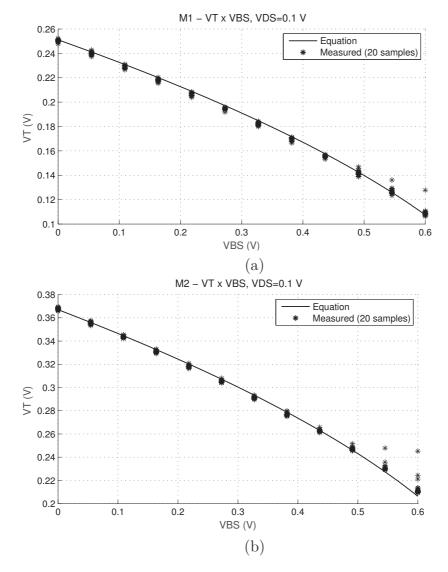

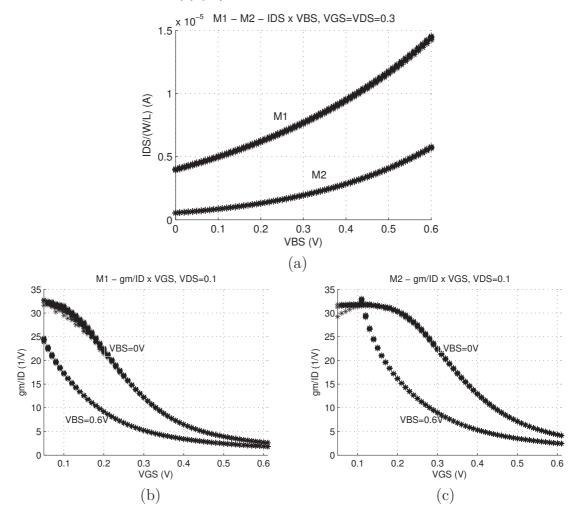

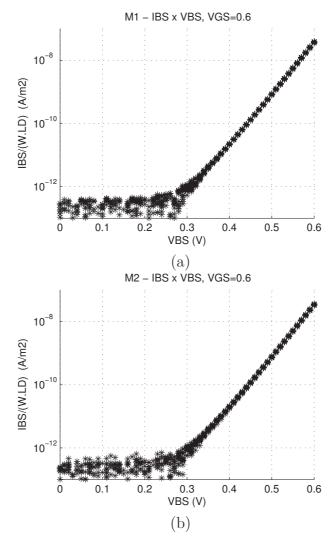

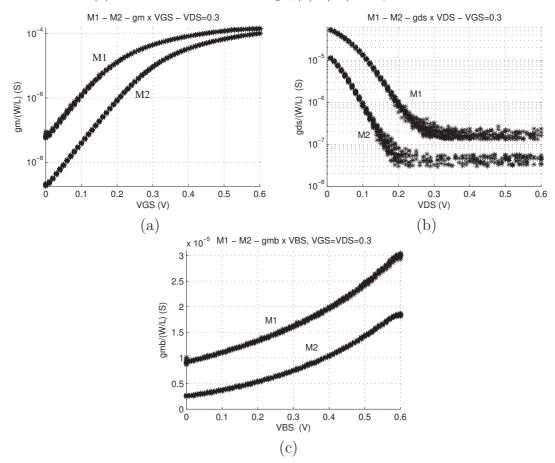

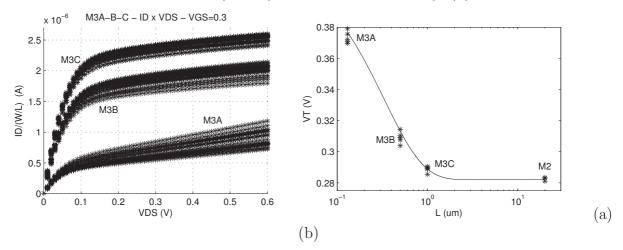

| The effects of the $V_{BS}$ voltage on the drain current density and on the             |                                                                                                                                |

| transistor efficiency: (a) $(I_D/(W/L)) \ge V_{BS}$ of the M1 and M2 transistor,        |                                                                                                                                |

|                                                                                         | 35                                                                                                                             |

|                                                                                         |                                                                                                                                |

|                                                                                         |                                                                                                                                |

|                                                                                         | 36                                                                                                                             |

|                                                                                         |                                                                                                                                |

|                                                                                         |                                                                                                                                |

|                                                                                         | 07                                                                                                                             |

|                                                                                         | 37                                                                                                                             |

|                                                                                         | 20                                                                                                                             |

|                                                                                         | 39                                                                                                                             |

|                                                                                         |                                                                                                                                |

|                                                                                         | 40                                                                                                                             |

| -                                                                                       | 40<br>45                                                                                                                       |

|                                                                                         | 10                                                                                                                             |

|                                                                                         |                                                                                                                                |

|                                                                                         |                                                                                                                                |

|                                                                                         | 49                                                                                                                             |

|                                                                                         | 10                                                                                                                             |

|                                                                                         |                                                                                                                                |

|                                                                                         |                                                                                                                                |

|                                                                                         | 51                                                                                                                             |

|                                                                                         | The basic cell of an active-RC filter implementation using operational amplifiers: (a) single-ended and (b) fully-differential |

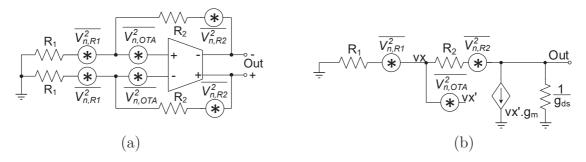

| Figure 14 – | Active integrator using negative input transconductance and single-stage        | 50 |

|-------------|---------------------------------------------------------------------------------|----|

| Figure 15 – | OTA (a) and its small-signal representation (b)                                 | 52 |

| -           | the closed-loop amplifier without negative input transconductor (a) and         |    |

|             | its DM small-signal circuit (b).                                                | 53 |

| Figure 16 – | Circuit used to perform the output equivalent noise power analysis of           |    |

|             | the closed-loop amplifier with negative input transconductor (a) and its        |    |

|             | DM small-signal circuit (b)                                                     | 55 |

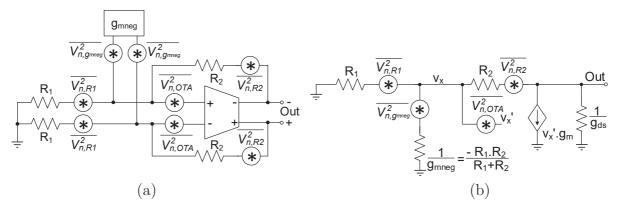

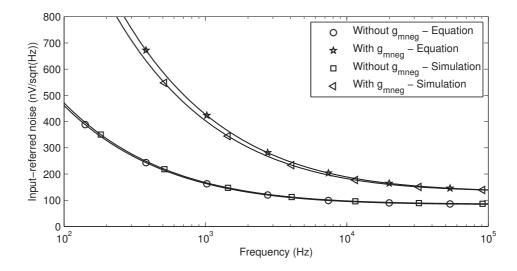

| Figure 17 – | Frequency domain analysis of the closed-loop amplifier input-referred           |    |

|             | noise with and without the negative input transconductor obtained by            |    |

|             | using the small-signal equations 3.15 and 3.22 and simulation                   | 57 |

| Figure 18 – | Classical cross-coupled negative transconductor                                 | 57 |

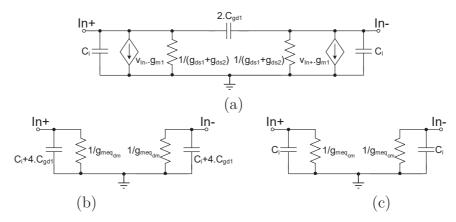

| Figure 19 – | The negative transconductor small-signal model representation: (a)              |    |

|             | complete circuit, (b) differential-mode and (c) common-mode simplified          |    |

|             | versions                                                                        | 58 |

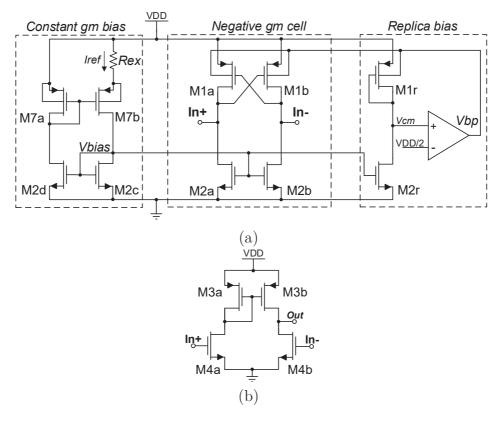

| Figure 20 – | Proposed robust negative transconductor: (a) main circuit and (b) error         |    |

|             | $amplifier\ implementation. \ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .$                  | 59 |

| Figure 21 – | Simulation results of the negative transconductance (a), and the DC CM          |    |

|             | voltage (b), versus the reference current with and without the replica bias.    | 61 |

| Figure 22 – | Schematic of the proposed OTA - simplified version                              | 62 |

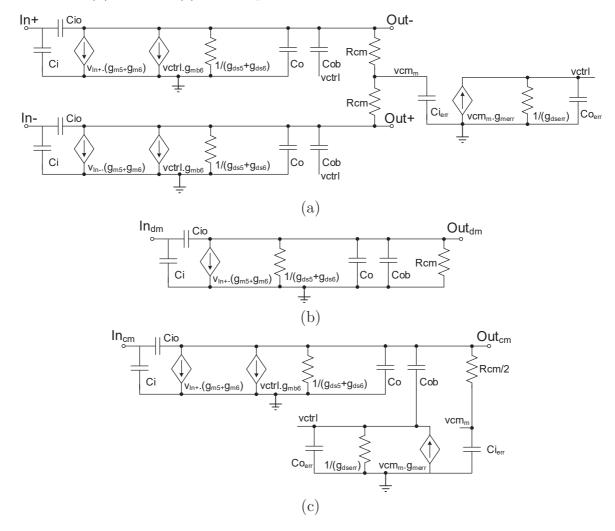

| Figure 23 – | Small-signal circuit of the proposed OTA from Fig. 22: (a) complete             |    |

|             | circuit, (b) DM and (c) CM simplified circuits                                  | 63 |

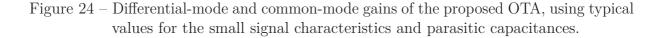

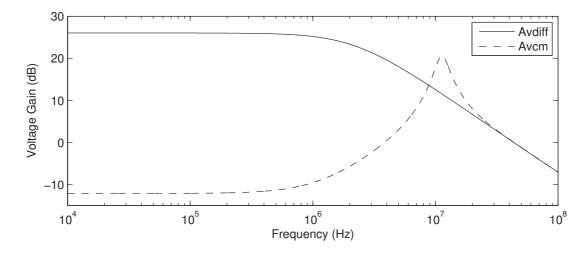

| Figure 24 – | Differential-mode and common-mode gains of the proposed OTA, using              |    |

|             | typical values for the small signal characteristics and parasitic capacitances. | 65 |

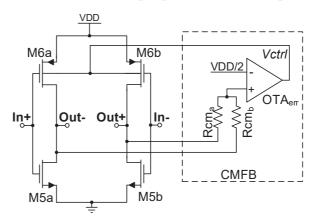

| Figure 25 – | Schematic of the proposed OTA - improved version, with the $V_{ctrl}$ voltage   |    |

|             | connected to both NMOS and PMOS bulk terminals                                  | 67 |

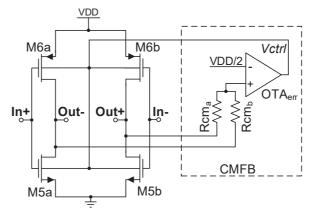

| Figure 26 – | Comparison of the common-mode gain reduction by increasing the error            |    |

|             | amplifier gain or the bulk transconductance                                     | 67 |

| Figure 27 – | Schematic of the proposed OTA using parallel common-mode current                |    |

|             | sources                                                                         | 68 |

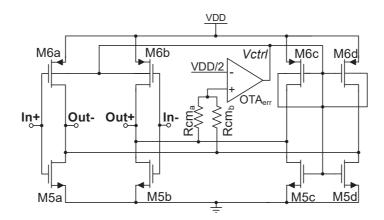

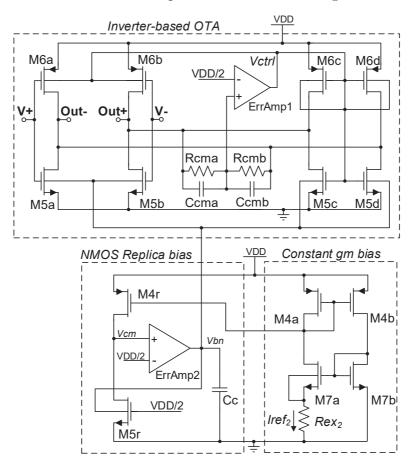

| -           | Inverter-based OTA implementation considering the NMOS bulk bias                | 70 |

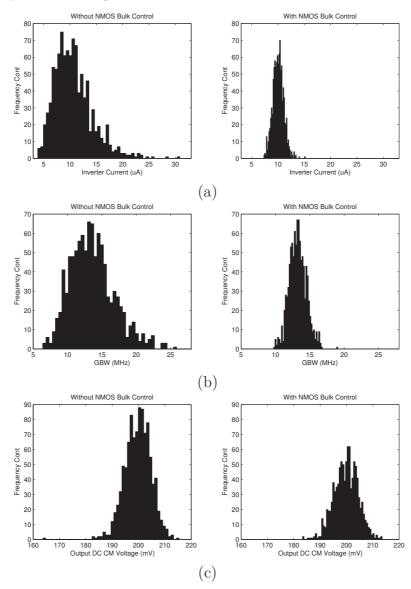

| Figure 29 – | Histogram of some OTA specifications without and with considering               |    |

|             | the NMOS bulk control: (a) CMOS inverter current, (b) GBW and (c)               |    |

| -           | common-mode output DC voltage                                                   | 71 |

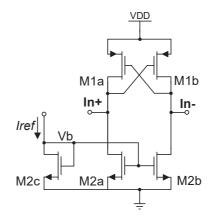

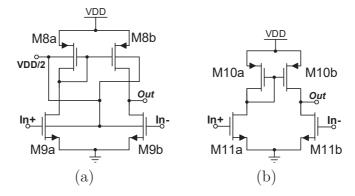

|             | The CMFB error amplifiers: (a) ErrAmp1 and (b) ErrAmp2                          | 72 |

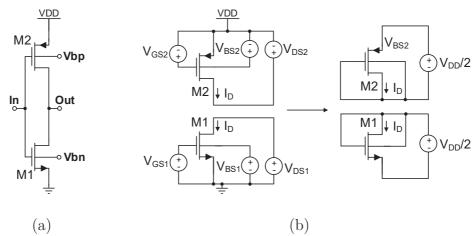

| Figure 31 – | Inverter-based circuit design: (a) schematic of the basic cell and (b) the      |    |

|             | individual bias representation.                                                 | 75 |

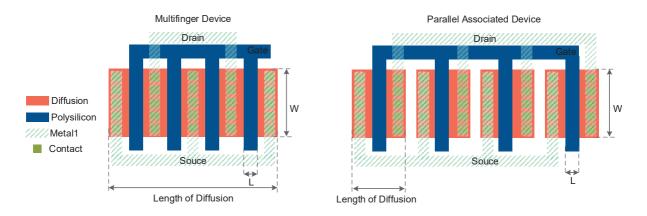

| Figure 32 – | Multifinger and parallel associated devices layouts                             | 77 |

|             |                                                                                 |    |

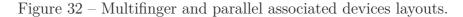

| Figure 33 - | - Flowchart of the operation-point simulation-based W calculation algo-                                                                                                   |     |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|             | rithm using a drain current reference $(I_{D_{ref}})$                                                                                                                     | 30  |

| Figure 34 - | - Operation-point simulated-based sizing tool in a graphical user interface                                                                                               |     |

|             | (GUI)                                                                                                                                                                     | 31  |

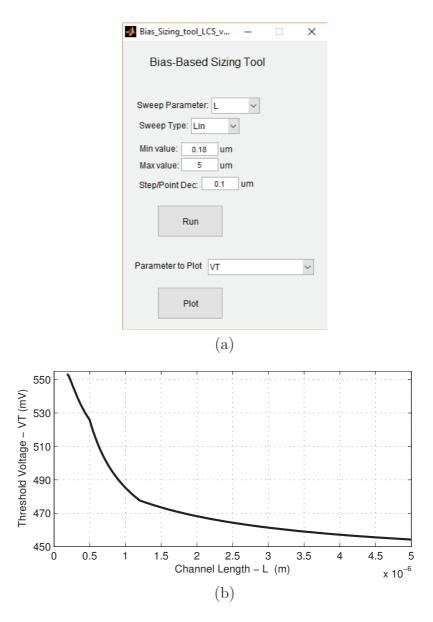

| Figure 35 - | - Parameter sweep environmental in the implemented tool (a), and a                                                                                                        |     |

|             | sample of sweep variation curve obtained for the threshold voltage in                                                                                                     |     |

|             | function of the channel length variation (b)                                                                                                                              | 32  |

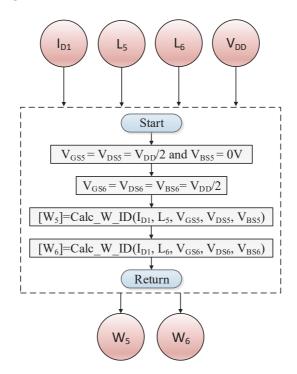

| Figure 36 - | - Flowchart of the design methodology used in the transistor sizing of the                                                                                                |     |

|             | OTA shown in Fig. 27                                                                                                                                                      | 34  |

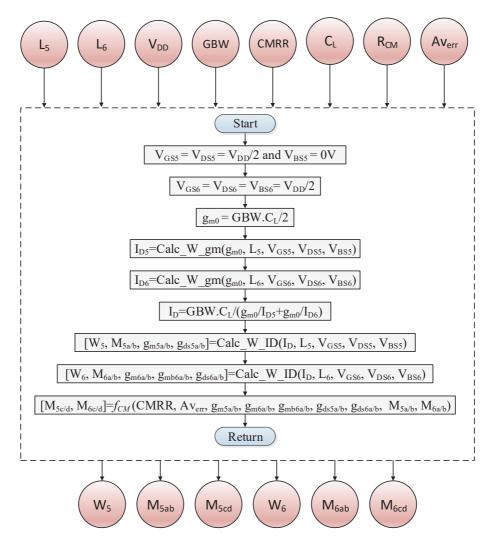

| Figure 37 - | - Flowchart of the design methodology used in the transistor sizing of the                                                                                                |     |

|             | OTA shown in Fig. 27 - improved version                                                                                                                                   | 35  |

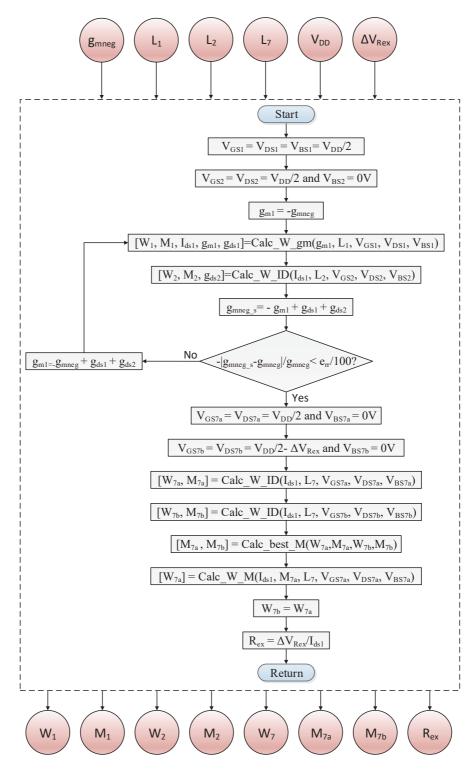

| Figure 38 - | - Flowchart of the design methodology used for the transistor sizing of                                                                                                   |     |

|             | the negative transconductor shown in Fig. 20                                                                                                                              | 86  |

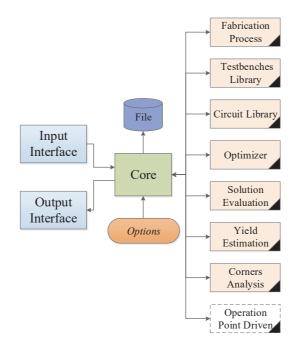

| Figure 39 - | - UCAF modular functions. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                         | 88  |

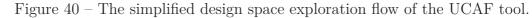

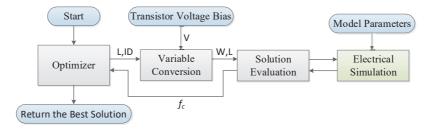

| Figure 40 - | - The simplified design space exploration flow of the UCAF tool. $\ldots$ .                                                                                               | 39  |

| Figure 41 - | - Design variable comparison in a single-ended CMOS inverter amplifier:                                                                                                   |     |

|             | (a) conventional tool and (b) proposed operation-point driven tool 9                                                                                                      | 90  |

| Figure 42 - | - The improved UCAF flow using the proposed operation-point driven                                                                                                        |     |

|             | strategy.                                                                                                                                                                 | 91  |

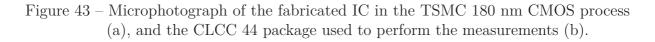

| Figure 43 - | - Microphotograph of the fabricated IC in the TSMC 180 nm CMOS                                                                                                            |     |

|             | process (a), and the CLCC 44 package used to perform the measurements                                                                                                     |     |

|             | (b)                                                                                                                                                                       | )3  |

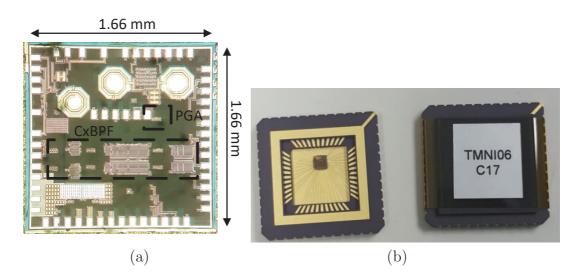

| Figure 44 - | – The top-level layout of the designed IC in the GF 8HP BiCMOS 130 $\rm nm$                                                                                               |     |

|             | process                                                                                                                                                                   | 94  |

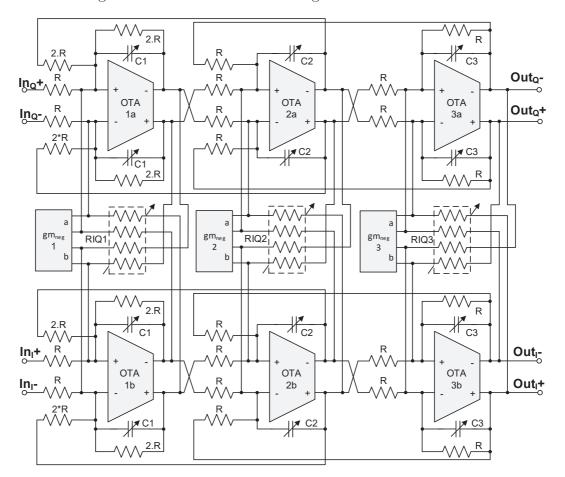

| Figure 45 - | - Schematic of the designed third-order CxBPF                                                                                                                             | 96  |

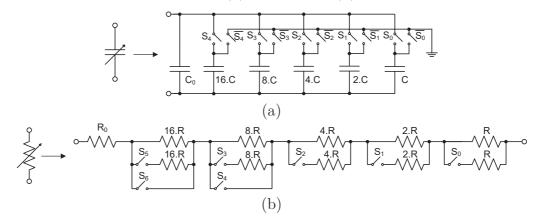

| Figure 46 - | - Programmable capacitor (a) and resistor (b) used to implement the                                                                                                       |     |

|             | CxBPF                                                                                                                                                                     | 97  |

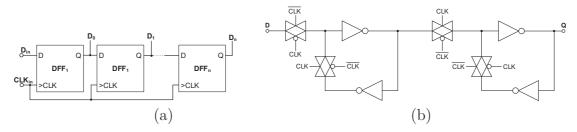

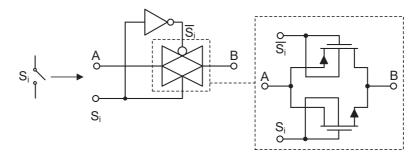

| Figure 47 - | - Shift register used as serial input register bank (a) and the schematic of                                                                                              |     |

|             | the edge-triggered D flip-flop (b) used in the implementation. $\ldots$ .                                                                                                 | 98  |

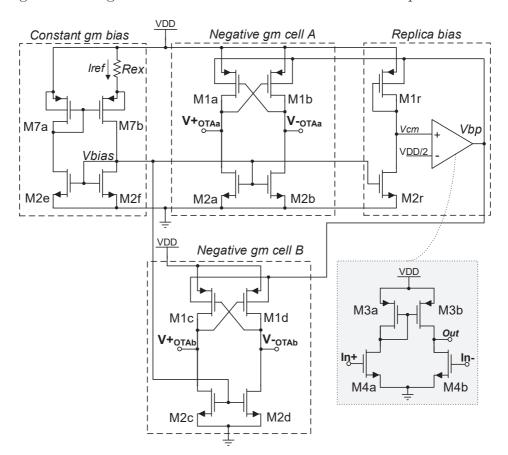

| Figure 48 - | - Negative transcondutor used in the CxBPF implementation 10 $$                                                                                                           | )() |

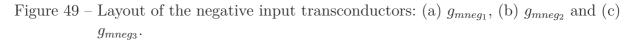

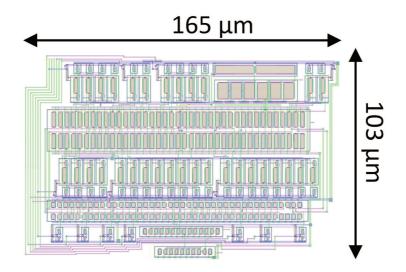

| Figure 49 - | - Layout of the negative input transconductors: (a) $g_{mneg_1}$ , (b) $g_{mneg_2}$ and                                                                                   |     |

|             | (c) $g_{mneg_3}$                                                                                                                                                          | )1  |

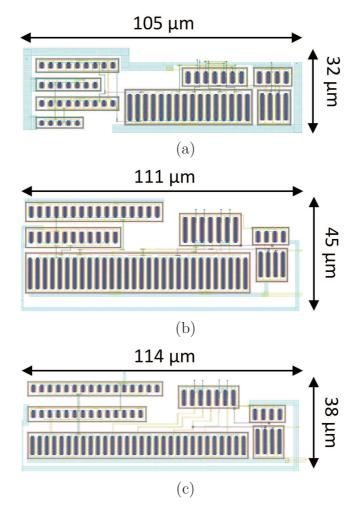

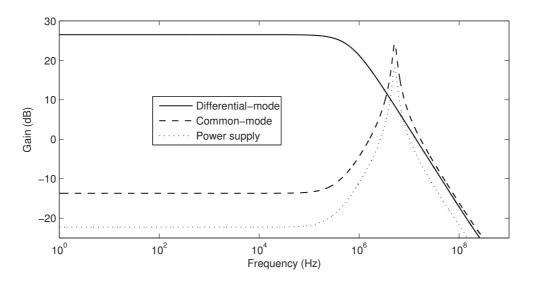

| Figure 50 - | - Layout of the OTA used in the CxBPF implementation                                                                                                                      | )2  |

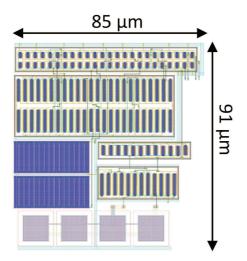

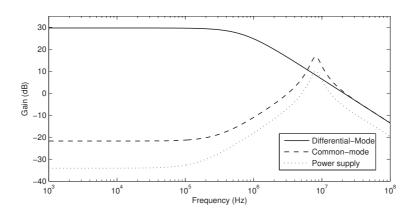

| Figure 51 - | - OTA differential-mode, common-mode and power supply gains as func-                                                                                                      |     |

|             | tion of the frequency                                                                                                                                                     | )3  |

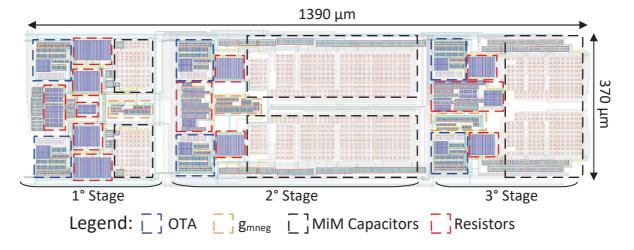

| Figure 52 – | - Layout of the CxBPF circuit                                                                                                                                             | )4  |

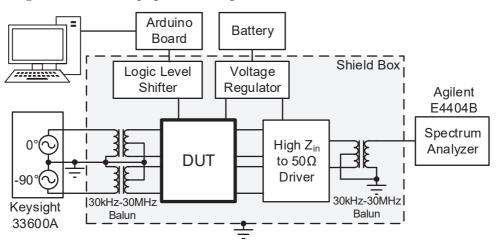

| Figure 53 – | - The equipment setup used in the CxBPF measurements. $\dots \dots \dots$ | )5  |

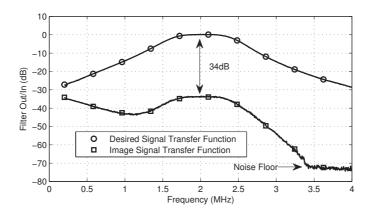

| Figure 54 - | - Measured complex BPF transfer function for the desired and image                                                                                                        |     |

|             | signals. $\ldots \ldots \ldots$                           | )5  |

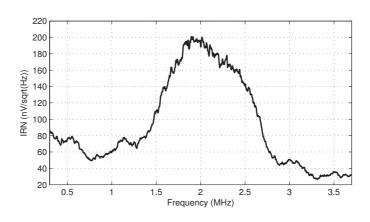

| Figure 55 | – Measured equivalent output noise density                                      | 106 |

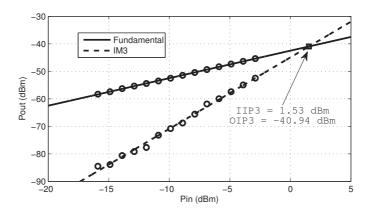

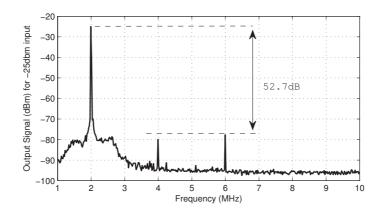

|-----------|---------------------------------------------------------------------------------|-----|

| Figure 56 | – Measured third-order interception point (IIP3).                               | 106 |

| Figure 57 | – Measured spurious-free dynamic range (SFDR)                                   | 106 |

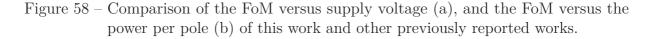

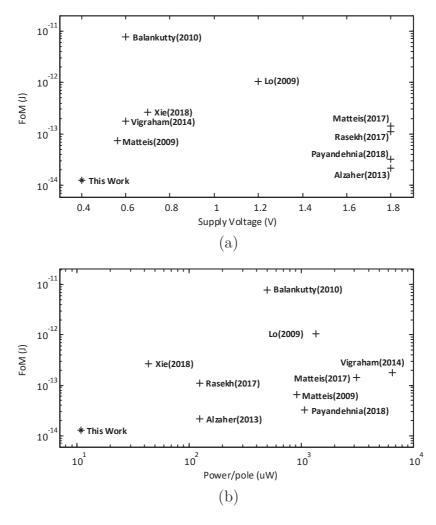

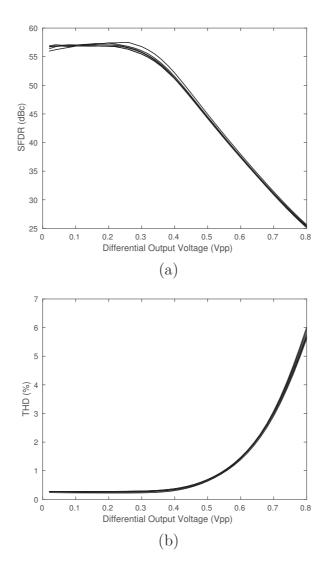

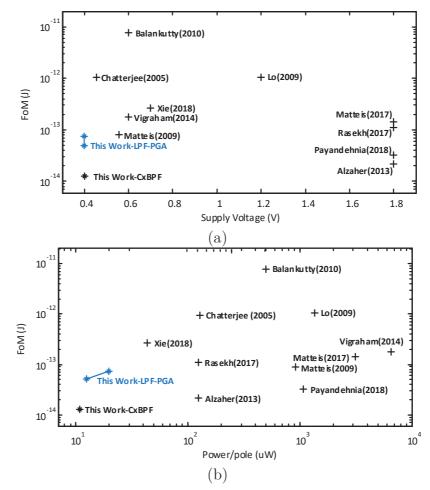

| Figure 58 | – Comparison of the FoM versus supply voltage (a), and the FoM versus           |     |

|           | the power per pole (b) of this work and other previously reported works.        | 108 |

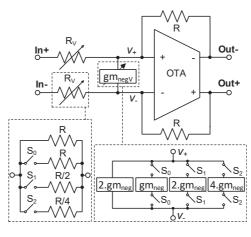

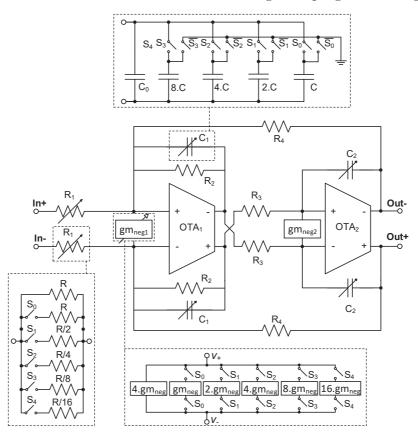

| Figure 59 | – Proposed PGA using a programmable input negative transconductance.            | 109 |

| Figure 60 | – Proposed programmable negative input transconductor                           | 110 |

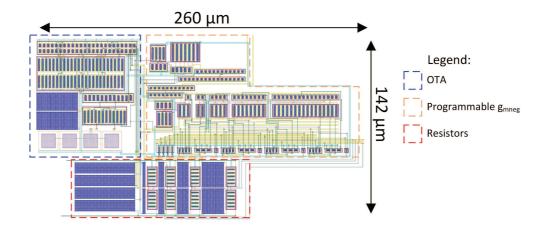

| Figure 61 | – Layout of the PGA circuit.                                                    | 112 |

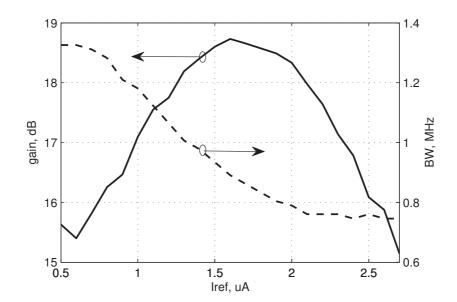

| Figure 62 | – The PGA gain and bandwidth variation in function of the ${\cal I}_{ref}$ bias | 112 |

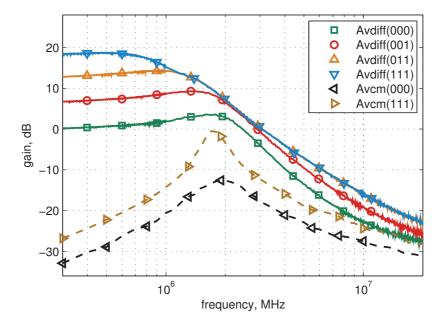

| Figure 63 | – Measured frequency domain transfer functions for the PGA differential-        |     |

|           | mode $(Av_{diff})$ and common-mode $(Av_{cm})$ gains                            | 113 |

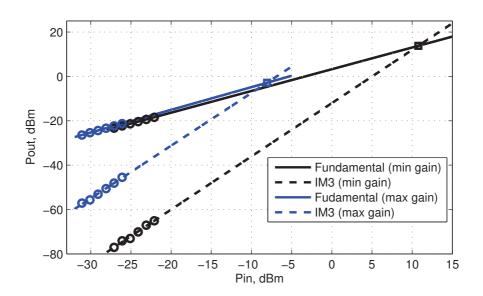

| Figure 64 | – Measured input third-order inter-modulation intercept point (IIP3)            | 114 |

| Figure 65 | – Tow-Thomas second-order filter with integrated programmable gain              |     |

|           | capability.                                                                     | 116 |

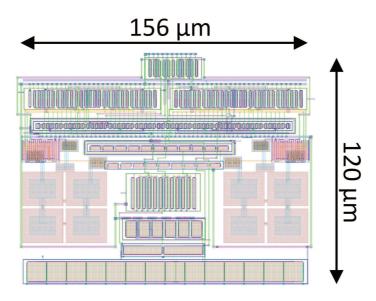

| Figure 66 | – The used gate connected to bulk transmission gate switch                      | 118 |

| Figure 67 | - Layout of the programmable and constant value negative transconductor.        | 119 |

| Figure 68 | - Layout of the OTA1 and OTA2 amplifier used in the filter implementation.      | 120 |

| Figure 69 | – Post-layout simulation results of the differential-mode, the common-          |     |

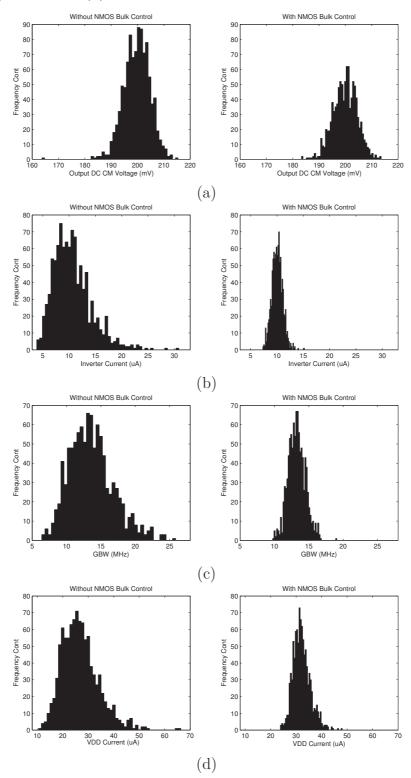

|           | mode and the power supply gains for the proposed OTA                            | 121 |

| Figure 70 | – Post-layout simulation pulse response for the proposed OTA                    | 122 |

| Figure 71 | – Histogram for some OTA specifications without and with the NMOS               |     |

|           | bulk control: (a) Output DC common-mode Voltage, (b) CMOS inverter              |     |

|           | current, (c) GBW and (d) $V_{DD}$ current                                       | 123 |

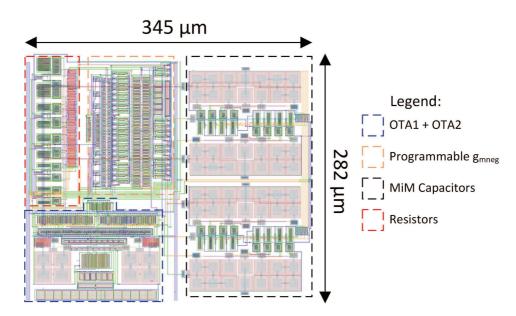

| Figure 72 | – Complete layout of the Tow-Thomas LPF with integrated programmable            |     |

|           | gain                                                                            | 124 |

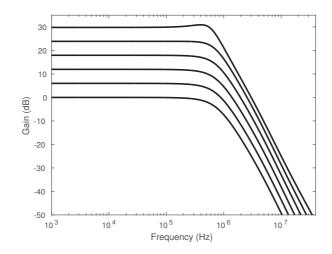

| Figure 73 | – Post-layout simulated transfer function of the programmable-gain LPF.         |     |

|           | The thermometric-coded control bits were changed to set the desired             |     |

|           | voltage gain from 0 dB to 30 dB with 6 dB step                                  | 125 |

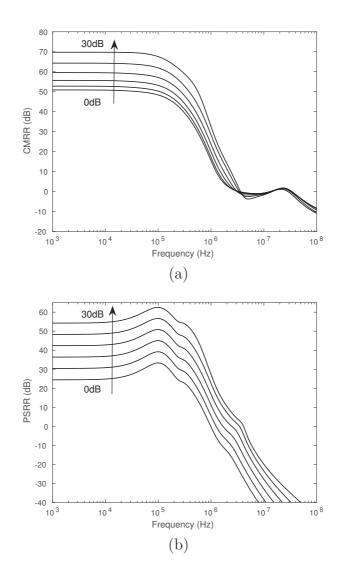

| Figure 74 | – Post-layout simulated common-mode and power supply rejection rates            |     |

|           | of the programmable gain LPF as a function of frequency and the gain            |     |

|           | modes from 0 dB to 30 dB with 6 dB step: (a) CMRR and (b) PSRR                  | 126 |

| Figure 75 | – Input-referred noise (IRN) voltage of the programmable-gain LPF as a          |     |

|           | function of the frequency for all the voltage gain modes                        | 127 |

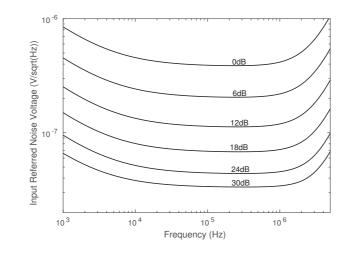

| Figure 76 | – The programmable gain LPF dynamic range analysis as a function of             |     |

|           | the differential output voltage in all the gain modes: (a) spurious-free        |     |

|           | dynamic range (SFDR) and (b) total harmonic distortion (THD)                    | 128 |

| Figure 77 | - Comparison of the FoM of this work and other previously reported work:        |     |

|           | (a) FoM versus supply voltage and (b) FoM versus the power per pole.            | 129 |

|           |                                                                                 |     |

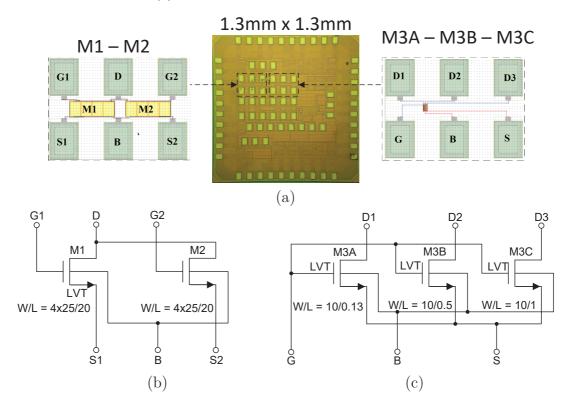

| Figure 78 – | NMOS test transistors used to analyze the device characteristics: (a)      |     |

|-------------|----------------------------------------------------------------------------|-----|

|             | microphotograph of the fabricated IC, (b) schematic of the test transistor |     |

|             | M1 and M2 and (c) the schematic of the test transistors M3A, M3B           |     |

|             | and M3C                                                                    | 144 |

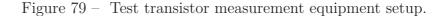

| Figure 79 – | Test transistor measurement equipment setup                                | 144 |

| Figure 80 – | The connection of the B1500A equipment using the SMUs as voltage           |     |

|             | sources and performing the current measurements                            | 145 |

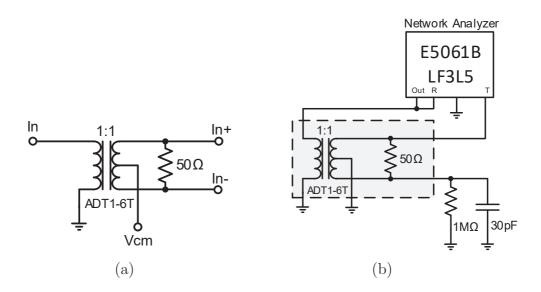

| Figure 81 – | Input Balun transformer used to the single-ended to differential conver-   |     |

|             | sion (a) and its AC characterization using a network analyzer (b)          | 148 |

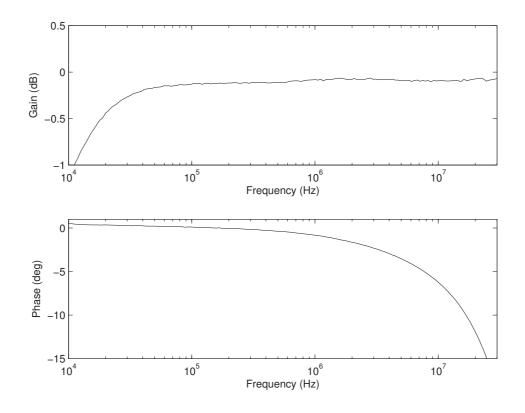

| Figure 82 – | The balun differential-mode Bode diagram                                   | 148 |

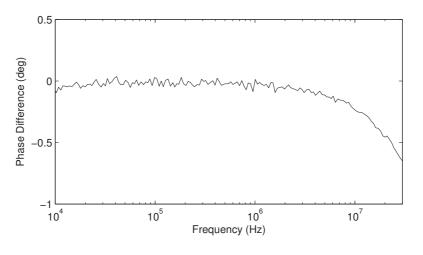

| Figure 83 – | The balun phase difference                                                 | 149 |

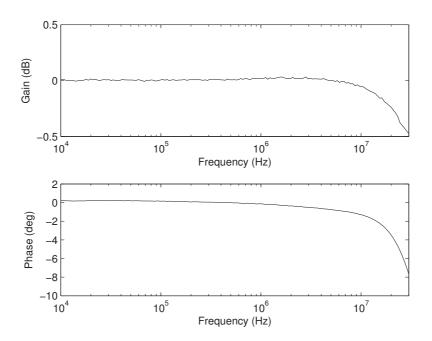

| Figure 84 – | The balun common-mode Bode diagram                                         | 149 |

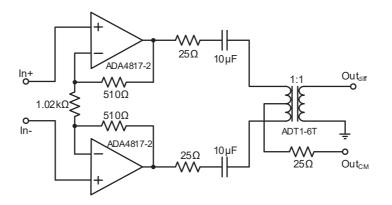

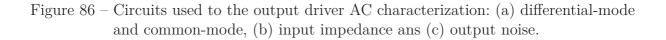

| Figure 85 – | The proposed external output driver circuit.                               | 151 |

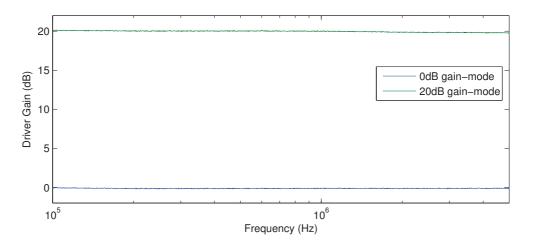

| Figure 86 – | Circuits used to the output driver AC characterization: (a) differential-  |     |

|             | mode and common-mode, (b) input impedance ans (c) output noise             | 152 |

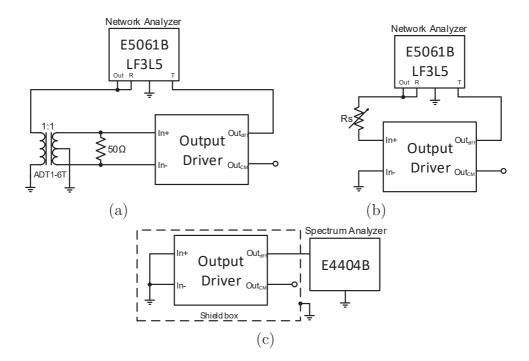

| Figure 87 – | Driver differential-mode gain.                                             | 152 |

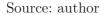

| Figure 88 – | Battery powered voltage regulator used to obtain the supply and refer-     |     |

|             | ence voltages.                                                             | 154 |

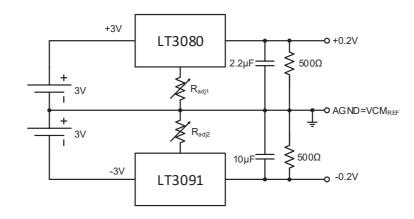

| Figure 89 – | Photography of the generic printed circuit board (PCB) designed            | 154 |

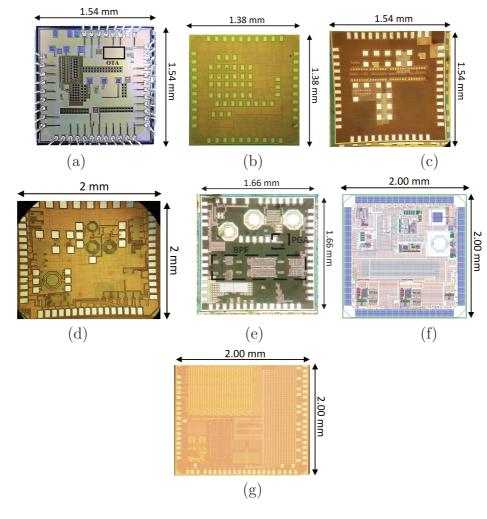

| Figure 90 – | Integrated circuits designed and fabricated during the Ph.D. program:      |     |

|             | (a) TSMC 180 nm CMOS - 2015, (b) TSMC 130 nm CMOS - 2015, (c)              |     |

|             | TSMC 180 nm CMOS - 2016, (d) Global Foundries 130 nm RF CMOS               |     |

|             | - 2016, (e) TSMC 180 nm CMOS- 2017, (f) Global Foundries 130 nm            |     |

|             | HP BiCMOS - 2018 and (g) TSMC 65 nm CMOS - 2018                            | 158 |

|             |                                                                            |     |

## List of Tables

| Table 1 –  | The state-of-the-art Bluetooth LE RF receivers (RX) and transmitters (Tx)                                                                              |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2 –  | Empirical channel inversion level classification for a NMOS transistor . 31                                                                            |

| Table 3 –  | Simulation results of the DM equivalent negative transconductance $g_{mneg}$                                                                           |

|            | and $V_{DC}$ input voltage, for some process and temperature corners at                                                                                |

|            | $V_{DD} = 0.4 \text{ V}. \qquad \dots \qquad $ |

|            | Values of the passive devices used in the CxBPF implementation 98                                                                                      |

| Table 5 –  | Values of the parameters used in the CxBPF negative transconductors                                                                                    |

|            | implementation                                                                                                                                         |

| Table 6 -  | Parameter values of all the transistor and passive devices used in the                                                                                 |

|            | CxBPF OTA implementation                                                                                                                               |

|            | OTA post-layout simulation results                                                                                                                     |

| Table 8 –  | CxBPF measured specifications and comparison with other Bluetooth                                                                                      |

|            | filters                                                                                                                                                |

| Table 9 –  | Parameters values used in the PGA negative transconductors implemen-                                                                                   |

|            | tation                                                                                                                                                 |

|            | Measured results and comparison with other works from the literature. 115                                                                              |

| Table 11 – | Parameters used to implement the Tow-Thomas LPF with integrated                                                                                        |

|            | programmable-gain capability                                                                                                                           |

| Table 12 – | Device parameters used to implement a 10 $\mu S$ negative transconductor . 119                                                                         |

| Table 13 – | Device parameters used in the OTA implementation                                                                                                       |

| Table 14 – | Post-layout simulation results of the 0.4 V OTA 121                                                                                                    |

| Table 15 – | Comparison of the process variability in some specifications of the de-                                                                                |

|            | signed OTA with and without using the proposed NMOS bulk control.                                                                                      |

|            | The results were based on the Monte Carlo process and mismatch simu-                                                                                   |

|            | lation with 1000 samples $\ldots \ldots 124$                |

| Table 16 – | LPF post-layout simulation results                                                                                                                     |

| Table 17 – | Comparison with some active-RC LPFs from the literature $\ldots$                                                                                       |

| Table 18 – | The specifications of some commercial differential active probes 151                                                                                   |

|            |                                                                                                                                                        |

# List of abbreviations and acronyms

| AC     | Alternated Current                                  |

|--------|-----------------------------------------------------|

| BiCMOS | Bipolar and Complementary Metal-Oxide-Semiconductor |

| BLE    | Bluetooth Low Energy                                |

| BPF    | Band-Pass Filter                                    |

| CAD    | Computer-Aided Design                               |

| CM     | Common-Mode                                         |

| CMFB   | Common-Mode Feedback                                |

| CMOS   | Complementary Metal-Oxide-Semiconductor             |

| CMRR   | Common-Mode Rejection Ratio                         |

| CxBPF  | Complex Band-Pass Filter                            |

| DC     | Direct Current                                      |

| DDA    | Differential Difference Amplifier                   |

| DFF    | D-Type Flip-Flop                                    |

| DIBL   | Drain-Induced Barrier Lowering                      |

| DL     | Diffusion Region Length                             |

| DM     | Differential-Mode                                   |

| DR     | Dynamic Range                                       |

| FD     | Fully-Differential                                  |

| FF     | N-Fast and P-Fast Process Corner Parameters Set     |

| FoM    | Figure of Merit                                     |

| FS     | N-Fast and P-Slow Process Corner Parameters Set     |

| GBW    | Gain-Bandwidth Product                              |

| GUI    | Graphical User Interface                            |

| cy |

|----|

|    |

- IIP<sub>3</sub> Input Third-Order Intermodulation Intercept-Point

- IM<sub>3</sub> Third-Order Intermodulation Product

- IRN Input-Referred Noise

- IRR Image Rejection Ratio

- LNA Low Noise Amplifier

- LOD Length of Diffusion Effect

- LPF Low-Pass Filter

- MI Moderated Inversion

- MiM Metal-insulator-Metal

- MOS Metal-Oxide-Semiconductor

- NF Noise Figure

- NIC Negative Input Converter

- NMOS Metal-Oxide-Semiconductor type N

- OPAMP Operational Amplifier

- OPD Operation-Point Driven

- OTA Operational Transconductance Amplifier

- PDK Process Design Kit

- PGA Programmable Gain Amplifier

- PMOS Metal-Oxide-Semiconductor type P

- PSRR Power Supply Rejection Ratio

- PVT Process Voltage and Temperature

- RF Radio Frequency

- RSCE Reverse Short-Channel Effect

- SI Strong Inversion

- SF N-Slow and P-Fast Process Corner Parameters Set

- SFDR Spurious-Free Dynamic Range

- SS N-Slow and P-Slow Process Corner Parameters Set

- STI Shallow Trench Isolation

- THD Total Harmonic Distortion

- TIA Transimpedance Amplifier

- ULP Ultra-Low Power

- ULV Ultra-Low Voltage

- WI Weak Inversion

- WPE Well Proximity Effect

# List of symbols

| $Av_{cl}$    | Closed-Loop Voltage Gain                     |

|--------------|----------------------------------------------|

| $Av_{cl_0}$  | Low Frequency Closed-Loop Voltage Gain       |

| $Av_{dm}$    | Differential-Mode Voltage Gain               |

| $Av_{dm_0}$  | Low Frequency Differential-Mode Voltage Gain |

| $Av_{cm}$    | Common-Mode Voltage Gain                     |

| $Av_{cm_0}$  | Low Frequency Common-Mode Voltage Gain       |

| $Av_{vdd}$   | Positive Power Supply Voltage Gain           |

| $Av_{vss}$   | Negative Power Supply Voltage Gain           |

| $C_{bs}$     | Bulk to Source Capacitance                   |

| $C_{db}$     | Drain do Bulk Capacitance                    |

| $C_{gb}$     | Gate to Bulk Capacitance                     |

| $C_{gd}$     | Gate to Drain Capacitance                    |

| $C_{gs}$     | Gate to Source Capacitance                   |

| $C_i$        | Input Capacitance                            |

| $C_{io}$     | Input to Output Capacitance                  |

| $C_L$        | Load Capacitance                             |

| $C_o$        | Output Capacitance                           |

| $C_{ob}$     | Output to Bulk Capacitance                   |

| $C_{ox}$     | Gate Oxide Capacitance                       |

| $\Delta V_T$ | Threshold Voltage Variation                  |

| $\Delta g_m$ | Transconductance Safety Margin               |

| $e_{rr}$     | Percent Error                                |

| $f_c$        | Solution Evaluation Cost Function            |

| $f_{cutoff}$ | Cutoff Frequency                                                            |

|--------------|-----------------------------------------------------------------------------|

| $\phi_T$     | Thermal Voltage                                                             |

| $\phi_F$     | Fermi Level                                                                 |

| $\gamma$     | Body Effect Parameter                                                       |

| $\gamma_n$   | MOSFET Thermal Noise Factor                                                 |

| $g_m$        | Transconductance                                                            |

| $g_{mb}$     | Bulk Transconductance                                                       |

| $g_{mneg}$   | Equivalent Negative Transconductance                                        |

| $g_m/I_D$    | Transistor Efficiency Parameter                                             |

| $g_{ds}$     | Output Conductance                                                          |

| $I_0$        | Technology Current                                                          |

| $I_B$        | Bulk Current                                                                |

| $I_{BS}$     | Bulk to Source Current                                                      |

| $I_C$        | Channel Inversion Coefficient                                               |

| $I_D$        | Drain Current                                                               |

| $I_D/(W/L)$  | Drain Current Density                                                       |

| $I_G$        | Gate Leakage Current                                                        |

| $I_{ref}$    | Reference Current                                                           |

| $I_S$        | Source Current                                                              |

| k            | Boltzmann Constant (approximately equal to $1.38\times 10^{-23} {\rm J/K})$ |

| L            | Transistor Channel Length                                                   |

| Λ            | Channel Length Modulation Parameter                                         |

| M            | Device Multiplicity                                                         |

| $\mu_0$      | Low Electric Field Channel Charge Carrier Mobility Parameter                |

| n            | Sub-threshold Slope Factor                                                  |

| $n_0$        | Bulk Factor Parameter                                                       |

| $\omega_{GBW}$      | Angular Gain-Bandwidth Product Frequency |

|---------------------|------------------------------------------|

| $\omega_p$          | Pole Angular frequency                   |

| $\omega_z$          | Zero Angular frequency                   |

| $p_i$               | Process Model Parameters                 |

| $Q_{filter}$        | Filter Quality Factor                    |

| S                   | Laplace frequency $(s \approx j.\omega)$ |

| $\overline{V_n^2}$  | Noise Power Source                       |

| $V_B$               | Bias Voltage                             |

| $V_{BS}$            | Bulk to Source Voltage                   |

| $V_{CM}$            | Common-Mode Voltage                      |

| $V_{CM_{DC}}$       | DC Common-Mode Voltage                   |

| $V_{CM_{in_{min}}}$ | Minimum Input Common-Mode Voltage        |

| $V_{DD}$            | Power Supply Voltage                     |

| $V_{DD_{min}}$      | Minimum Power Supply Voltage             |

| $V_{DS}$            | Drain to Source Voltage                  |

| $V_{DS_{SAT}}$      | Saturation Voltage                       |

| $V_{GS}$            | Gate to Source Voltage                   |

| $V_{i_{CM_{DC}}}$   | Minimum Common-Mode Input Voltage        |

| $V_{OD}$            | Overdrive Voltage                        |

| $V_{O_{DC}}$        | Output DC Voltage                        |

| $V_{O_{CM}}$        | Output CM Voltage                        |

| $V_T$               | Threshold Voltage                        |

| $V_{T0}$            | Threshold Voltage at $V_{BS} = 0V$       |

| $V_{T_p}$           | PMOS Transistor Threshold Voltage        |

| T                   | Temperature in Kelvin (K)                |

| W                   | Transistor Channel Width                 |

## Contents

| 1     | INTRODUCTION                                                   | 23 |

|-------|----------------------------------------------------------------|----|

| 1.1   | Objectives                                                     | 26 |

| 1.2   | The Main Contributions of this Thesis                          | 26 |

| 1.3   | Thesis Organization                                            | 27 |

| 2     | ULV AND ULP OPERATIONAL AMPLIFIERS FOR ACTIVE-RC               |    |

|       | FILTERS                                                        | 28 |

| 2.1   | CMOS Transistors at the ULV Range                              | 28 |

| 2.1.1 | Current Density and Channel Inversion Level                    | 29 |

| 2.1.2 | Saturation Voltage                                             | 32 |

| 2.1.3 | Bulk Forward Bias                                              | 32 |

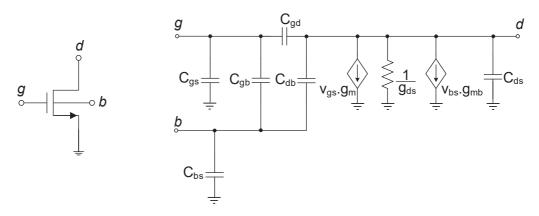

| 2.1.4 | Small-signal Transconductances and Conductances                | 36 |

| 2.1.5 | Short Channel Effects                                          | 38 |

| 2.2   | ULV Operational Amplifiers                                     | 38 |

| 2.2.1 | The Minimum Operation Voltage for Amplifiers                   | 39 |

| 2.2.2 | Low Power ULV Operational Amplifier                            | 41 |

| 2.2.3 | The Common-mode Rejection of the ULV Amplifiers                | 43 |

| 2.2.4 | Gate and Bulk Input Amplifiers                                 | 44 |

| 2.2.5 | Compensation of the PVT Variation on the ULV Amplifiers        | 45 |

| 2.3   | Chapter Conclusion                                             | 46 |

| 3     | PROPOSED ULTRA-LOW VOLTAGE CIRCUITS                            | 48 |

| 3.1   | The use of a Negative Transconductor for Single-stage OTA Com- |    |

|       | pensation                                                      | 48 |

| 3.1.1 | Closed-loop Amplifier                                          | 48 |

| 3.1.2 | Active Integrator                                              | 51 |

| 3.1.3 | Noise Analysis                                                 | 53 |

| 3.2   | The Proposed ULV PVT Robust Negative Transconductor            | 56 |

| 3.3   | The Proposed ULV Inverter-Based OTA                            | 62 |

| 3.3.1 | Improvements in the CMFB Loop                                  | 66 |

| 3.3.2 | Improving the Drain Current Control                            | 68 |

| 3.3.3 | Error Amplifier                                                | 72 |

| 3.4   | Chapter Conclusion                                             | 72 |

| 4     | DESIGN METHODOLOGY FOR ULV CIRCUITS                            | 74 |

| 4.1   | Transistor Sizing of ULV Circuits                              | 75 |

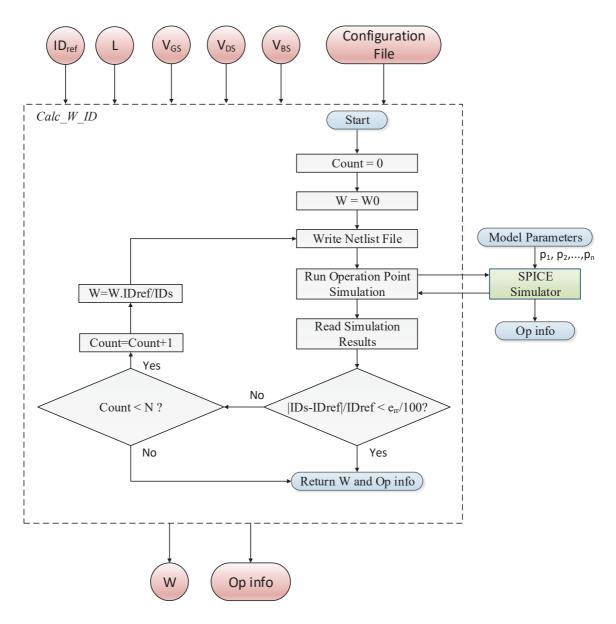

| 4.2   | Proposed Operation-Point Simulation-Based Design Tool        | 77  |

|-------|--------------------------------------------------------------|-----|

| 4.2.1 | Design Example                                               | 83  |

| 4.3   | ULV Circuit Design using the UCAF Tool                       | 87  |

| 4.4   | Chapter Conclusion                                           | 91  |

| 5     | DESIGN AND EXPERIMENTAL RESULTS                              | 93  |

| 5.1   | Complex Band-Pass Image-Rejection Filter                     | 94  |

| 5.1.1 | Filter Design                                                | 95  |

| 5.1.2 | Negative Transconductors Implementation                      | 98  |

| 5.1.3 | OTA Implementation                                           | 99  |

| 5.1.4 | CxBPF Measured Results                                       | 103 |

| 5.2   | Programmable Gain Amplifier                                  | 108 |

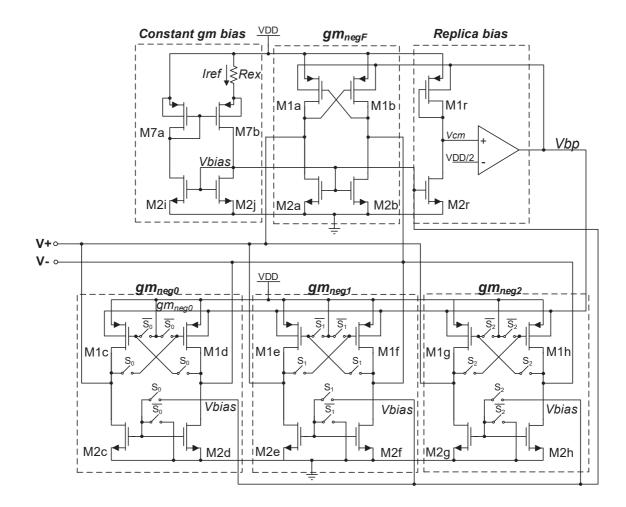

| 5.2.1 | OTA Implementation                                           | 110 |

| 5.2.2 | Programmable Negative Input Transconductor                   | 110 |

| 5.2.3 | Measured Results                                             | 112 |

| 5.3   | Second-Order Low-pass Filter with integrated Programmable Ga | nin |

|       | Amplifier                                                    | 114 |

| 5.3.1 | Filter Design                                                | 115 |

| 5.3.2 | Negative Transconductors Implementation                      | 118 |

| 5.3.3 | OTA Implementation                                           | 118 |

| 5.3.4 | Post-Layout Simulated Results of the Programmable-Gain LPF   | 122 |

| 5.4   | Chapter Conclusion                                           | 129 |

| 6     | CONCLUSIONS                                                  | 131 |

|       | BIBLIOGRAPHY                                                 | 133 |

|       | APPENDIX                                                     | 142 |

|       | APPENDIX A – CHARACTERIZATION OF THE CMOS 130N               | Μ   |

|       | TEST TRANSISTORS                                             | 143 |

| A.1   | Test Transistors                                             | 143 |

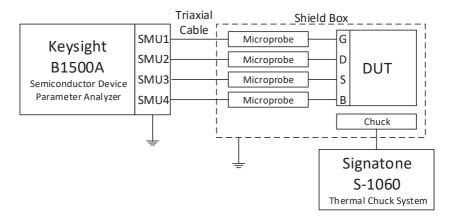

| A.2   | Measurement Setup                                            | 143 |

|       | APPENDIX B – FULLY-DIFFERENTIAL CIRCUITS MEASUR              |     |

|       | MENTS STRATEGY                                               |     |

| B.1   | Classical Measurement Equipment Characteristics              |     |

| B.2   | DUT Input Interface                                          |     |

| B.3   | DUT Output Interface                                         |     |

| B.3.1 | Power Supply and Voltage Regulators                          | 153 |

| B.4 | Generic Test Board                           | 154 |  |

|-----|----------------------------------------------|-----|--|

|     | APPENDIX C – PUBLICATIONS AND FABRICATED ICS | 155 |  |

| C.1 | Publications                                 | 155 |  |

| C.2 | Fabricated ICs                               | 157 |  |

## 1 Introduction

The Internet of Things (IoT) is one of the main subjects of the microelectronics industry and research centers nowadays. A global IoT market of \$8.9T is projected in 2020, including a vast quantity of application areas from the biomedical to the precision agriculture, according to Columbus (2017). In 2015 there were about 9 billion connected devices around the world and it is estimated ranging from 25 to 50 billion devices by 2025 (MANYIKA et al., 2015).

The massive number of wirelessly connected devices and the fast-growth expected by the IoT concept have increased the demand for short-range RF transceivers. In some applications, such as the body implantable devices and the remote wireless sensor networks (WSN), there is a significant trade-off between the needed long lifetime and the reduced energy density availability. This is supported by the challenging, sometimes impracticable, device replacement and the low energy density provided by small batteries or energy harvesting capability (DEMIR; AL-TURJMAN; MUHTAROGLU, 2018). As the RF transceiver is one of the most power hungry circuit, consuming about 90% of the total energy of an IoT device (LIU et al., 2015), the key solution to address the trade-off is the development of low energy RF transceivers.

Several solutions have been proposed in the literature to make the design of low energy transceivers possible. The first of all strategies is the communication standard improvements to relax the hardware specification in favor of the low power dissipation, for example, the Bluetooth Low Energy (BLE) and the ANT+ standards (CHANG, 2014). The BLE is currently the most popular standard of the IoT devices and, in its version 5, it has the capability of using low data rate coded schemes to improve by four times the communication range of the previous version, without increasing the power dissipation of the 2.4 GHz ISM radios (Bluetooth-SIG, 2016).

The physical level simplification of the BLE standard made possible and practical several new RF transceiver architectures. Table 1 shows the state-of-the-art BLE transmitters and receivers. The classical RX and TX topologies operating around 1 V of power supply voltage tends to present increased power dissipations even with the standard relaxed specification set (WONG et al., 2013; LIU et al., 2013; PRUMMEL et al., 2015; SANO et al., 2015; WANG et al., 2016). A smaller power dissipation, at the transmitter part, is obtained by using all-digital circuits (KUO et al., 2017; LIU et al., 2015) or operating at the ultra-low voltage range (ULV) (YIN et al., 2018). On the other hand, at the receiver (RX) part, the smaller power dissipation is obtained using modern Low-IF and Zero-IF architectures, operating with low voltage supply (ZHANG; MIYAHARA; OTIS, 2013; YI

| Reference           | Process | Voltage         | Power [mW] |      | Architecture               |             |

|---------------------|---------|-----------------|------------|------|----------------------------|-------------|

|                     | [nm]    | [V]             | RX         | ΤX   | RX                         | ТΧ          |

| Masuch $(2013)$     | 130     | 1.0             | 1.0        | 5.9  | $\operatorname{Zero-IF^1}$ | QVCO+EPA    |

| Wong $(2013)$       | 130     | 1               | 4.8        | 4.6  | Sliding-IF                 | VCO+APA     |

| Liu (2013)          | 90      | 1.2             | 3.3        | 5.4  | Sliding-IF                 | PLL+DPA     |

| Zhang $(2013)$      | 65      | 0.3             | 1.3        | -    | Low-IF                     | -           |

| Bryant $(2014)$     | 65      | 0.85            | 0.55       | -    | $\operatorname{Zero-IF^1}$ | -           |

| Selvakumar $(2015)$ | 130     | 0.8             | 0.6        | -    | Low-IF                     | -           |

| Prummel $(2015)$    | 55      | 0.9-3.3         | 11.2       | 10.1 | Low-IF                     | PLL+DPA     |

| Sano $(2015)$       | 40      | 1.1             | 6.3        | 7.7  | Sliding-IF                 | PLL+DPA     |

| Liu (2015)          | 40      | 1.0             | 3.3        | 4.2  | Sliding-IF                 | All-digital |

| Wang $(2016)$       | 40      | 0.92 - 1.1      | 5.3        | 10   | Sliding-IF                 | All-digital |

| Kuo (2017)          | 28      | 1.0             | 2.75       | 3.7  | High-IF DT                 | All-digital |

| Ding $(2018)$       | 40      | 0.8             | 2.3 - 2.9  | 6.1  | Zero-IF                    | All-digital |

| Kuo (2018)          | 28      | 0.55 - 1.1      | 1 - 2.4    | -    | Low-IF DT                  | -           |

| Yi (2018)           | 28      | $0.18 - 0.30^2$ | 0.38-1.31  | -    | $Low-IF^3$                 | -           |

| Yin (2018)          | 28      | $0.2^{2}$       | -          | 4    | -                          | VCO+EPA     |

Table 1 – The state-of-the-art Bluetooth LE RF receivers (RX) and transmitters (Tx)

<sup>1</sup>LNA-less front-end, <sup>2</sup>DC-DC converter input voltage, and <sup>3</sup>without baseband filters and amplifiers.

et al., 2018; BRYANT; SJOLAND, 2014; SELVAKUMAR; LISCIDINI, 2015; DING et al., 2018; KUO et al., 2018), or by reducing the number of RF active blocks (MASUCH; DELGADO-RESTITUTO, 2013a; BRYANT; SJOLAND, 2014). The digital-intensive circuits transceivers should be implemented in advanced CMOS process ( $\leq 40$  nm) in order to obtain faster switches and lower parasitic capacitances (KUO et al., 2018). Otherwise, the strategies based on cutting some active-RF hardware and reducing the operation voltage can also be implemented in low-cost sub-micron CMOS processes. Additionally, the low voltage operation offers the opportunity to increase the IoT device lifetime, by using high-efficiency only step-down or low conversion factor buck-boost DC-DC converters, on the battery (LIU et al., 2017) and energy harvesting (ABDELFATTAH et al., 2018) powered circuits, respectively. The ULV operation in the range of 0.2 V to 0.5 V is also very useful for digital circuits, in which an optimal supply voltage level can be adopted to reduce the dynamic power dissipation to the level of the leakage power dissipation to reach the Minimal Energy Point (MEP) operation (REYNDERS; DEHAENE, 2015; ALIOTO, 2012).

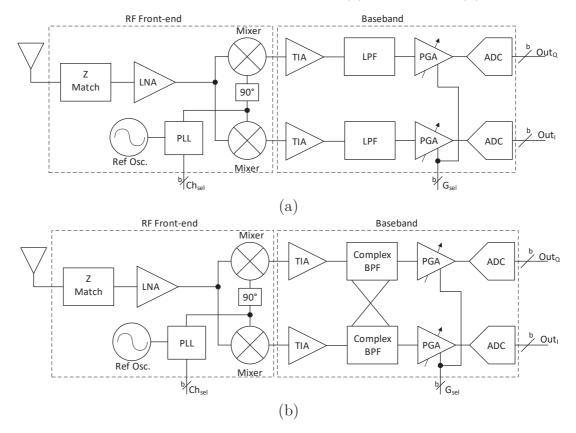

Based on the previous analysis, this work aims to design low energy building blocks for BLE RF receivers by using the low voltage operation and new design strategies to obtain the low power dissipation in low-cost sub-micron CMOS process. Fig. 1 shows the typical block diagram of continuous-time quadrature Zero-IF and Low-IF RF receivers. The RF front-end match the RX input impedance with the antenna, amplifies the received signal with low noise insertion, and the signal is down-converted to a zero or low intermediate

Figure 1 – Typical RF receiver architectures: (a) Zero-IF, and (b) Low-IF.

Source: author

frequency (IF), according to the PLL-based local oscillator frequency. In the low-voltage implementations, passive mixer and transimplement amplifiers (TIA) are commonly used to the down-conversion process and digitally-controlled oscillator (DCO) is preferred to implement the PLL (YIN et al., 2018; POURMOUSAVIAN et al., 2018). Due to the relaxed noise-figure (NF) requirement of the BLE standard, the LNA can be removed from the front-end (MASUCH; DELGADO-RESTITUTO, 2013a; BRYANT; SJOLAND, 2014), or it can be designed using single NMOS transistor two stage amplifiers with proper transformer coupling and power-gating circuits to present sub-mW power dissipation (ZHANG; MIYAHARA; OTIS, 2013; YI et al., 2018). The baseband part uses active filters and programmable gain amplifiers (PGA) to provide to the analog to digital converter (ADC) a filtered and amplified signal. In the Zero-IF RX a low-pass filter (LPF) is adopted to select the desired channel bandwidth and to attenuate the blockers, while a band-pass filter (BPF) is used in Low-IF RX for the channel selection and to reject the image signal generated after the down-conversion process. The continuous time active-RC topologies are preferred to implement the baseband filter and amplifiers because of its higher linearity in comparison to the  $g_m$ -C topologies at the ULV range (ZHANG; MIYAHARA; OTIS, 2013; BALANKUTTY et al., 2010). These circuits have the operational amplifier as the main active block and due to the required gain-bandwidth product (GBW), the ULV

topologies tend to present more than 100  $\mu$ W of power dissipation per pole, even using single-stage amplifiers (RASEKH; BAKHTIAR, 2017; YE et al., 2013) and optimized designs (ALZAHER; TASADDUQ; AL-AMMARI, 2013). The ADC circuit is commonly implemented using a successive approximation register (SAR) architecture to reduce the number of active blocks and, consequently, to reduce the power dissipation (HERNANDEZ; SEVERO; NOIJE, 2018).

### 1.1 Objectives

Due to the need for low energy RF transceivers and on the lack of ultra-low voltage (ULV) and ultra-low power (ULP) baseband circuits, this work aims to propose new topologies of operational transconductance amplifier (OTA) and negative transconductor to be applied in active-RC filters and amplifiers used in the baseband section of BLE RF receivers. To reach the ULP operation, an inverter-based single-stage (unbuffered) operational amplifier is designed to avoid the power dissipation on the phase margin compensation required in multiple stages amplifier. To address the low voltage gain and the loading effect, a compensation scheme using a negative input transconductance is proposed. To achieve the proper operation at the ULV range, only two-stacked transistors and fully-differential topologies are applied in all the circuit implementation. Based on the proposed OTA and negative transconductor, a third order complex BPF, a programmable gain amplifier and a Tow-Thomas biquad with programmable gain capability are designed and prototyped in sub-micron CMOS technologies to operate at the 0.4 V power supply.

Additionally, as specific objectives, this work aims to analyze the input negative transconductor compensation technique and its effects on the active-RC circuits. For this circuits, a design methodology and a low-cost solution to the characterization of ULV and ULP active filter and amplifiers are proposed.

### 1.2 The Main Contributions of this Thesis

The work developed in this thesis introduces the following contributions:

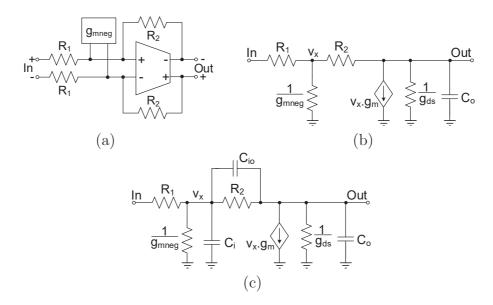

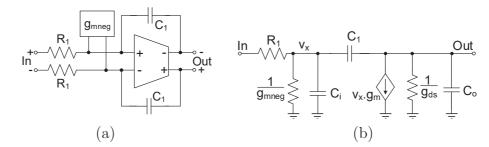

• The small-signal analysis of the single-stage OTA with negative input transconductance compensation is performed, considering the effects of the parasitic input and feedback capacitances in the closed-loop amplifier and active integrators. Additionally, the equivalent output and input-referred noise of the closed-loop amplifier are analyzed with and without using the negative input transconductance. Based on these analysis, the optimal single-stage OTA compensation can be reached without instability issues and the noise power added by the negative transconductor can be estimated.

- A novel topology of ULV negative transconductor is proposed using a replica circuit and the PMOS bulk forward bias to reduce the effects of the process and temperature variations. The proposed technique reduced the variation of the input common-mode DC voltage and extended the range of adjustable transconductance.

- An improved ULV inverter-based OTA is proposed, presenting a reasonable commonmode rejection rate. A novel NMOS bulk replica bias combined to the common-mode feedback circuit is introduced to reduce the variabilities on the output common-mode DC voltage and the current drained from the power supply.

- This work also introduces the use of a programmable negative transconductor connected at the inputs of the single-stage OTAs to allow the development of programmable gain amplifiers that presents the optimal compensation in all the gain modes (SEVERO; NOIJE, 2018). The proposed strategy is applied to the design of an ULP programmable gain amplifier (PGA) and a programmable gain Tow-Thomas second-order biquad.

- We have also proposed in this work a design methodology based on the transistor operation point to size all the CMOS transistors. A simulation-based tool was implemented to allow the use of the proposed methodology in any fabrication process. Additionally, we have improved the UCAF optimization-based design tool (SEVERO et al., 2012) by including the operation point-driven approach to improve the design space exploration efficiency on the design of ULV circuits.

#### 1.3 Thesis Organization

This thesis is organized as follows. After the introduction of Chapter 1, the analysis of the CMOS transistors operation at the ULV range and the operational amplifiers used in the baseband filters are presented in Chapter 2. Chapter 3 presents the main strategy proposed in this work by using a single-stage operational transconductance amplifier (OTA) and a negative input transconductance to compensate for the reduced voltage gain and loading effects. The circuit topologies proposed in this work and its main characteristics are also presented in Chapter 3. In Chapter 4 a design methodology using an operation point simulation-based tool is proposed to design the ULV circuits. Additionally, an improvement in an optimization-based tool from the literature is also proposed in this chapter. Chapter 5 presents the simulation and experimental results for the application of the proposed circuits on the design of active-filters and programmable gain amplifiers for the baseband section of BLE RF receivers. The strategy used to perform the circuit measurements is presented and detailed on the appendix part. Finally, in Chapter 6 some conclusions to this work are given.

# 2 ULV and ULP Operational Amplifiers for Active-RC Filters

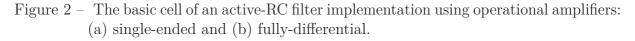

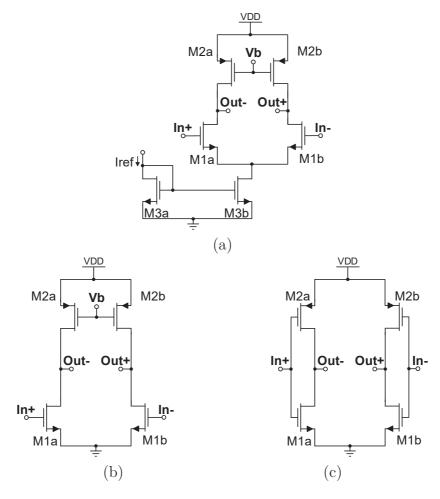

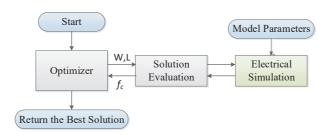

The active-RC filters implementations are based on the use of operational amplifiers with resistors and capacitors to perform the feedback and to control frequency characteristics. Fig. 2(a) and (b) show the basic cell employed to implement active-RC low-pass filters with single-ended or fully-differential (balanced) operational amplifiers, respectively. The closed-loop nature of the active-RC implementation reduces the swing voltage at the amplifier inputs and improve its linearity, as illustrated by the sinusoidal waves in Fig. 2. This characteristic makes the active-RC topologies better than the  $g_m$ -C topologies to operate at the ULV range. The use of balanced amplifiers instead of using single-ended amplifiers also is preferred to implement ULV circuits since they have twice the output voltage swing of the single-end implementations, as illustrated in Fig. 2. Furthermore, the use of fully-differential filter topologies facilitates the implementation of high order integrator-based active filters, considering that both the negative and positive signals are available (SEDRA; SMITH, 2007). In contrast to this, a common-mode feedback circuit (CMFB) is required to control the output common-mode signal of the balanced amplifier. The design of this circuit can increase the operational amplifier power dissipation considerably if the conventional CMFB circuits topologies are used at the ULV range (HARJANI; PALANI, 2015; DUQUE-CARRILLO, 1993).

The power dissipated by the active-RC filters is mainly due to the operational amplifier power dissipation since it is the only active block employed. On the other hand, the power dissipation of the operational amplifier is directly related to the circuit topology and to the fabrication process. Based on these assumptions, the following sections present the analysis of the CMOS transistor operating at the ULV range, where the main electrical characteristics and the design strategies are presented using experimental device characterization curves. After this part, the characteristics of the reduced power dissipation operational amplifier at the ULV range and the design techniques previous reported in the literature are analyzed.

### 2.1 CMOS Transistors at the ULV Range

The electrical characteristics of the CMOS transistors are dependent on the channel Width (W) and Length (L), the fabrication process and on the bias voltage. The W and L parameters are the designer free variables, while the bias voltage is limited by the used power supply voltage level and by the circuit topology.

Source: author

In the following subsections, the main characteristics of the CMOS transistor operation at the ULV range are analyzed using some experimental device I-V curves from the TSMC 130nm CMOS process. The I-V curves are obtained with the characterization of long channel transistors M1 (Low- $V_T$ ) and M2 (standard- $V_T$ ), and on variable channel length transistors M3a, M3b and M3c (Low- $V_T$ ). Appendix A shows the test transistors sizes, the fabricated structures, and the measurement strategy employed to obtain the devices I-V curves.

Although the transistor bulk terminal is the best terminal voltage to be adopted as a reference for the transistor characteristics analysis (SCHNEIDER; GALUP-MONTORO, 2010), this work uses a common-source reference to make easier the analysis of the bulk forward bias. Additionally, the circuits proposed in this work, shown in Chapter 3, are composed of only two-stacked devices, and the source terminal is also used as a reference.

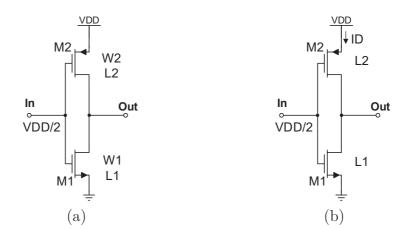

#### 2.1.1 Current Density and Channel Inversion Level

The CMOS transistor drain current  $(I_D)$  is directly dependent on the gate to source  $(V_{GS})$  and on the drain to source  $(V_{DS})$  voltages. The  $I_D$  is also directly proportional to the channel width (W) and inversely proportional to the channel length (L). Thus, the

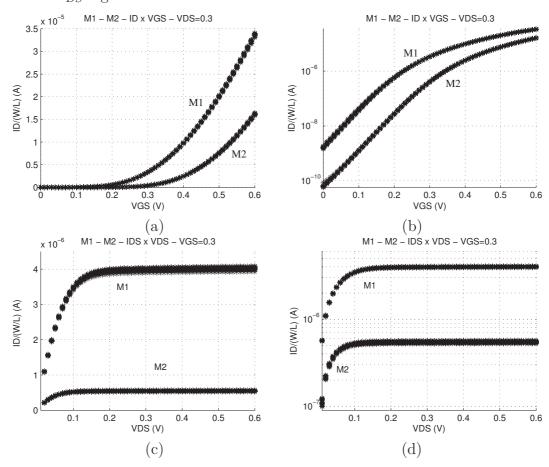

Figure 3 – The measured drain current density  $(I_D/(W/L))$  related to the  $V_{GS}$  and  $V_{DS}$  voltages of the test transistors M1 and M2: (a)  $I_D/(W/L) \times V_{GS}$  linear, (b)  $I_D/(W/L) \times V_{GS}$  logarithmic, (c)  $I_D/(W/L) \times V_{DS}$  linear and (d)  $I_D/(W/L) \times V_{DS}$  logarithmic.

Source: author

transistor drain current density can be evaluated as the  $I_D/(W/L)$  ratio and it is one of the most important parameters for the ULV operation. The lower  $I_D/(W/L)$  is, the higher should be the transistor W/L aspect ratio do present the target drain current. Fig. 3 shows the measured drain current density  $(I_D/(W/L))$  of the M1 and M2 test transistors related to the  $V_{GS}$  and  $V_{DS}$  voltages, using both linear and logarithms scales. The  $V_{GS}$  voltage controls the channel inversion level while the  $V_{DS}$  defines the triode and saturation regions. The border between the triode and saturation regions is defined by the saturation voltage  $(V_{DS_{SAT}})$  that is analyzed in section 2.1.2.

For long channel devices, at the saturation region, the drain current density is only changed by the channel inversion level. The channel inversion can be divided into weak (WI), moderated (MI) and strong (SI) inversion levels, according to the current conduction mechanism. At the WI the current conduction is dominated by charge carriers diffusion in the channel region and  $I_D/(W/L)$  can be estimated by using Eq. 2.1. On the other hand, at the SI the current conduction mechanism is dominated by charge carriers drift,

|                 | Overdrive voltage | Inversion Coefficient | Transistor Efficiency |

|-----------------|-------------------|-----------------------|-----------------------|

| Inversion Level | $V_{GS} - V_T$    | $I_C = I_D / I_0$     | $g_m/I_D$             |

| Weak            | < -60 mV          | < 0.1                 | $> 20 V^{-1}$         |

| Moderated       | -60 to 200 mV     | 0.1 to 10             | 10 to 20 $V^{-1}$     |

| Strong          | > 200  mV         | > 10                  | $< 10 V^{-1}$         |

Table 2 – Empirical channel inversion level classification for a NMOS transistor

and the current density can be estimated by using the classical quadratic model of Eq. 2.3. In the MI level, both the drift and the diffusion current conduction mechanism are present, and it can be modeled using more complex equations, as presented by Schneider and Galup-Montoro (2010), and Tsividis (2003). The technology current  $(I_0)$ , used in Eq. 2.1, can be calculated using Eq. 2.2.

$$I_D/(W/L) = I_0 \cdot \exp\left(\frac{V_{GS} - V_T}{n.\phi_T}\right) \cdot \left[1 - \exp\left(-\frac{V_{DS}}{\phi_T}\right)\right] \approx I_0 \cdot \exp\left(\frac{V_{GS} - V_T}{n.\phi_T}\right)$$

(2.1)

$$I_0 = 2.n_0.\mu_0.C_{ox}.\phi_T^2 \tag{2.2}$$

$$I_D/(W/L) = \frac{\mu_0 C_{ox}}{2} (V_{GS} - V_T)^2 (1 + \lambda V_{DS}) \approx \frac{\mu_0 C_{ox}}{2} (V_{GS} - V_T)^2$$

(2.3)

where:  $V_T$  is the device threshold voltage parameter, n is the sub-threshold slope factor,  $\phi_T$  is the thermal voltage,  $n_0$  is the bulk factor,  $\mu_0$  is the low electric field mobility parameter,  $C_{ox}$  is the oxide capacitance and  $\lambda$  is channel length modulation parameter (COLOMBO et al., 2011).

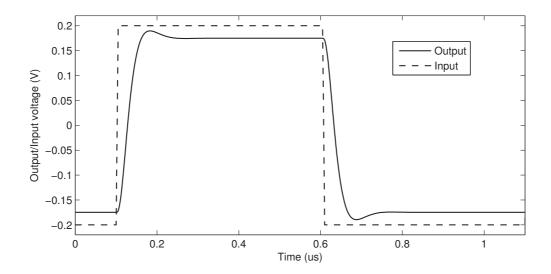

Based on Eq. 2.1 and 2.3 we can verify that the drain current density is directly proportional to the gate effective  $(V_{G_{eff}})$  or overdrive  $(V_{OD})$  voltage, defined as  $V_{GS} - V_T$ . As shown in Fig. 3(a) and (b), the test transistor M1 has higher values of  $I_D/(W/L)$  than M2 at the same  $V_{GS}$  voltage. It occurs due to the difference on the  $V_{OD}$  voltage since M1 is a low- $V_T$  device with  $V_T$  equal to 250 mV and M2 is a standard- $V_T$  device with 365 mV of  $V_T$ . The classification of WI, MI and SI are empirical, and it is given according to the  $V_{OD}$ voltage, as shown in Table 2. Besides  $V_{OD}$ , the inversion level coefficient ( $I_c = I_D/I_0$ ) and the transistor efficiency given by the  $g_m/I_D$  ratio, where  $g_m$  is the gate transconductance, can also be used to define the channel inversion level, as shown in Table 2.