## UNIVERSIDADE DE SÃO PAULO ESCOLA DE ENGENHARIA DE SÃO CARLOS

# CÉSAR WILLIAM VERA CASAÑAS

# PROJETO DE AMPLIFICADORES DE BAIXO RUÍDO USANDO ALGORITMOS METAHEURÍSTICOS

## CÉSAR WILLIAM VERA CASAÑAS

# PROJETO DE AMPLIFICADORES DE BAIXO RUÍDO USANDO ALGORITMOS METAHEURÍSTICOS

Dissertação apresentada à Escola de Engenharia de São Carlos da Universidade de São Paulo, como parte dos requisitos para obtenção do título de Mestre em Ciências, Programa de Engenharia Elétrica.

Área de Concentração: Telecomunicações.

Orientador: Prof. Dr. João Navarro Soares Júnior.

São Carlos Maio de 2013

Trata-se da versão corrigida da dissertação. A versão original se encontra disponível na EESC/USP que aloja o Programa de Pós-Graduação de Engenharia Elétrica.

AUTORIZO A REPRODUÇÃO TOTAL OU PARCIAL DESTE TRABALHO, POR QUALQUER MEIO CONVENCIONAL OU ELETRÔNICO, PARA FINS DE ESTUDO E PESQUISA, DESDE QUE CITADA A FONTE.

Vera Casañas, César William V335p Projeto de Amplificadores

Projeto de Amplificadores de Baixo Ruído Usando Algoritmos Metaheurísticos / César William Vera Casañas; orientador Prof. João Navarro Soares. São Carlos, 2013.

Dissertação (Mestrado) - Programa de Pós-Graduação em Engenharia Elétrica e Área de Concentração em Telecomunicações -- Escola de Engenharia de São Carlos da Universidade de São Paulo, 2013.

1. Transistor MOS. 2. LNA. 3. Compromisso. 4. Figura de ruído. 5. Ganho. 6. Linearidade. 7. Algoritmos Genéticos. 8. Recozimento simulado. I. Título.

#### FOLHA DE JULGAMENTO

Candidato: Engenheiro CESAR WILLIAN VERA CASAÑAS.

Título da dissertação: "Projeto de amplificadores de baixo ruído usando algoritmos metaheurísticos".

Data da defesa: 27/05/2013

Comissão Julgadora:

Resultado:

Prof. Dr. João Navarro Soares Júnior (Orientador)

(Escola de Engenharia de São Carlos/EESC)

APRUVA DO

Prof. Titular Amílcar Careli César

(Escola de Engenharia de São Carlos/EESC)

AP NOVADO

Prof. Dr. Cláudio Fabiano Motta Toledo

(Instituto de Ciências Matemáticas e de Computação/USP)

APROVADO

Coordenador do Programa de Pós-Graduação em Engenharia Elétrica e Presidente da Comissão de Pós-Graduação:

Prof. Titular Denis Vinicius Coury

#### **AGRADECIMENTOS**

Agradeço a meu orientador, professor João Navarro, pela confiança, paciência, orientação e tempo dedicado.

Agradeço a minha família, mesmo distante tenho certeza que torceram, torcem e torcerão por mim incondicionalmente.

O meu muito obrigado a Rodrigo Alberto Llorente, o primeiro passo para este logro foi dele.

Quero também agradecer a todos meus amigos, nacionais, internacionais, locais, distantes ou próximos, que me ajudaram de uma ou outra forma a conseguir este logro. Dentre eles gostaria citar a Julián Villamarín, Fredy Morales e Andrés Coca, ótimos amigos.

Maísa Ramos, para com você faltariam palavras de agradecimentos.

Fico grato ao CNPq pelo apoio econômico oferecido.

A todo o pessoal técnico-administrativo da Pós-Graduação de Engenharia Elétrica o meu agradecimento.

#### Resumo

O projeto de amplificadores de baixo ruído (LNA) aparenta ser um trabalho simples pelos poucos componentes ativos e passivos que o compõe, porém a alta correlação entre os seus parâmetros de projeto dificulta muito esse trabalho. Esta dissertação apresenta uma proposta para contornar essa dificuldade: o uso de algoritmos metaheurísticos, em particular algoritmos genéticos e simulated annealing. Algoritmos metaheurísticos são técnicas avançadas que emulam princípios físicos ou naturais para resolver problemas com alto grau de complexidade. Esses algoritmos estão emergindo nos últimos anos porque têm mostrado eficiência e eficácia. São feitos neste trabalho os projetos de três LNAs, dois (LNA1 e LNA2) para sistemas com arquitetura homódine (LNA com carga capacitiva) e um (LNA3) para sistemas com arquitetura heteródine (LNA com carga resistiva) utilizando-se algoritmos genéticos e simulated annealing (recozimento simulado). Apresenta-se inicialmente a análise detalhada da configuração escolhida para os projetos (fonte comum cascode com degeneração indutiva FCCDI). A frequência de operação dos LNAs é 1,8 GHz e a fonte de alimentação de 2,0 V. Para o LNA1 e o LNA2 se atingiu uma figura de ruído de 2,8 dB e 3,2 dB, consumo de potência de 6,8 mW e 2,7 mW e ganho de tensão de 22 dB e 24 dB, respectivamente. Para LNA3 se atingiu uma figura de ruído de 3,5 dB, consumo de potência de 7,8 mW e ganho de tensão de 15,5 dB. Os resultados obtidos e comparações feitas com LNAs da literatura demonstram viabilidade e eficácia da aplicação de algoritmos metaheurísticos no projeto de LNA. Neste trabalho utilizaram-se as ferramentas ELDO (simulador de circuitos elétricos), versão 2009.1 patch1 64 bits, ASITIC (para projetar e simular os indutores), versão 03.19.00.0.0 e MATLAB (o toolbox fornece os algoritmos metaheurísticos), versão 7.9.0.529 R2009b. Além disso, os projetos foram desenvolvidos na tecnologia CMOS 0,35 um da AMS (Austria Micro Systems).

Palavras chaves – transistor MOS, LNA, compromisso, figura de ruído, ganho, linearidade, algoritmos genéticos, *simulated annealing*.

#### Abstract

The design of low noise amplifiers (LNA) seems to be a simple work because the small number of active and passive device that they are composes, nevertheless the high trade off of LNA parameters complicates very much the work. This research presents a proposal to contour act the obstacle: to use metaheuristic algorithms, in special genetic algorithms and simulated annealing. The metaheuristic algorithms are advanced techniques that emulate physics or natural principles to solve problems with high grade of complexity. They have been emerging in the last years because they have shown effectiveness and efficiency. In this dissertation were designed three LNAs using genetic algorithms and simulated annealing: two (LNA1 and LNA2) to homódine architecture (LNA with capacitive load) and one (LNA3) to heteródine architecture (LNA with resistive load). First it is show the detailed analysis of configuration chosen to the designs (common source cascode with inductive degeneration). The operation frequency is 1.8 GHz and power supply is 2.0 V for all LNAs. LNA1 and LNA2 reached a noise figure of 2.8 dB and 3.2 dB, a dissipation power of 6.8 mW and 2.7 mW, and a voltage gain of 22 dB and 24 dB respectively. LNA3 reached 3.5 dB of noise figure, 7.8 mW of dissipation power, and 15.5 dB of voltage gain. The results obtained and the comparisons with LNAs from the literature demonstrate that the metaheuristic algorithms show efficiency and effectiveness in the design of LNA. This study was developed with the help of the tools ELDO (electric circuit simulator) version 2009.1 patch1 64 bits, ASITIC (to design and simulate the inductors) version 03.19.00.0.0, and MATLAB (the toolbox provides the metaheuristic algorithms) version 7.9.0.529 R2009b. Furthermore, the designs were developed on CMOS 0.35 AMS (Austria Micro Systems) technology.

Keywords: transistor MOS, LNA, trade-off, noise figure, gain, linearity, genetic algorithm, simulated annealing.

# Lista de figures

| Figura 1 - Blocos básicos num sistema RF                                                 | 12 -     |

|------------------------------------------------------------------------------------------|----------|

| Figura 2 - Blocos do transmissor e do receptor                                           | 12 -     |

| Figura 3 - Circuito receptor para RF com conversão direta. Em vários pontos é mostrado   | 0 0      |

| espectro do sinal                                                                        | 13 -     |

| Figura 4 - Parâmetros de projeto de um LNA                                               | 14 -     |

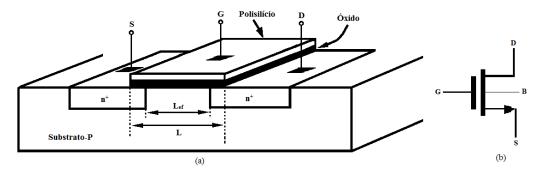

| Figura 5 - Transistor NMOS: (a) Estrutura física (b) Símbolo elétrico                    | 19 -     |

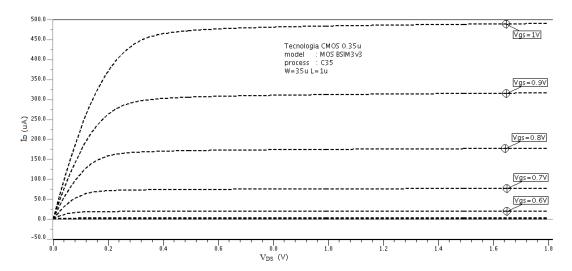

| Figura 6 - $I_{DS}$ versus $V_{DS}$ para diferentes valores de $V_{GS}$                  | 22 -     |

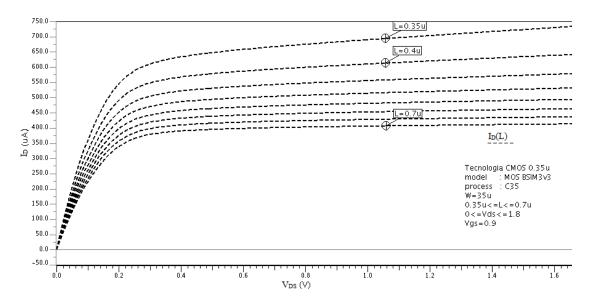

| Figura 7 - Modulação do Comprimento de Canal                                             | 23 -     |

| Figura 8 - Capacitâncias intrínsecas de um transistor NMOS                               | 25 -     |

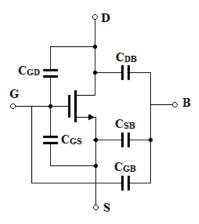

| Figura 9 - Capacitâncias entre os terminais do NMOS                                      | 26 -     |

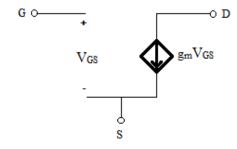

| Figura 10 - Modelo de pequenos sinais simples                                            | 27 -     |

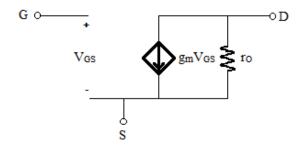

| Figura 11 - Modelo de pequenos sinais com resistor                                       | 27 -     |

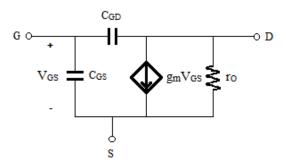

| Figura 12 - Modelo pequenos sinais com capacitores                                       | 28 -     |

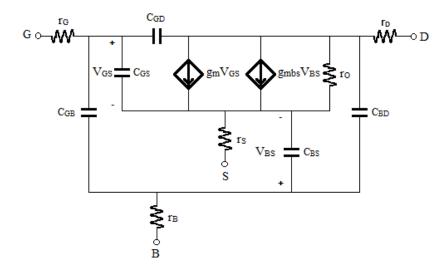

| Figura 13 - Modelo de pequenos sinais Completo                                           | 28 -     |

| Figura 14 - Modelo do ruído térmico para um resistor: (a) tensão (b) corrente            | 31 -     |

| Figura 15 - Modelo de ruído do transistor MOS                                            | 32 -     |

| Figura 16 - Impedâncias do LNA                                                           | 35 -     |

| Figura 17 - Amplitude de saída, Ao, versus amplitude de entrada, Ai; a. ponto de compre  | essão    |

| de 1dB; b. ponto de interseção de 3a ordem                                               | 36 -     |

| Figura 18 - Arquiteturas (a) Heteródine (carga resistiva) (b) Homódine (carga capacitiva | .)- 38 - |

| Figura 19 - Topologias: (a) Porta Comum (PC), (b) Fonte Comum (FC), (c) Dreno comu       | ım       |

| (DC)                                                                                     | 39 -     |

| Figura 20 - (a) Configuração FC com DI, (b) PC com DI                                    | 40 -     |

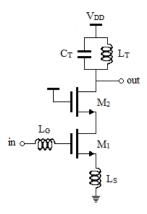

| Figura 21 - Configuração Fonte Comum Cascode com degeneração indutiva (FCCDI)            | 41 -     |

| Figura 22 - Indutor passivo: parâmetros de construção                                    | 43 -     |

| Figura 23 - Parâmetros do indutor e seu modelo PI                                        | 44 -     |

| Figura 24 - Modelo de indutor passivo gerado com ASITIC                                  | 45 -     |

| Figura 25 - Indutor Ativo e sua Indutância equivalente                                   | 47 -     |

| Figura 26 - Indutor Ativo Simples                                                            | - 48 - |

|----------------------------------------------------------------------------------------------|--------|

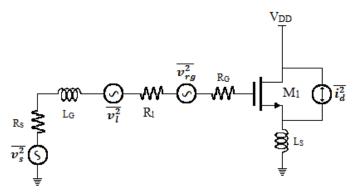

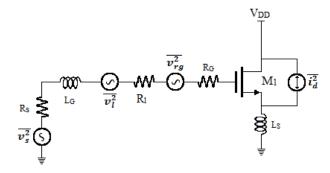

| Figura 27 - Modelo para análise de ruído                                                     | - 49 - |

| Figura 28 - Modelo de pequeno sinal da Figura 21 para calcular o ganho de tensão             | - 50 - |

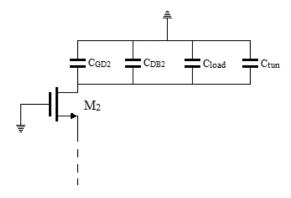

| Figura 29 - $C_T = C_{GD2} + C_{DB2} + C_{load} + C_{tun}$ .                                 | - 51 - |

| Figura 30 - Circuito para o casamento da impedância de entrada                               | - 52 - |

| Figura 31 - Modelo de pequenos sinais simplificado da Figura 30                              | - 52 - |

| Figura 32 - Estágio FC para rede da saída                                                    | - 54 - |

| Figura 33 - Modelo de pequenos sinais para calcular a impedância de saída                    | - 54 - |

| Figura 34 - Circuito final para calcular a impedância de saída                               | - 55 - |

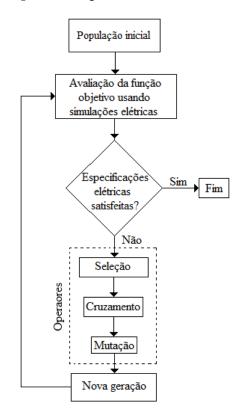

| Figura 35 - Diagrama de fluxo de GA                                                          | - 61 - |

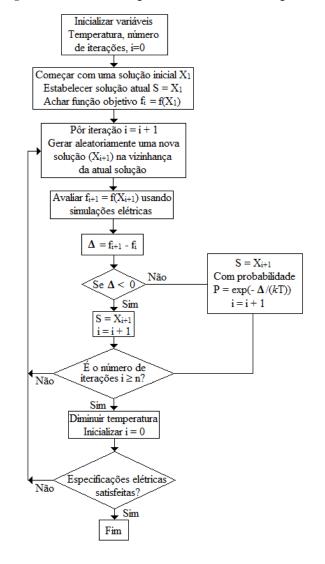

| Figura 36 - Processo do algoritmo Simulated Annealing.                                       | - 64 - |

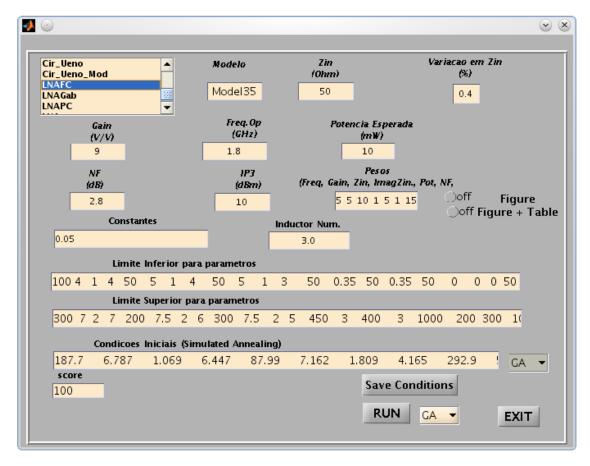

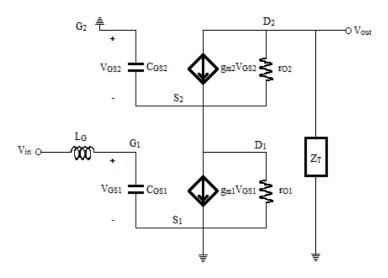

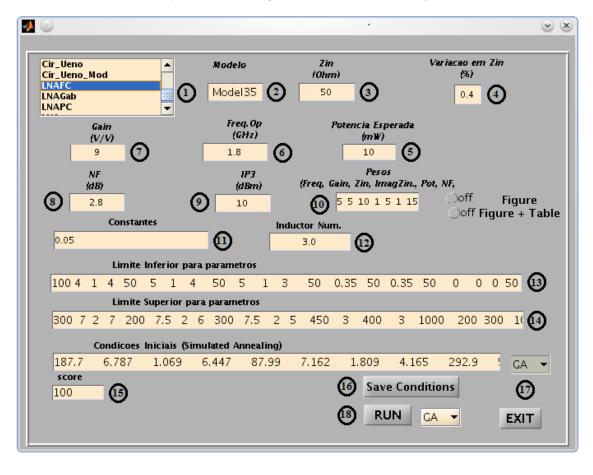

| Figura 37 - Interface de operação da ferramenta CircuiOp                                     | - 67 - |

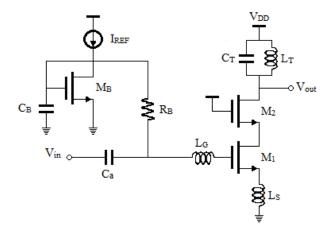

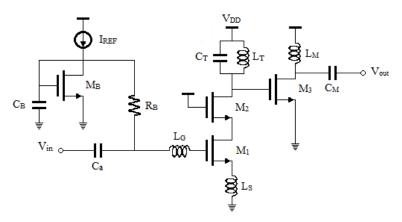

| Figura 38 - Esquemático para os LNA1 e LNA2                                                  | - 68 - |

| Figura 39 - Esquemático para o LNA3                                                          | - 68 - |

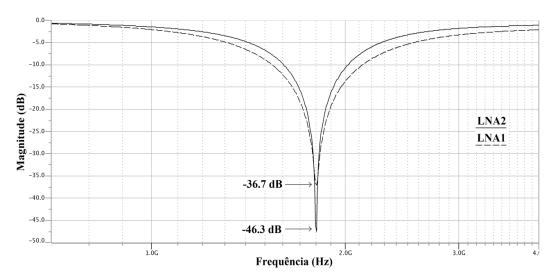

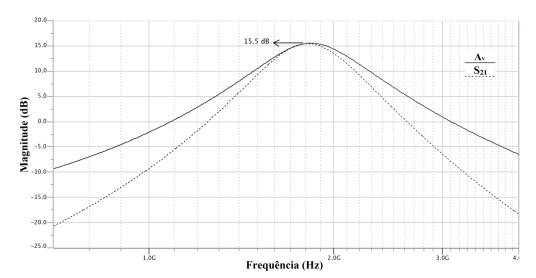

| Figura 40 - Ganho de tensão versus Frequência, LNA1 e LNA2                                   | - 73 - |

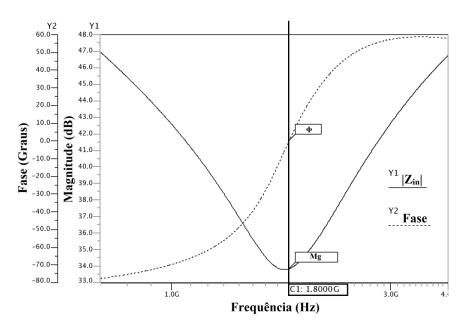

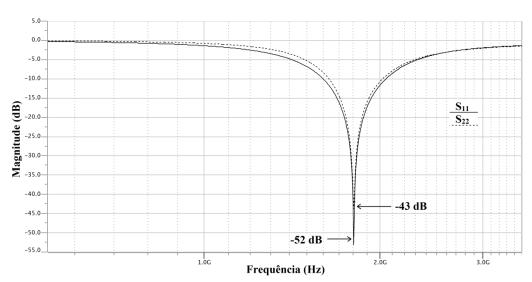

| Figura 41 - Coeficiente de reflexão S <sub>11</sub>                                          | - 74 - |

| Figura 42 - Magnitude da impedância e fase versus Frequência. A resposta ideal na frequência | ência  |

| de operação é 50 $\Omega$ @0°                                                                | - 74 - |

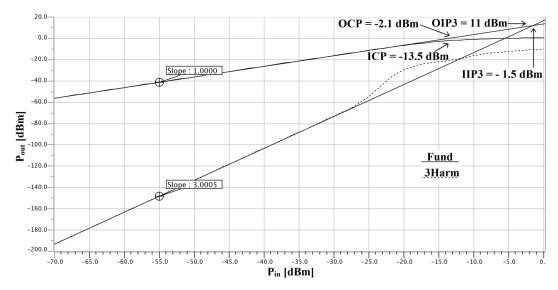

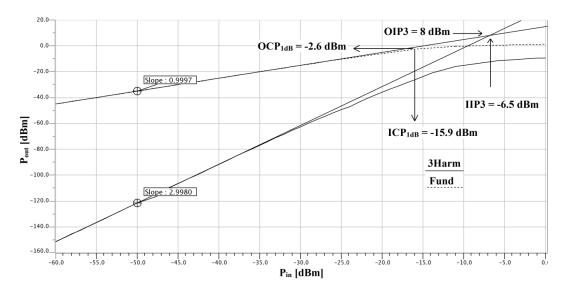

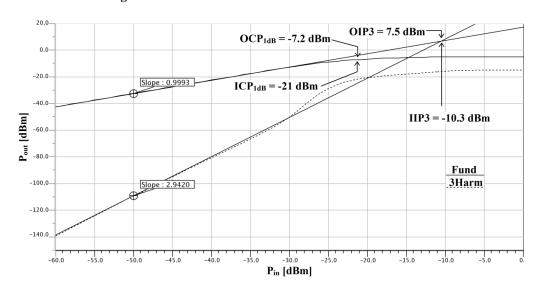

| Figura 43 - Potência na saída versus Potência na entrada: LNA1                               | - 76 - |

| Figura 44 - Potência na saída versus Potência na entrada: LNA2                               | - 76 - |

| Figura 45 - Ganhos de tensão e potência versus frequência: LNA3                              | - 78 - |

| Figura 46 - Coeficientes de reflexão S <sub>11</sub> e S <sub>22</sub>                       | - 79 - |

| Figura 47 - Potência na saída versus Potência na entrada: LNA3                               | - 79 - |

| Figura 48 - Configuração FCCDI                                                               | - 90 - |

| Figura 49 - Modelo para análise de ruído                                                     | - 91 - |

| Figura 50 - FCCDI: (a) Esquemático elétrico (b) Modelo de pequeno sinal                      | - 93 - |

| Figura 51 - Modelo de pequenos sinais reduzido da configuração FCCDI                         | - 94 - |

| Figura 52 - Interface gráfica da ferramenta CircuicOp                                        | - 96 - |

|                                                                                              |        |

# Lista de tabelas

| Tabela 1 - Especificações de projeto                                       | 15 -  |

|----------------------------------------------------------------------------|-------|

| Tabela 2 - Tensão associadas ao transistor MOS                             | 20 -  |

| Tabela 3 - Capacitâncias Intrínsecas do transistor MOS                     | 25 -  |

| Tabela 4 - Capacitâncias dos terminais na saturação                        | 26 -  |

| Tabela 5 - Resumo das configurações com DI                                 | 42 -  |

| Tabela 6 - Descrição dos componentes do modelo PI                          | 44 -  |

| Tabela 7 - Dimensões do indutor da Figura 24                               | 45 -  |

| Tabela 8 - Valores obtidos com ASITIC                                      | 45 -  |

| Tabela 9 - Dispositivos e variáveis de projeto                             | 56 -  |

| Tabela 10 - Conceitos gerais dos algoritmos genéticos                      | 60 -  |

| Tabela 11 - Faixa de variação das dimensões                                | 69 -  |

| Tabela 12 - Especificações de projeto para os LNAs                         | 70 -  |

| Tabela 13 - Pesos da função objetivo                                       | 70 -  |

| Tabela 14 - Parâmetros do algoritmo GA utilizados pela ferramenta CircuiOp | 71 -  |

| Tabela 15 - Parâmetros do algoritmo SA utilizados pela ferramenta CircuiOp | 72 -  |

| Tabela 16 - Dimensões dos dispositivos do LNA1                             | 72 -  |

| Tabela 17 - Dimensões dos dispositivos do LNA2                             | 73 -  |

| Tabela 18 - Melhores resultados para LNA3 com GA+SA                        | 77 -  |

| Tabela 19 - Dimensões dos dispositivos do LNA3                             | 77 -  |

| Tabela 20 - Resumo dos LNA                                                 | 80 -  |

| Tabela 21 - Comparação com outros LNAs (Todos FCCDI)                       | 81 -  |

| Tabela 22 - Descrição dos parâmetros do modelo BSIM3v3                     | 105 - |

# Sumário

| CAPÍTU   | LO 1 INTRODUÇÃO                             | 11 - |

|----------|---------------------------------------------|------|

| CAPÍTU   | LO 2 REVISÃO TEÓRICA                        | 18 - |

| 2.1.     | Transistor MOS                              | 18 - |

| 2.1.1.   | EFEITO DO CORPO                             | 22 - |

| 2.1.2.   | MODULAÇÃO DE COMPRIMENTO DE CANAL           | 22 - |

| 2.1.3.   | Transcondutância                            | 24 - |

| 2.1.4.   | CAPACITÂNCIAS INTRÍNSECAS                   | 25 - |

| 2.1.5.   | MODELO DE PEQUENO SINAL                     | 26 - |

| 2.2.     | Amplificadores de Baixo Ruído – LNA         | 29 - |

| 2.2.1.   | Parâmetros de projeto                       | 29 - |

| 2.2.1    | .1. Fator de ruído/Figura de ruído          | 30 - |

| 2.2.1    | .2. Ruído                                   | 30 - |

| 2.2.1    | .3. Ganho                                   | 33 - |

| 2.2.1    | .4. Coeficiente de reflexão                 | 34 - |

| 2.2.1    | .5. Linearidade                             | 35 - |

| 2.2.1    | .6. Fator de Estabilidade                   | 37 - |

| 2.2.2.   | Arquiteturas de LNAs                        | 37 - |

| 2.2.3.   | INDUTORES                                   | 42 - |

| 2.2.3.1. | . Indutores Passivos                        | 43 - |

| 2.2.3.2. | . Indutores ativos                          | 46 - |

| 2.2.4.   | CONSIDERAÇÕES DE PROJETO DA TOPOLOGIA FCCDI | 48 - |

| 2.2.4.1. | FATOR DE RUÍDO                              | 49 - |

| 2.2.4.2. | . Ganho de tensão                           | 50 - |

| 2.2.4.3. | . IMPEDÂNCIA DE ENTRADA                     | 51 - |

| 2.2.4.4. | . IMPEDÂNCIA DE SAÍDA                       | 53 - |

| 2.3.     | COMPLEXIDADE DO PROJETO DE UM LNA           | 56 - |

| CAPÍT | ULO 3 ALGORITMOS METAHEURÍSTICOS                                                              | 58 -  |

|-------|-----------------------------------------------------------------------------------------------|-------|

| 3.1.  | ALGORITMOS GENÉTICOS (GAS)                                                                    | 59 -  |

| 3.2.  | SIMULATED ANNEALING (SA)                                                                      | 62 -  |

| CAPÍT | ULO 4 RESULTADOS                                                                              | 68 -  |

| CONCI | LUSÃO                                                                                         | 82 -  |

| REFER | ÊNCIAS                                                                                        | 85 -  |

| APÊND | ICES E ANEXOS                                                                                 | 89 -  |

| APÊNI | DICE A - FATOR DE RUÍDO                                                                       | 90 -  |

| APÊNI | DICE B - GANHO DE TENSÃO                                                                      | 93 -  |

| APÊNI | DICE C - INTERFACE DA FERRAMENTA <i>CIRCUICOP</i>                                             | 96 -  |

| APÊNI | DICE $\operatorname{D}$ – $\operatorname{C\'odigo}$ para simulações e medições dos parâmetros | 99 -  |

| ANEX  | KO A - Parâmetros do modelo BSIM3v3                                                           | 104 - |

| ANEX  | O B - TECNOLOGIA USADA POR ASITIC                                                             | 106 - |

# Capítulo 1 INTRODUÇÃO

Na história, os meios de comunicação têm avançado em paralelo com o avanço dos povos. O século 20 foi rico em grandes avanços nessa área, tendo se difundido nele o rádio, a TV, telefonia e as comunicações via satélites. Ao fim do século ainda surgiram a Internet e serviços como o correio eletrônico, a *World Wide Web* ou simplesmente web, a telefonia móvel, a voz sobre IP (telefonia na internet). O homem, no entanto, segue pesquisando e procurando aperfeiçoar tecnologias e meios de comunicação e todas as áreas que envolvem. Uma área de grande interesse ainda hoje é a dos circuitos integrados para radiofrequência (RF). O avanço nesta área proporcionou melhorias nos sistemas de comunicação, com aparelhos portáteis cada vez menores, com menor consumo de potência e mais baratos (RAZAVI, 1998). Nas aplicações de RF como a WLAN's (*Wireless Local Area Network*), o GPS (*Global Positioning System*), o RF ID's (*Radio-Frequency IDentification*), telefonia móvel, Bluetooth, dentre outras, aparecem sistemas nos quais estão presentes esses circuitos integrados de alta frequência.

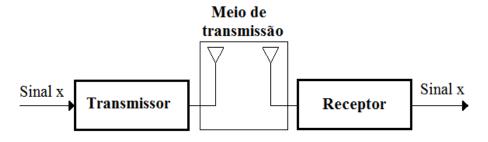

Nas aplicações referidas acima se podem identificar de forma geral três elementos: o bloco transmissor, o bloco receptor e o meio de transmissão (Figura 1). Detalhando um pouco mais, os blocos transmissor e receptor são compostos por outros blocos como mostrado na Figura 2. Observando a Figura 2 o processo de transmissão se pode resumir brevemente assim: uma fonte gera um sinal (e.g. uma mensagem), o bloco transmissor digitaliza o sinal com o auxílio de um conversor análogo digital (*Analog to Digital Converter* ADC), o bloco compressor tira as redundâncias através de algoritmos de compressão (por exemplo *jpeg* para imagens e *mpeg* para áudio e vídeo), o bloco codificador faz a codificação dos dados (a conversão dos dados a uma sequência de pulsos elétricos por exemplo), o bloco modulador faz a modulação (processo no qual uma onda portadora é modificada, em amplitude, frequência ou fase pelo sinal de informação) e, finalmente, o bloco amplificador amplifica o sinal e o envia pelo meio de transmissão ou canal. No processo de recepção o receptor recebe o sinal modulado original atenuado com ruídos adicionados. Agora, o receptor realiza o processo inverso para obter o sinal original no destino, ou seja, amplifica-o, demodula, decodifica-o, descomprime-o e converte-o de novo para um sinal analógico, caso o sinal final

seja analógico, com ajuda de um conversor digital análogo (Digital to Analog Converter DAC).

Figura 1 - Blocos básicos num sistema RF

Figura 2 - Blocos do transmissor e do receptor

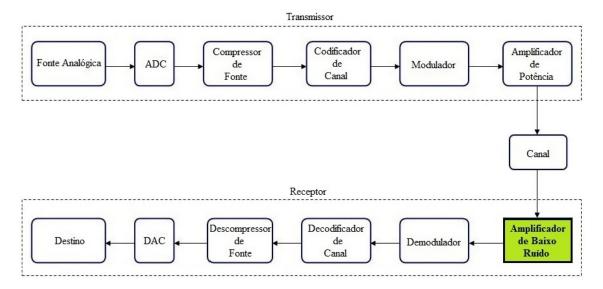

Vamos considerar agora, com um pouco mais de detalhes, a entrada do bloco receptor (*front end*). A Figura 3 indica os blocos que compõe o *front end* de um circuito receptor para conversão direta (RAZAVI, 1998). Nele o sinal que chega pela antena é inicialmente filtrado para seleção da banda de transmissão. Posteriormente é amplificado no bloco LNA, *low noise amplifier*. O sinal vindo do LNA é aplicado a dois misturadores, *mixer*, que fazem multiplicações: no misturador superior a multiplicação é feita pelo sinal vindo do oscilador; no misturador inferior a multiplicação é feita pelo sinal vindo do oscilador atrasado de 90°, gerando uma versão em quadratura. Com esta multiplicação ocorre a translação da banda

desejada para baixo. Uma segunda filtragem é posteriormente aplicada para selecionar o canal desejado dentro da banda e, por fim, os sinais resultantes são amplificados. Um bloco demodulador recebe então o sinal do canal desejado com sua versão em quadratura e, efetivamente, recobra a informação transmitida (comprimida e decodificada). Este demodulador, no caso mais simples, pode ser apenas um *flip-flop* tipo D.

Figura 3 - Circuito receptor para RF com conversão direta. Em vários pontos é mostrado o espectro do sinal.

Podemos seguir detalhando e aprofundando cada um dos blocos, filtros, *mixer*, oscilador, etc., mas neste trabalho nos focaremos no circuito integrado de alta frequência responsável por amplificar o sinal no receptor, o LNA.

Geralmente, um circuito LNA é o primeiro circuito do bloco receptor ou, em alguns casos como descrito acima, está precedido de um filtro passa faixas. Este circuito é utilizado para amplificar sinais fracos, da ordem de microvolts (normalmente a ordem de grandeza dos sinais que chegam aos receptores de RF), garantindo a menor inserção de ruído possível ao sistema (LEE, 1998) (RAZAVI, 1998).

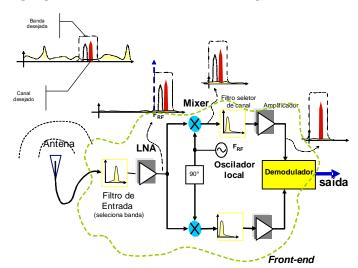

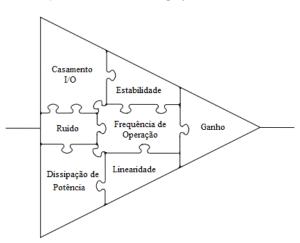

Além de prover suficiente ganho junto com uma baixa inserção de ruído, caracterizado pela figura de ruído que será descrita mais adiante, um LNA também é caracterizado por outros parâmetros igualmente importantes: a frequência de operação, o consumo de potência (que se deseja baixo), o casamento da impedância na entrada e, em alguns casos, na saída, a baixa distorção harmônica e a estabilidade. Na literatura são propostas diversas figuras de

mérito (FOM) (LINTEN, ASPEMYR, *et al.*, 2004) para caracterizar amplificadores de baixo consumo de potência e que são estendidas para os LNAs.

Há entre estes parâmetros, em geral, interdependências sendo a mais importante aquela que ocorre entre a figura de ruído e o consumo de potência (RAZAVI, 1998) (LEE, 1998), onde um baixo consumo de potência causa a degradação no desempenho de ruído.

Figura 4 - Parâmetros de projeto de um LNA

Um sério problema em projetos de LNA´s, como ilustrado na Figura 4 (ROA, 2003) e como reportado na literatura, é obter um bom compromisso (*trade off*) entre os parâmetros de projeto (ALLSTOT, LI e SHEKHAR, 2004) (RAZAVI, 1998) (LEE, 1998). SHAEFFER e LEE (1997) propõem contornar o problema através de uma otimização da figura de ruído que permite a seleção do melhor dispositivo para duas restrições simultâneas: casamento da impedância de entrada e ganho específico ou casamento da impedância de entrada e consumo de potência específica. ROA (2003) propõe uma metodologia de projeto que otimiza o desempenho de ruído e linearidade para consumo de potência e ganho de potência específicos. VAROTTO (2004) propõe uma metodologia diferente baseada no projeto com transistores operando na inversão moderada para alcançar um ótimo desempenho no quesito de figura de ruído.

Todos os trabalhos acima tentam encarar o problema do compromisso dos parâmetros de projeto por diferentes metodologias. Este trabalho tem como objetivo contornar o problema usando uma nova ferramenta que vem sendo estudada para resolver problemas de otimização:

algoritmos de otimização ou algoritmos metaheurísticos. Nosso objetivo é projetar amplificadores de baixo ruído, usando algoritmos de otimização (nosso caso, algoritmos genéticos e *simulated annealing*) para atingir um conjunto de especificações estabelecidas. Na Tabela 1 estão contidas as especificações desejadas, estabelecidas no começo do projeto. Os valores foram determinados como uma média do estado da arte; mas para a frequência de operação se pensou em nossos LNAs como possível bloco de uma das aplicações que operam nessa frequência, 1,8 GHz, por exemplo, como bloco de uma etiqueta *RF-ID*.

Tabela 1 - Especificações de projeto

| Especificaçõo                 | es    |

|-------------------------------|-------|

| Figura de Ruído [dB]          | < 3,2 |

| Ganho [dB]                    | > 15  |

| Consumo de Potência [mW]      | < 10  |

| Coeficientes de reflexão [dB] | < -20 |

| OPC1dB [dBm]                  | > 0   |

| OIP3 [dBm]                    | > 0   |

| Frequência [GHz]              | 1,8   |

A motivação para este estudo está em dois aspectos:

- A equipe de pesquisa do LµS (Laboratório de microsistemas) da SEL EESC USP tem como objetivo obter o conhecimento integral dos algoritmos metaheurísticos para desenvolver métodos de projeto de diferentes circuitos analógicos, entre eles circuitos para as aplicações acima ditas.

- 2. A grande quantidade de aplicações, tanto na área profissional como de entretenimento, onde há a presença de LNAs, por exemplo (RAZAVI, 1998):

- WLAN's: As redes locais sem fio são aplicações para prover comunicação móvel em escritórios, hospitais, fábricas, etc. Operam na banda de 900 MHz até 2,4 GHz. Portabilidade e reconfiguração são características das WLAN's.

- GPS: O sistema de posicionamento global é um sistema de navegação por satélite que fornece a um aparelho receptor móvel a sua posição e a direção a qualquer momento. O GPS é uma aplicação útil para trabalhos de exploração

na terra ou no oceano e para traçar percursos e rotas para veículos terrestres, de voo e navegação. A faixa de operação do GPS é de 1,17 GHz até 1,57 GHz.

- RF-ID's: Sistemas de identificação por radiofrequência são aplicações para identificação automática através de sinais de rádio, recuperando e armazenando dados por meio de etiquetas RFID. Uma etiqueta RFID é um dispositivo transceptor (dispositivo transmissor e receptor) que pode ser colocada em objetos, animais ou pessoas. Estes dispositivos operam na faixa de 900 MHz até 2,4 GHz.

- GSM: Sistema Global para Comunicações Móveis é o padrão mais popular para telefones celulares do mundo. Permite, além da comunicação de voz, a troca de dados entre telefones, acesso a internet e serviço de *roaming* internacional.

- **Bluetooth**: Esta aplicação permite comunicação rápida, segura e barata entre computadores, *smartphone*, telefones celulares, mouses, teclados, impressoras e outros dispositivos, utilizando ondas de rádio no lugar de cabos. É um padrão de comunicação sem fio e de baixo consumo de energia. O alcance é curto e depende da potência de transmissão, sendo de 1 metro (Classe 3), 10 metros (Classe 2) ou até 100 metros (Classe 1). O *Bluetooth* opera na faixa de 2,4 até 2,5 GHz.

Neste trabalho, com auxílio de algoritmos genéticos e *simulated annealing* (recozimento simulado), foram projetados três LNA, dois (LNA1 e LNA2) para sistemas com arquitetura *homódine* (LNA com carga capacitiva) e um (LNA3) para sistemas com arquitetura *heteródine* (LNA com carga resistiva) (RAZAVI, 1998). O trabalho foi desenvolvido na tecnologia AMS (*Austria Micro Systems*) CMOS (*Complementary Metal Oxide Silicon*) 0,35 µm e com o auxílio da ferramenta de simulação de circuitos elétricos ELDO da Mentor Graphics (versão 2009.1 patch1 64 bits), da ferramenta ASITIC (versão 03.19.00.0.0.0) para projetar os indutores passivos e da ferramenta que fornece os algoritmos metaheurísticos, MATLAB (versão 7.9.0.529 R2009b). Para executar essas ferramentas foi utilizado um computador com processador Intel(R) Core(TM) i3 @2,5 GHz, Memória RAM de 3,0 Gb e o sistema operativo foi Linux Open SUSE v11.3.

O trabalho faz parte do projeto de blocos para sistemas de comunicação RF, desenvolvida pela equipe de pesquisa do  $L\mu S$  (Laboratório de microsistemas) da SEL EESC USP.

Este documento está organizado da seguinte forma: no Capítulo dois trata-se do transistor MOS, se faz um percurso sobre sua estrutura, equações características na região de saturação, as capacitâncias intrínsecas e finalmente chegar-se ao modelo de pequeno sinal. Em seguida trata-se do LNA com os parâmetros de projeto, as arquiteturas disponíveis, a arquitetura escolhida e analise detalhado da mesma. No capítulo três se faz uma resenha dos algoritmos genéticos e *simulated annealing* e é apresentada a função objetivo usada na ferramenta *CircuitOp*. Os resultados são apresentados no Capítulo 4 e finalmente as conclusões são apresentadas.

### Capítulo 2 Revisão Teórica

Neste capítulo se tratam basicamente dois assuntos: o transistor como dispositivo componente de circuitos de RF, neste caso de um LNA, e uma breve análise do circuito LNA. Após tratar dos transistores MOS se discute os parâmetros de projeto e os tipos de ruído presentes em LNAs. Em seguida são apresentadas as topologias mais comunmente usadas, vantagens e desvantagens que cada uma tem. Por fim se determina a topologia usada neste estudo com a respectiva justificativa para tal escolha. O objetivo deste capítulo é mostrar a complexidade que envolve o projeto de um LNA.

#### 2.1. Transistor MOS

Esta seção aborda os conceitos gerais do transistor MOS (*metal-oxide semiconductor*). Começamos dizendo que há dois tipos de transistor MOS: NMOS, onde a condução é feita por elétrons, e PMOS, onde a condução é feita por lacunas. A tecnologia CMOS (tecnologia que permite a construção tanto de transistores NMOS como de PMOS) passou, a partir dos anos 80, a ser dominante na fabricação de circuitos integrados devido às vantagens sem igual que ela oferece: altos níveis de integração, baixo consumo de potência e simplicidade de projeto. Nos últimos anos, 75% dos circuitos semicondutores (tanto em quantidade como em valor) foram produzidos em CMOS, fato que adiciona outra vantagem à tecnologia: redução de custos devido à escala de produção. Este quadro não deve ser alterado nos próximos anos (ITRS, 2009).

Circuitos usados em radiofrequência foram, tradicionalmente, implementados com componentes discretos de Arseneto de Gálio (GaAs) ou de Silício na tecnologia BIPOLAR. A partir de meados da década de 90, alternativas tecnológicas têm sido testadas tais como BiCMOS, (MEYER e MACK, 1994), SOA (*Silicon-On-Anything*), (BALTUS e DEKKER, 2000), e CMOS (ABIDI, POTTIE e KAISER, 2000), (LEE e WONG, 2000), (RAZAVI, 1998). Neste tipo de aplicação, a tecnologia CMOS se destaca pelas vantagens já mencionadas e ainda pela possibilidade de obter a integração de todo um sistema num único *chip*: o *front end*, tipicamente analógico e em alta frequência, e o *back end*, tipicamente digital e em baixa frequência. A integração completa de um sistema reduz custos e dimensões e

aumenta a confiabilidade. Em vista disto, a tecnologia CMOS é uma opção viável para implementação de transceptores RF integrados funcionando em frequências de até 5,0 GHz e será utilizada aqui.

Focamos a apresentação feita aqui no transistor NMOS, mas todos os conceitos vistos se aplicam de forma análoga para o transistor PMOS. Na Figura 5(a) (RAZAVI, 2001) se ilustra uma estrutura simplificada de um transistor NMOS, fabricado sobre substrato tipo P (para PMOS seria sobre substrato tipo N). O dispositivo consiste de duas difusões fortemente dopadas tipo N (tipo P para PMOS) que formam a fonte (S) e o dreno (D) respectivamente, uma região condutora, que pode ser metal ou silício policristalino fortemente dopado, geralmente chamada de poly, que opera como porta (G) e uma delgada capa isolante, por exemplo, óxido de silício (SiO<sub>2</sub>), que isola a porta do substrato (GREGORIAN e TEMES, 1986) (RAZAVI, 2001).

O acrônimo MOS, como já dito *metal-oxide semiconductor*, corresponde a porta (metal), ao isolante (óxido) e ao material para formar o canal (semiconductor).

Figura 5 - Transistor NMOS: (a) Estrutura física (b) Símbolo elétrico

Para um transistor MOS fonte e dreno são fisicamente iguais, é dizer, o dispositivo é simétrico; do ponto de vista elétrico, o terminal fonte (*source*) nos transistores NMOS é aquele que é conectado ao menor potencial, e nos transistores PMOS é aquele que está conectado ao maior potencial.

Voltando à Figura 5(a), temos que a distância entre a fonte (*source*) e o dreno (*drain*) é o comprimento de canal, *L*, mas devido à difusão (durante a fabricação as regiões de dreno e fonte avançam sob a área coberto pela porta) o comprimento real ou efetivo de um transistor é

menor que L. Neste trabalho a tecnologia utilizada permite um comprimento de canal mínimo de  $0.35 \ \mu m$ .

A Figura 5 apresenta o transistor NMOS como um dispositivo de três terminais, mas realmente o dispositivo tem quatro terminais porque o substrato - *Bulk* (*B*) - é outro terminal. Na Tabela 2 apresentam-se as tensões que se podem estabelecer nos terminais do transistor e que serão usadas na frente deste estudo.

Tensão

Descrição

$V_{GS}$  Diferença de potencial entre a porta e a fonte

$V_{GD}$  Diferença de potencial entre a porta e dreno

$V_{DS}$  Diferença de potencial entre o dreno e a fonte

$V_{BS}$  Diferença de potencial entre o substrato e a fonte

$V_{RD}$  Diferença de potencial entre o substrato e o dreno

Tabela 2 - Tensão associadas ao transistor MOS

Um transistor MOS pode estar operando, de acordo com a concentração de portadores no canal, em três regiões distintas que são:

- i. Inversão Forte ( $Strong\ Inversion$ ): a tensão  $V_{GS}$  é suficiente para formar um canal com concentração de portadores igual ou superior à concentração de portadores intrínseca do substrato. Observemos que o tipo de portador no canal é diferente do portador intrínseco do substrato. É esta a região de operação estudada normalmente.

- ii. Inversão Fraca (*Weak Inversion*): a tensão  $V_{GS}$  está próxima à tensão de *threshold* do transistor, formando um canal com concentração de portadores inferior a concentração intrínseca de portadores do substrato. Utilizada para circuitos de baixíssimo consumo de potência.

- iii. Inversão Moderada (Moderate Inversion): é uma região de transição, não muito bem definida, entre as regiões de inversão forte e inversão fraca. Equações que descrevem o transistor nesta faixa não são muito precisas.

Caso consideremos apenas a chamada forte inversão, podemos dizer que o transistor estará em corte, triodo ou saturação. Quando  $V_{GS}$  de um transistor NMOS é menor que a tensão de limiar –  $voltage\ threshold$  - da tecnologia ( $V_{TH}$ ) a quantidade de cargas móveis é muito pequena e, portanto, não há praticamente corrente fluindo entre dreno e fonte. Neste

caso se diz que o transistor está na região de corte. O dispositivo está na região do triodo quando a tensão  $V_{GS} \ge V_{TH}$  e a tensão  $V_{DS}$  é tal que  $V_{DS} < V_{GS}$  -  $V_{TH}$ . Neste caso é possível modelar o dispositivo como uma resistência controlada por tensão. A região de saturação é atingida pelo dispositivo quando  $V_{GS} \ge V_{TH}$  e a tensão  $V_{DS}$  é tal que  $V_{DS} > V_{GS}$  -  $V_{TH}$  (RAZAVI, 2010).

Neste trabalho os transistores irão operar apenas em forte inversão, saturação, portanto em seguida serão apresentadas as equações associadas a esta região. Na saturação a corrente do dreno-fonte torna- se quase constante e pode-se expressar, em primeira ordem, como:

$$I_D = \frac{1}{2} \mu_0 C_{ox} \frac{W}{I} (V_{GS} - V_{TH})^2 \tag{1}$$

onde W é a largura do transistor,  $\mu_0$  é a mobilidade dos elétrons para os transistores NMOS (mobilidade das lagunas nos transistores PMOS),  $C_{ox}$  é uma constante que representa a capacitância por unidade de área da tecnologia associada à porta e é igual a  $C_{ox} = \frac{k_{ox}\varepsilon_0}{t_{ox}}$ ,  $k_{ox}$  é a constante dielétrica do óxido de silício (aproximadamente 3,9),  $\varepsilon_0$  é a permeabilidade no vácuo (8.85x10<sup>-12</sup> F/m) e  $t_{ox}$  representa a espessura do óxido de silício.

O transistor da tecnologia utilizada neste trabalho tem uma espessura de óxido de silício de 7,57 nm (75,7  $\check{A}$ ) e, portanto, o  $C_{ox}$  é aproximadamente 4,56 fF/ $\mu$ m<sup>2</sup>. Esse valor é usado nos cálculos.

Na Eq.1 o projetista tem controle das dimensões do dispositivo e da tensão  $V_{GS}$ . Assim se para uma relação W/L fixa se varia a tensão  $V_{GS}$  se obtém diferentes respostas de corrente do dreno, como mostrado na Figura 6. Essas curvas foram traçadas para um transistor da tecnologia CMOS  $0.35~\mu m$  (modelo MOS BSIM3v3) com dimensões  $35~\mu m$  e  $1~\mu m$  (W e L respectivamente) através do simulador elétrico ELDO.

É interessante observar na Eq.1 que se os valores de W e L forem dobrados, a razão W/L permanecendo igual,  $I_D$  permanece inalterada, mas as capacitâncias, associadas ao tamanho do dispositivo (como se verá adiante), aumentam. Isto modifica o comportamento da resposta em frequência do transistor.

A tensão limiar ( $V_{TH}$ ),  $C_{ox}$  e a mobilidade ( $\mu_0$ ) são parâmetros que dependem da tecnologia e, como consequência, o projetista não tem controle sobre eles.

Figura 6 -  $I_{DS}$  versus  $V_{DS}$  para diferentes valores de  $V_{GS}$

## 2.1.1. Efeito do corpo

Um fenômeno interessante ocorre quando a diferença de potencial fonte-substrato ( $V_{SB}$ ) passa a ser diferente de zero. Nesse caso a tensão de limiar ( $V_{TH}$ ) do dispositivo é aumentada à medida que a fonte se torna mais positiva em relação ao substrato, como se pode observar pela Eq.(2) (RAZAVI, 2010).

$$V_{TH} = V_{TH0} + \gamma (\sqrt{|2\Phi_F + V_{SB}|} - \sqrt{|2\Phi_F|})$$

(2)

onde  $V_{TH0}$  é a tensão de limiar quando  $V_{SB}=0$ ,  $\gamma$  é o coeficiente de efeito de corpo e  $\Phi_F$  é o chamado potencial de junção.  $\gamma$  e  $\Phi_F$  são parâmetros que dependem da tecnologia e, portanto, estão fora do controle do projetista.

## 2.1.2. Modulação de comprimento de canal

A medida que  $V_{DS}$  aumenta, quando o transistor está em saturação, aumenta a corrente de dreno, pois o comprimento de canal ( $L_{eff}$ ) diminui ( $I_D \alpha I/L_{eff}$ ). Esta variação do comprimento de canal é chamada de modulação de comprimento de canal e para modelar este efeito é inserido na Eq.1 um fator de correção, assim a nova equação é:

$$I_D = \frac{1}{2} \mu_0 C_{ox} \frac{W}{L} (V_{GS} - V_{TH})^2 (1 + \lambda V_{DS})$$

(3)

onde  $\lambda$  é o coeficiente de modulação de comprimento de canal.

A modulação de comprimento de canal está sob controle do projetista porque  $\lambda$  é inversamente proporcional a L (ALLEN e HOLBERG, 2002). Uma expressão para  $\lambda$  é (JOHNS e MARTIN, 1996):

$$\lambda = \frac{k_{ds}}{2L\sqrt{V_{DS} + (-V_{eff}) + \Phi_F}} \tag{4}$$

onde  $V_{eff} = V_{GS} - V_{TH}$ ,  $k_{ds} = \sqrt{\frac{2k_{si}\mathcal{E}_0}{qN_A}}$ ,  $k_{si}$  é a constante dielétrica do silício (igual a 11,8), q é a carga do elétron (1,602x10<sup>-19</sup> C) e  $N_A$  é a concentração da dopagem no substrato.

Na Figura 7 é ilustrada a modulação do comprimento de canal para um transistor na tecnologia CMOS  $0.35~\mu m$ , polarizado com  $0.9~\rm V$  de tensão  $V_{GS}$  e  $0~\rm V < V_{DS} < 1.8~\rm V$ . O comprimento do dispositivo foi alterado de  $0.35~\mu m$  até  $0.7~\mu m$  e  $W=35~\mu m$ . A figura 7 aponta que  $\lambda$  é inversamente proporcional a L, como já dito.

Figura 7 - Modulação do Comprimento de Canal

#### 2.1.3. Transcondutância

A transcondutância é a relação entre a variação da corrente de dreno e a variação de tensão  $V_{GS}$  ou:

$$g_m = \frac{\partial I_D}{\partial V_{GS}}$$

Para a região de saturação, derivando a Eq.1 obtém se:

$$g_m = \mu_0 C_{ox} \frac{W}{L} (V_{GS} - V_{TH}) \tag{5}$$

A Eq.5 revela que  $g_m$  é linearmente proporcional a W/L para um valor fixo de  $(V_{GS}-V_{TH})$  e vice-versa, ou seja, é linearmente proporcional a  $(V_{GS}-V_{TH})$  para um valor fixo de W/L. Também pode ser expressado como uma função da corrente; da Eq.1 temos que se isolamos a diferença de tensões obtemos:

$$V_{GS} - V_{TH} = \sqrt{\frac{2I_D}{\mu_0 C_{ox} \frac{W}{L}}}$$

(6)

Agora, substituindo Eq.6 na Eq.5 e agrupando obtemos:

$$g_m = \sqrt{2\mu_0 C_{ox} \frac{w}{L} I_D} \tag{7}$$

A Eq.7 revela que  $g_m$  é proporcional à  $\sqrt{\frac{w}{L}}$  para um valor fixo de  $I_D$ , e também  $g_m$  é proporcional  $\sqrt{I_D}$  para um valor fixo de W/L. Caso dividimos a Eq.5 pela Eq.1 e reagrupemos novamente temos:

$$\frac{g_m}{I_D} = \frac{\mu_0 C_{ox} \frac{W}{L} (V_{GS} - V_{TH})}{\frac{1}{2} \mu_0 C_{ox} \frac{W}{L} (V_{GS} - V_{TH})^2}$$

$$g_m = \frac{2I_D}{V_{GS} - V_{TH}} \tag{8}$$

Neste caso  $g_m$  é linearmente proporcional a  $I_D$ , quando  $(V_{GS} - V_{TH})$  é fixo, também se pode observar que para um dado  $I_D$ ,  $g_m$  é inversamente proporcional a  $(V_{GS} - V_{TH})$ .

## 2.1.4. Capacitâncias intrínsecas

Nos circuitos de RF é importante considerar as capacitâncias intrínsecas do transistor MOS porque elas têm direta participação no comportamento da resposta em frequência do circuito. Na Figura 8 são ilustradas as capacitâncias (LAKER e SANSEN, 1994) (JOHNS e MARTIN, 1996) e na Tabela 3 se apresenta a descrição delas.

Figura 8 - Capacitâncias intrínsecas de um transistor NMOS

Tabela 3 - Capacitâncias Intrínsecas do transistor MOS

| Capacitância  | Descrição                                                                               |

|---------------|-----------------------------------------------------------------------------------------|

| $C_1$         | Capacitância entre a porta e o canal, $C_1 = WLC_{ox}$                                  |

| $C_2$         | Capacitância entre o canal e o substrato, $C_2 = WL\sqrt{q\varepsilon_{si}N_A/4\Phi_F}$ |

| $C_3$ e $C_4$ | Capacitância devida à área de sobreposição entre a porta sobre a fonte ou dreno         |

| $C_5$ e $C_6$ | Capacitância entre o dreno e fonte e o substrato                                        |

As capacitâncias  $C_3$  e  $C_4$  são chamadas na literatura de capacitâncias de *overlap* e para obter uma expressão delas se requer cálculos mais elaborados (RAZAVI, 2001). A capacitância  $C_5$  e  $C_6$  são geralmente compostas em duas componentes: uma capacitância de junção de área ( $C_j$ ) e outra capacitância de junção de perímetro ( $C_{jsw}$ ) (RAZAVI, 2001).

É de nosso interesse conhecer as equações das capacitâncias entre os terminais do dispositivo (Figura 9) na saturação. Equações aproximadas são apresentadas na Tabela 4. Nessa tabela  $C_{ov}$  é a capacitância de *overlap* por unidade de comprimento. Ela depende do quanto as difusões de dreno ou fonte avançaram para baixo da região de porta.

Figura 9 - Capacitâncias entre os terminais do NMOS

Tabela 4 - Capacitâncias dos terminais na saturação

| $C_{GS} = 2/3 \ WLC_{ox} + WC_{ov}$ |

|-------------------------------------|

| $C_{GD} = WC_{ov}$                  |

| $C_{GB} = Desprezada$               |

| $C_{SB} = C_5 + 2/3 C_2$            |

| $C_{DB} = C_6$                      |

# 2.1.5. Modelo de pequeno sinal

Caso as correntes e as tensões do transistor sejam perturbadas por pequenas variações, a representação do dispositivo pelo modelo de pequeno sinal é importante para que se possam realizar análises no circuito. Observemos que a relação não linear entre  $I_D$  e  $V_{DS}$  revela que o transistor não pode ser modelado por um simples resistor linear (RAZAVI, 2010). Novamente, para este trabalho, a região de operação de interesse é a região de saturação, assim o modelo de pequenos sinais estudado é dessa região. O modelo mais simples do transistor na região de saturação é uma fonte de corrente controlada por tensão como apresentado na Figura 10.

Figura 10 - Modelo de pequenos sinais simples

A figura revela que a corrente de dreno é controlada pela tensão de entrada assim  $I_D = g_m V_{GS}$ . A porta permanece aberta o que implica, neste modelo, uma corrente de entrada nula. Agregando um resistor, como mostrado na Figura 11, se representa a modulação de comprimento de canal, ou seja, a variação de  $I_D$  com respeito à  $V_{DS}$ .

Figura 11 - Modelo de pequenos sinais com resistor

onde  $r_o$  é a resistência de saída do transistor para análise de pequenos sinais. Essa resistência é definida como  $r_0 = \left(\frac{\partial I_D}{\partial V_{DS}}\right)^{-1}$  e usando a Eq.(2) (porque nela está presente o efeito de modulação de comprimento de canal) temos que:

$$r_0 = \frac{1}{\frac{1}{2}\mu_0 C_{ox} \frac{W}{I} (V_{GS} - V_{TH})^2 \lambda}$$

(9)

A literatura ilustra que  $r_0$  pode ser aproximado assim (LAKER e SANSEN, 1994):

$$r_0 \cong \frac{1}{\lambda I_D} \tag{10}$$

Um modelo um pouco mais complexo do modelo de pequenos sinais é ilustrado na Figura 12, onde se acrescentam as capacitâncias  $C_{GS}$  e  $C_{GD}$  que se formam entre a porta e as difusões de fonte e dreno, como já dito.

Figura 12 - Modelo pequenos sinais com capacitores

O modelo de pequenos sinais pode ser ainda mais complexo, que alias é utilizado por simuladores para obter resultados mais próximos dos resultados reais. Um modelo mais complexo teria, por exemplo, as capacitâncias  $C_{SB}$  e  $C_{DB}$ , teria outra fonte de corrente dependente controlada pela tensão  $V_{SB}$ , modelando o efeito de corpo. Na Figura 13 se ilustra um modelo mais detalhado do que aquele da Figura 12.

Figura 13 - Modelo de pequenos sinais Completo

Os resistores  $r_D$ ,  $r_S$  e  $r_B$  modelam os contatos ôhmicos dos terminais dreno, fonte e substrato respectivamente. O resistor  $r_G$ , modela além do contacto ôhmico da porta e também a resistência do material de porta. O substrato junto com as difusões de porta e dreno contribuem à formação das capacitâncias  $C_{SB}$  e  $C_{DB}$ .

Para as análises teóricas geralmente são utilizados os modelos das figuras Figura 11, em baixas frequências, e Figura 12, em altas frequências, pela simplicidade destes modelos. Neste caso os resultados obtidos servem como uma primeira aproximação do projeto, que, com ajuda de ferramentas de simulações, podem ser refinados posteriormente.

Por fim, é bom lembrar que os transistores em geral estão caracterizados pela frequência de ganho unitário (BEVILACQUA e NIKNEJAD, 2004) (TSIVIDIS, 2010) que indica para qual frequência o ganho de corrente, entre corrente de porta e corrente de dreno, é unitário. Esta frequência é aproximadamente dada por:

$$\omega_T \approx \frac{g_{m1}}{c_{GS1}} \tag{11}$$

# 2.2. Amplificadores de Baixo Ruído – LNA

Nesta seção são abordados brevemente os conceitos relacionados aos LNAs. O objetivo é apresentar uma discussão dos parâmetros de projeto e as topologias frequentemente usadas, com suas vantagens e desvantagens. Segue uma breve descrição de indutores passivos e indutores ativos e, após isso, se discute qual a topologia escolhida para realizar o projeto deste trabalho. Finalmente são ilustradas as dificuldades no projeto de LNAs e se fornece uma previa de uma possível solução, ou seja, de como contornar as dificuldades.

### 2.2.1. Parâmetros de projeto

Como já foi dito no projeto de amplificador de baixo ruído o problema é obter um bom compromisso entre os parâmetros de projeto. Em seguida serão definidos esses parâmetros.

#### 2.2.1.1. Fator de ruído/Figura de ruído

O fator de ruído é a medida da degradação na relação sinal ruído - SNR ( $Signal\ to\ Noise\ Ratio$ ) - que um bloco do circuito introduz (GONZALEZ, 1997). O SNR é definido como a relação entre a potência do sinal e a potência de ruído. Assim, um bloco tem na sua entrada uma relação sinal ruído  $SNR_{in}$  e na sua saída outra relação sinal ruído  $SNR_{out}$ , define-se fator de ruído F como:

$$F = \frac{SNR_{in}}{SNR_{out}} \tag{12}$$

O ideal seria que o  $SNR_{in}$  fosse igual ao  $SNR_{out}$ , mas na realidade circuitos com componentes ativos, e.g. transistores, sempre acrescentarão ruído.

A figura de ruído, *NF* (*Noise figure*), é a transformação à escala logarítmica do fator de ruído (Eq. 12), ou seja:

$$NF = 10\log_{10}(F) \tag{13}$$

Neste trabalho será empregado o conceito de figura de ruído, ou seja, os resultados das simulações elétricas para as medições de ruído são transformadas na escala logarítmica.

Antes de seguir com a descrição dos outros parâmetros será exposta uma definição de ruído e os tipos de ruído presentes nos dispositivos ativos e passivos de nosso interesse.

#### 2.2.1.2. Ruído

Na literatura pode-se observar que com frequência a figura de mérito no projeto de LNA é o ruído que ele introduz (ALLSTOT, LI e SHEKHAR, 2004). O ruído pode ser definido como qualquer sinal de interferência aleatória e que não tem relação com o sinal de interesse. Essas interferências em resistores e transistores MOS, na forma de correntes ou tensões, são de três tipos diferentes: ruído térmico, ruído *flicker* e ruído *shot* (GREGORIAN e TEMES, 1986). Este último não será considerado, pois não aparece nos dispositivos empregados aqui.

• Ruído térmico: É aquele gerado, como sinais aleatórios, devido ao movimento térmico aleatório dos portadores. Por ser um processo aleatório não é possível

identificar um valor específico de tensão (ou da corrente) em um instante particular, portanto é caracterizado com medidas estatísticas como o valor quadrático médio (LEE, 1998). Para um resistor o ruído térmico pode ser expresso em termos de tensão como:

$$\overline{v_n^2} = 4kTR\Delta f \tag{14}$$

onde  $\overline{v_n^2}$  é o valor quadrático médio da tensão de ruído, R o valor da resistência, k a constante de Boltzmann (1,38x10<sup>-23</sup>J/K), T a temperatura absoluta em Kelvins e  $\Delta f$  é a largura de banda do ruído. Em termos de corrente o ruído térmico no resistor é dado por:

$$\overline{i_{nT}^2} = 4kTG\Delta f \tag{15}$$

onde  $\overline{i_n^2}$  é o valor quadrático médio da corrente de ruído e G=1/R.

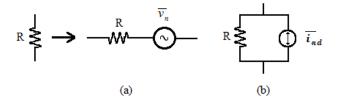

Para a análise de ruído, um resistor pode ser modelado com um resistor ideal mais uma fonte de ruído em tensão ou em corrente como mostra a Figura 14.

Figura 14 - Modelo do ruído térmico para um resistor: (a) tensão (b) corrente

Nos transistores MOS o ruído térmico também está presente. A corrente no dreno contribui com o chamado ruído da corrente de dreno. Considerações teóricas fornecem a seguinte expressão (LEE, 1998):

$$\overline{i_{nd}^2} = 4kTg_{d0}\gamma\Delta f$$

onde  $\overline{i_{nd}^2}$  é o valor quadrático médio da corrente de ruído,  $g_{d0}$  é a condutância quando  $V_{DS}=0$ ,  $\gamma$  é o coeficiente de ruído no dreno (tem um valor de um quando  $V_{DS}=0$  e decresce até 2/3 na saturação). Observe que em baixas frequências é possível desprezar esse ruído, mas em altas frequências ele se torna considerável.

Adicionalmente, a agitação térmica no canal gera o chamado ruído de porta. Este ruído também é desprezível em baixas frequências, mas não em altas frequências. Este tipo de ruído pode ser expresso como (VAN DER ZIEL, 1986):

$$\overline{i_{ng}^2} = 4kTg_g\delta\Delta f \tag{16}$$

onde  $\delta$  é o coeficiente de ruído da porta,  $g_g$  é a condutância formada entre porta e fonte e se expressa como:

$$g_g = \frac{\omega^2 C_{GS}^2}{5g_{d0}} \tag{17}$$

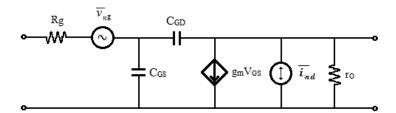

Na Figura 15 é ilustrado o modelo do transistor MOS com fontes de ruído para uso em análises de ruído.

Figura 15 - Modelo de ruído do transistor MOS

• Ruído Flicker: também é conhecido como ruído 1/f devido ao fato de que sua densidade espectral de potência é inversamente proporcional á frequência. Este ruído tem sido estudado fortemente, porém não é claro qual o origem dele (LEE, 1998). Nenhum mecanismo universal foi provado como causa do ruído flicker (GREGORIAN e TEMES, 1986). Uma das teorias atribui a origem às flutuações aleatórias do número de portadores no canal do transistor (TSIVIDIS, 2010). Apesar de não ser conhecida a sua origem, é possível modela-lo como uma fonte de tensão em série com a porta com tensão quadrática média representada por (RAZAVI, 2001):

$$\overline{v_n^2} = \frac{K}{fWLC_{ox}} \tag{18}$$

onde  $\overline{v_n^2}$  é a tensão quadrática média do ruído *flicker*, K é uma constante que depende da temperatura e dos processos de fabricação (um valor típico é  $3x10^{-24}~V^2F$ ), e f é a frequência onde o ruído é avaliado.

Como o ruído *flicker* é inversamente proporcional à frequência, ele tem um valor elevado apenas em frequências baixas.

#### 2.2.1.3. Ganho

Inicialmente vamos diferenciar ganho de tensão de ganho de potência ( $S_{21}$ ). Em amplificadores de baixo ruído o ganho de tensão é utilizado quando na saída do LNA a carga é capacitiva, onde não é preciso realizar casamento da impedância de saída. Por outro lado quando na saída do LNA a carga é resistiva é necessário realizar casamento da impedância de saída e, nesse caso, o ganho de potência é mais interessante de ser aplicado (GOLIO, 2008). Neste segundo caso, quando o casamento é perfeito ou quase perfeito o ganho de potência coincide com o ganho de tensão.

O ganho é definido como a razão entre a amplitude do sinal da saída pela amplitude do sinal da entrada. Portanto o ganho de tensão  $(A_v)$  é:

$$A_{v} = \frac{v_o}{v_i} \tag{19}$$

Observe que o ganho é uma medida sem dimensão, porém se torna em decibéis (dB) quando a Eq.19 é expressa na escala logarítmica, assim:

$$A_{v_{dR}} = 20\log\left(|A_v|\right) \tag{20}$$

Para o ganho de potência é conveniente primeiro escrever a definição de potência:

$$P = VI = \frac{V^2}{R}$$

Agora e pela definição de ganho temos que o ganho de potência  $(A_p)$  é:

$$A_p = \frac{P_o}{P_i}$$

onde  $P_o$  e  $P_i$  correspondem às potência fornecida à saída e a potência recebida na entrada do amplificador respectivamente. Pela definição de ganho temos que o ganho de potência é:

$$A_p = \frac{V_o^2 / R_o}{V_i^2 / R_i}$$

$$A_p = \frac{V_o^2 R_i}{V_i^2 R_o} \tag{21}$$

Da Eq.21 temos que quando as resistências da entrada  $(R_i)$  e da saída  $(R_o)$  são iguais o ganho de potência é igual ao quadrado do ganho de tensão:

$$A_{\mathcal{V}} = A_{\mathcal{V}}^2 \tag{22}$$

Transformando em decibéis a Eq.22 temos:

$$A_{p_{dB}} = 10\log\left(A_{v}^{2}\right)$$

$$A_{p_{dB}} = 20\log\left(A_v\right)$$

ou seja:

$$A_{p_{dB}} = A_{v_{dB}}$$

É por isso que quando as impedâncias de entrada e da saída são iguais o ganho de tensão coincide com o ganho de potência.

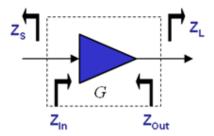

#### 2.2.1.4. Coeficiente de reflexão

LNAs são projetados normalmente para ter uma impedância de entrada de  $50\,\Omega$  de forma a casar com a impedância de saída da antena, tipicamente de  $50\,\Omega$  (LEE, 1998). Por essa razão é preciso projetar uma rede que faça o casamento da impedância de entrada do LNA com a impedância da antena. Para algumas arquiteturas a impedância de saída do LNA também deve ser de  $50\,\Omega$ .

O coeficiente de reflexão é utilizado para determinar o grau de casamento de impedâncias. É definido como a razão entre o sinal refletido e o sinal incidente e pode se escrever assim (GONZALEZ, 1997):

$$\Gamma = \frac{v^-}{v^+}$$

Na entrada de um LNA o coeficiente pode ser expresso, em termos das impedâncias associadas, por:

$$\Gamma_{in} = \frac{Z_s - Z_{in}}{Z_s + Z_{in}} \tag{23}$$

onde  $Z_{in}$  é a impedância de entrada do amplificador e  $Z_s$  é a impedância da fonte de sinal (antena). Na Figura 16 se apresentam as impedâncias ditas acima e associadas ao LNA.

Figura 16 - Impedâncias do LNA

Da Eq.23 se pode observar que quando se têm valores próximos de impedâncias  $Z_s$  e  $Z_{in}$ , o coeficiente de reflexão é baixo (o ideal é  $\Gamma$ =0). De forma similar se calcula o coeficiente de reflexão na saída do amplificador, dado por:

$$\Gamma_{out} = \frac{Z_L - Z_{out}}{Z_L + Z_{out}} \tag{24}$$

onde  $Z_L$  é a impedância da carga, que no caso da figura 2 é a impedância de entrada do circuito demodulador, e  $Z_{out}$  é a impedância de saída do amplificador.

#### 2.2.1.5. Linearidade

Um LNA deve fazer mais que amplificar sem acrescentar ruído. Ele deve manter um comportamento linear tanto na presença de sinais fracos como de sinais fortes (LEE, 1998). Um LNA de ganho de tensão  $A_{\nu}$  tem um comportamento linear quando para um sinal de entrada com tensão  $v_i$  o sinal de saída  $v_0$  é igual a  $A_{\nu}*v_i$ , qualquer que seja a amplitude de  $v_i$ . Claro que isso não ocorre para amplificadores reais.

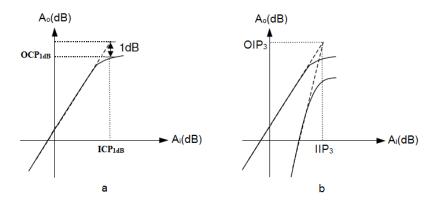

As medidas de linearidade mais utilizadas são o ponto de compressão de 1 dB (compression point 1dB - CP 1dB) e o ponto de interseção de terceira ordem (IP3) (Figura

17). O ponto de compressão de 1 dB referido na entrada,  $ICP_{1dB}$  ( $OCP_{1dB}$  quando referido na saída), é definido como a amplitude do sinal de entrada que faz com que o ganho tenha uma queda de 1 dB (TREVISAN, 2008) (Figura 17(a)). Com o ponto de compressão de 1 dB se calcula a faixa dinâmica (FD) do circuito. A FD é a diferença entre o a máxima amplitude do sinal de entrada ( $ICP_{1dB}$ ) e a mínima amplitude do sinal de entrada que pode ser detectada.

Figura 17 - Amplitude de saída, Ao, versus amplitude de entrada, Ai; a. ponto de compressão de 1dB; b. ponto de interseção de 3a ordem

O ponto *IP3* (Figura 17(b)) é um parâmetro para medir a influência das componentes de intermodulação de terceira ordem. Essas componentes de terceira ordem, geradas por tons com frequências próximas, podem alterar o sinal original. O *IIP3* (*IP3* referido a entrada) é a amplitude do sinal na entrada  $v_i = A[cos(\omega_1 t) + cos(\omega_2 t)]$ , onde  $\omega_1 \approx \omega_2$ , para o qual os sinais de saída na frequência  $\omega_1$  ou  $\omega_2$  e as componentes de intermodulação de terceira ordem, nas frequências  $(2\omega_1 - \omega_2)$  ou  $(2\omega_2 - \omega_1)$  tem amplitudes iguais. Caso aproximemos o comportamento do ganho do LNA por (CAMPOS RIBEIRO, 2004):

$$v_0 = a_0 + a_1 v_i + a_2 v_i^2 + a_3 v_i^3 + \dots$$

onde  $v_o$  é o sinal de saída e  $a_0$ ,  $a_1$ , ... são constantes, pode-se mostrar que (RAZAVI, 1998):

$$IIP_3 = \sqrt{\frac{4|a_1|}{3|a_3|}} \tag{25}$$

Os parâmetros  $CP_{IdB}$  e  $IP_3$  podem ser referenciados à entrada, como descrito acima, ou na saída como mostrado na Figura 17.

Pode-se mostrar que os parâmetros  $ICP_{1dB}$  e  $IIP_3$  estão relacionados por (RAZAVI, 1998):

$$20\log(\frac{IIP_3}{ICP_{1dB}}) \approx 9,6dB$$

#### 2.2.1.6. Fator de Estabilidade

Um LNA projetado pode oscilar inesperadamente em baixas ou em altas frequências para alguma combinação de impedâncias de fonte e carga. Para determinar a estabilidade do amplificador é preciso medir os seus parâmetros  $S(S_{11}, S_{12}, S_{21}, S_{22}, scattering parameters)$ . O parâmetro  $S_{21}$  é chamado na literatura de ganho direto (HALIM, AZIZ, *et al.*, 2008) (SHAEFFER e LEE, 1997) (DEBONO, MALOBERTI e MICALLEF, 2001). Outros autores, por exemplo (BEVILACQUA e NIKNEJAD, 2004) (HUANG, HUANG, *et al.*, 2008), chamam o parâmetro  $S_{21}$  de ganho de potência e geralmente aqueles utilizam essa nomenclatura quando a saída do amplificado está casada com a entrada do seguinte estágio. O parâmetro  $S_{12}$ , por sua vez, é o coeficiente de ganho inverso. Em amplificadores de baixo ruído este parâmetro mede o grau de isolamento entre a saída e a entrada.

O coeficiente de estabilidade pode ser calculado através da seguinte expressão (GONZALEZ, 1997) (POZAR, 2005):

$$K = \frac{1+|\Delta|^2 - |S_{11}|^2 - |S_{22}|^2}{2|S_{12}S_{21}|}$$

(26)

onde  $\Delta = S_{11}S_{22} - S_{12}S_{21}$ .

Se os coeficientes K e  $\Delta$  obedecerem as relações K>1 e  $|\Delta|<1$ , o LNA é incondicionalmente estável para qualquer combinação de impedâncias de fonte e carga. Da Eq.26 observa-se que a estabilidade melhora se o parâmetro  $S_{12}$  diminui, ou seja, são desejáveis valores baixos para o coeficiente de ganho inverso.

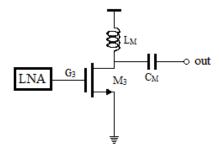

### 2.2.2. Arquiteturas de LNAs

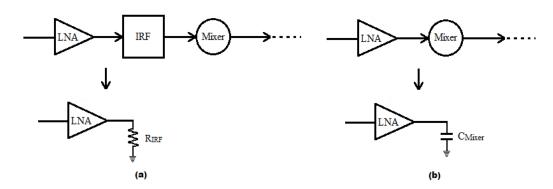

Como já dito o LNA é primeiro circuito do bloco receptor quando não é precedido de um filtro. O circuito subseguinte ao LNA pode ser outro filtro (IRF *Image Reject Filter*) ou o mixer como ilustra a Figura 18. É necessário que o projetista conheça o tipo de circuito subseguinte ao LNA para assim realizar os cálculos e simulações. Ele deve considerar uma carga resistiva quando um filtro segue ao LNA, ou considerar uma carga capacitiva quando é um mixer o estágio seguinte. Na literatura estas possibilidades são nomeadas de arquiteturas heteródine (heterodyne) (Figura 18(a)) e arquiteturas homódine (homodyne) (Figura 18(b)) (RAZAVI, 1998).

Figura 18 - Arquiteturas (a) Heteródine (carga resistiva) (b) Homódine (carga capacitiva)

O receptor homódine converte o sinal que chega à antena para a frequência de interesse diretamente, sem passar por filtros de frequências intermediárias. Por outro lado, o receptor heteródine converte o sinal que chega à antena a frequências de interesse através de um ou mais estágios de filtros de frequências intermediárias. Esse filtro ou filtros a mais, no receptor heteródine, ocasionam um maior consumo de potência que em receptores homódine. Outra desvantagem do receptor heteródine é a necessidade de um alto fator de qualidade (Q) para esses filtros, o que os faz difíceis de serem integrados junto ao circuito. Em compensação, o receptor heteródine tem maior largura de faixa de frequência e boa seletividade de canal de rádio. O receptor homódine possui baixo consumo de potência e maior possibilidade de integração, reduzindo o tamanho do receptor, devido a que não necessita de filtros de frequências intermediárias. Por outro lado, a conversão direta ocasiona o surgimento de alguns problemas que não existem nos receptores heteródine, por exemplo, o *offsets* de DC, distorção de ordem par, ruído *flicker*, etc. (RAZAVI, 1998).

Em geral um LNA consiste de três estágios: a rede de casamento da entrada (*Input Matching Network*), o amplificador propriamente dito e a rede de casamento da saída (*Output Matching Network*) (HALIM, AZIZ, *et al.*, 2008). Para projetar o estágio amplificador

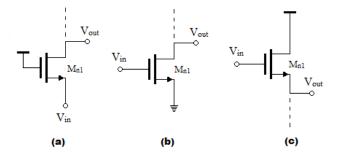

propriamente dito se utilizam duas configurações ou alguma combinação delas: Porta Comum e Fonte Comum. Há outra configuração, Dreno comum, geralmente usada com intuito de fornecer o casamento da impedância da saída ou como estágio de saída para medições. Estas configurações podem ser usadas na forma de terminação simples ou na forma diferencial, segundo as exigências de projeto (VAROTTO, 2004).

Cada uma delas apresenta vantagens e desvantagens nos parâmetros de projeto, ou seja, melhores ou piores desempenhos nos parâmetros podem ser obtidos de acordo com a escolha da arquitetura. Em seguida se dá uma breve descrição de cada arquitetura (RAZAVI, 2010).

- Porta Comum (PC): Na topologia porta comum mostrada na Figura 19(a), o sinal de entrada é aplicado à fonte e a saída colhida no dreno do transistor. Esta topologia fornece ganho de tensão moderado, baixa impedância de entrada e moderada impedância de saída;

- Fonte Comum (FC): Na topologia fonte comum ilustrada na Figura 19b, o sinal de entrada é aplicado à porta e a saída colhida no dreno. Provê ganho de tensão moderado, alta impedância de entrada e moderada impedância de saída;

- Dreno comum (DC): Nesta topologia, também chamada Seguidor de Fonte, o sinal de entrada é aplicado na porta do transistor e a saída colhida na fonte como se pode observar na Figura 19c. O seguidor de Fonte provê ganho de tensão menor que a unidade, alta impedância de entrada e baixa impedância de saída.

Para que o LNA atinja suas especificações se utilizam duas das configurações acima, a PC ou a FC, normalmente sós, mas podem também vir combinadas. A configuração Seguidor de Fonte geralmente é usada com intuito de fornecer o casamento da impedância da saída.

Figura 19 - Topologias: (a) Porta Comum (PC), (b) Fonte Comum (FC), (c) Dreno comum (DC).

As arquiteturas mais utilizadas no projeto de amplificador de baixo ruído são aquelas com degeneração na fonte, onde um resistor ou indutor é ligado em serie à fonte, servindo para melhorar a linearidade, aumentar a impedância da saída (RAZAVI, 2010) e casar a impedância de entrada. Assim por exemplo temos:

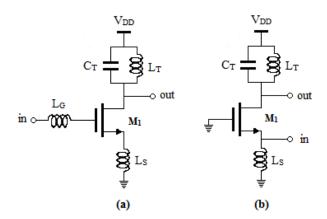

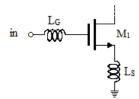

- Configuração FC com degeneração indutiva (DI) na fonte: Nesta configuração, desenhada na Figura 20(a), se utiliza um amplificador FC. Os indutores aplicados na fonte e na porta servem para cancelar a capacitância de entrada e ajustar a impedância. Comparada com a seguinte configuração, esta apresenta maior dificuldade para fazer o casamento da impedância de entrada, mas em compensação apresenta uma melhor figura de ruído.

- Configuração PC com degeneração indutiva (DI) na fonte: Nesta configuração, ilustrada na Figura 20(b), se utiliza um amplificador PC. O indutor aplicado na fonte serve para cancelar a capacitância de entrada a fim de obter uma impedância resistiva. O principal problema com esta configuração PC é a mínima figura de ruído (NF), tipicamente maior que 3,0 dB, mas ela oferece, como compensação, uma maior facilidade para a realização do casamento da impedância de entrada (KAUKOVUORI, KALTIOKALLIO e RYYNÄNEN, 2007).

Figura 20 - (a) Configuração FC com DI, (b) PC com DI

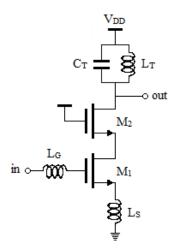

• FC Cascode com degeneração indutiva na fonte (FCCDI) (Figura 21): Esta arquitetura utiliza um amplificador fonte comum com transistor cascode em série. A configuração em cascode com degeneração indutiva na fonte se caracteriza por

garantir que o amplificador apresente ganho consideravelmente alto. O transistor  $M_2$  é utilizado como *cascode* ainda para melhorar o isolamento entre entrada e saída, ou seja, isola a entrada das variações de tensões da saída (BEVILACQUA e NIKNEJAD, 2004) (SHAEFFER e LEE, 1997). Com isto se garante também maior estabilidade no amplificador.

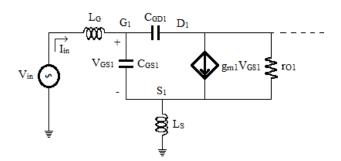

Figura 21 - Configuração Fonte Comum Cascode com degeneração indutiva (FCCDI)

As indutâncias  $L_G$  e  $L_S$  são utilizadas para fazer o casamento da impedância da entrada.

Nas três arquiteturas a capacitância  $C_T$  e indutância  $L_T$  servem para sintonizar o estágio na frequência de operação e dar ganho.

Observemos que a degeneração indutiva na fonte é o método mais usado em amplificadores CMOS de RF porque oferece a possibilidade de alcançar o melhor desempenho de ruído.

Com auxílio da Tabela 5 vemos de forma resumida as características (vantagens e desvantagens) das configurações para LNA com degeneração indutiva.

Tabela 5 - Resumo das configurações com DI

| Configuração                                   | Vantagens                                                                                                             | Desvantagens                           |  |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|

| PC com Degeneração<br>Indutiva<br>(PCDI)       | Simples casamento da impedância de entrada                                                                            | Figura de ruído elevada                |  |

| FC com Degeneração<br>Indutiva<br>(FCDI)       | bom ganho e<br>boa figura de ruído                                                                                    | Casamento da impedância<br>da entrada. |  |

| FC Cascode com degeneração<br>Indutiva (FCCDI) | Maior ganho, melhor<br>isolamento da entrada à saída,<br>portanto maior estabilidade, e<br>aceitável figura de ruído. | Casamento da impedância<br>da entrada. |  |

Na Tabela 5 pode-se observar que a configuração FCCDI oferece além do melhor ganho o melhor isolamento, o que garante valores baixos para o coeficiente de ganho inverso e um melhor comportamento no quesito da estabilidade como será visto mais na frente, porém degrada a figura de ruído por causa do transistor cascode.

É pelas características ditas da configuração FCCDI (Figura 21) que neste trabalho se fez a escolha por ela para realizar os projetos.

Observe que no circuito de LNA, Figura 21, indutores são aplicados tanto na rede de entrada como no amplificador propriamente dito. Por isto segue uma resenha deste dispositivo.

#### 2.2.3. Indutores

A função dos indutores nos LNAs é cancelar capacitâncias, sintonizar o LNA para certa frequência de operação, além de servir de carga para dar ganho. Esses indutores podem ser fabricados no mesmo substrato junto com todos dispositivos do LNA. Quando fabricados em espiral com as camadas de metal disponíveis, são chamados de indutores passivos; quando o equivalente comportamento indutivo é obtido através de transistores, são chamados de indutores ativos.

#### 2.2.3.1. Indutores Passivos

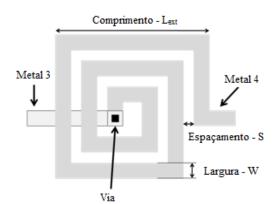

Na Figura 22 (REBELLO GUERREIRO, 2011) é ilustrado um indutor passivo, construído com a camada de metal quatro com a saída feita em metal três. Também são indicadas as dimensões relevantes para sua construção.

Figura 22 - Indutor passivo: parâmetros de construção

Os indutores passivos se caracterizam geralmente por ter baixo fator de qualidade e ocupar grande espaço na pastilha de silício. Em compensação consomem relativa baixa potência e introduzem pouco ruído ao circuito. O projetista precisa, na hora de projetar um circuito que utiliza indutores, calcular o valor da indutância e ter um modelo para fazer as análises elétricas. O valor da indutância, para um indutor em espiral, pode ser calculado aproximadamente pela seguinte relação empírica com menos de 10% de erro (RAZAVI, 2010):

$$L \approx 1.3e^{-7} \frac{A_m^{\frac{5}{3}}}{A_{tot}^{\frac{1}{6}}(W+s)^{0.25}}$$

(27)

onde  $A_m$  é a área de metal (a região cinza na Figura 23),  $A_{tot}$  é a área total ( $\approx (L_{ext})^2$ ), W e S são a largura e o espaçamento como mostrado na Figura 23.

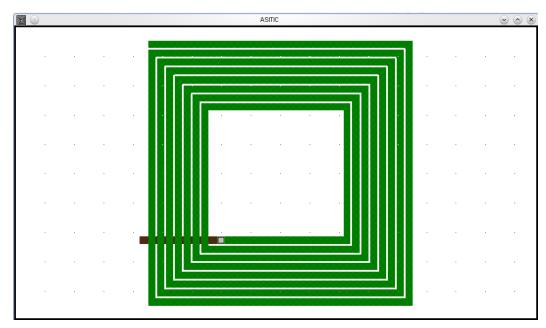

Além do valor da indutância é preciso modelar em altas frequências efeitos importantes dos indutores passivos, por exemplo, as capacitâncias parasitas, efeitos de correntes eddy, efeito pelicular e perdas por acoplamento eletromagnético. Para modelar os indutores passivos neste trabalho utilizou-se a ferramenta ASITIC (*Analysis and Simulation of Inductors and*

*Transformers in Integrated Circuits*) (ASITIC) (NIKNEJAD, 2002). Essa ferramenta ajuda no projeto de indutores além de capacitores e transformadores.

Para o funcionamento da ferramenta ASITIC é necessário fornecer a geometria do indutor (quadrado, circular, hexagonal), dimensões (comprimento externo  $L_{ext}$ , largura da trilha W, e espaçamento entre trilhas S e número de voltas n como mostrado na Figura 22) e o arquivo com a descrição da tecnologia (resistividades e espessuras das camadas de substrato e metais, constantes dielétricas e espessuras das camadas de isolante). O arquivo da tecnologia utilizado neste trabalho é apresentado no anexo B.

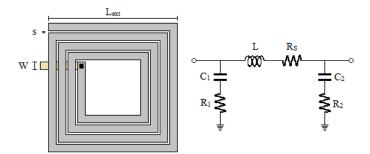

Na Figura 23 é apresentado um indutor passivo com o modelo PI equivalente e na Tabela 6 estão contidas as descrições dos componentes do modelo.

Figura 23 - Parâmetros do indutor e seu modelo PI

Tabela 6 - Descrição dos componentes do modelo PI

| Componente                      | Descrição                                  |

|---------------------------------|--------------------------------------------|

| L                               | Corresponde ao valor da indutância         |

| $R_{\rm s}$                     | Resistência série dos segmentos            |

| C <sub>1</sub> e C <sub>2</sub> | Capacitância entre o indutor e o substrato |

| R <sub>1</sub> e R <sub>2</sub> | Resistência do substrato                   |

Um exemplo de indutor gerado com a ferramenta é apresentado na Figura 24, na Tabela 7 estão contidos os valores das dimensões e na Tabela 8 estão os valores fornecidos pela ferramenta ASITIC para os componentes elétricos do modelo PI (para uma frequência de operação de 1,8 GHz).

Figura 24 - Modelo de indutor passivo gerado com ASITIC

Tabela 7 - Dimensões do indutor da Figura 24

| Dimensão              | Valor |  |  |

|-----------------------|-------|--|--|

| L <sub>ext</sub> [µm] | 180   |  |  |

| W [µm]                | 5     |  |  |

| s [µm]                | 1     |  |  |

| n [voltas]            | 7,75  |  |  |

Tabela 8 - Valores obtidos com ASITIC

| Componente                                   | Valor       |

|----------------------------------------------|-------------|

| L [nH]                                       | 12,4        |

| $\mathbf{R}_{\mathrm{s}}\left[\Omega\right]$ | 32,5        |

| C <sub>1</sub> e C <sub>2</sub> [fF]         | 65,7 e 62,4 |

| $R_1 e R_2 [K\Omega]$                        | 1,39 e 1,69 |

O valor da indutância obtido segundo a Eq.27 foi de 16,1 nH. Observe que o erro entre o valor teórico e o valor prático é de 23%, maior ao 10% dito na literatura. Essa diferença pode ser causada porque a Eq.27 só considera as dimensões e não propriedades físicas da tecnologia de construção. Com tudo como uma primeira aproximação pode ser aceita.

### 2.2.3.2. Indutores ativos

As dimensões físicas dos circuitos integrados para aplicações móveis são sempre uma preocupação. Duas desvantagens dos indutores passivos são suas dimensões, grandes mesmo para pequenas indutâncias, e o baixo fator de qualidade (PASCHT, FISCHER e BERROTH, 2001) (YANG, LEE, *et al.*, 2007). Uma alternativa para contornar estas desvantagens é o uso de indutores ativos. Um indutor ativo (IA) é um circuito construído com transistores (por isto é chamado de ativo) que apresenta um comportamento indutivo numa faixa específica de frequências. Ele requer transistores e capacitores para emular o comportamento indutivo e seu projeto está baseado no bloco *gyrator* (PASCHT, FISCHER e BERROTH, 2001).

Os indutores ativos, comparados com os passivos, apresentam algumas desvantagens como introdução de maior ruído, maior consumo de potência, faixa dinâmica limitada (comportamento não linear) e menor estabilidade (YUAN, 2008). Em compensação (em comparação com indutores passivos) utilizar indutores ativos, no projeto de circuitos de RF fornece:

- Menor área utilizada na pastilha;

- Maior indutância e fator de qualidade Q;

- O ajuste da indutância e do fator de qualidade Q;

- O ajuste da frequência de ressonância.

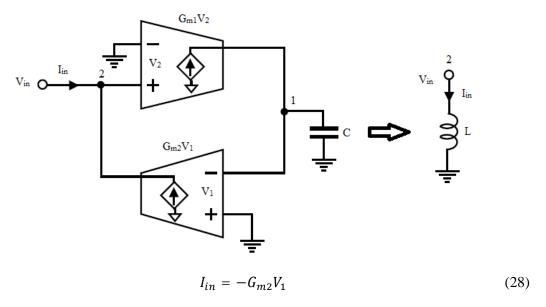

Como já dito, um indutor ativo baseia sua operação no bloco *gyrator*. Este é formado pela conexão de transcondutores (dispositivo conversor de tensão a corrente). Quando uma porta do *gyrator* é conectada a um capacitor, observar a Figura 25, o circuito é chamado *gyrator*-C (YUAN, 2008). Para um *gyrator* ideal, as impedâncias de entrada e saída dos transcondutores são de valor infinito e os valores das transcondutâncias dos transcondutores são constantes (YUAN, 2008). Assim da Figura 25 podem-se obter as seguintes expressões:

Figura 25 - Indutor Ativo e sua Indutância equivalente

onde  $G_{m2}$  é a transcondutância do *gyrator* 2 (localizado na parte inferior) e  $V_1$  é a tensão no nó um. Assim, temos que tensão no nó 1 é:

$$V_1 = -\frac{G_{m1}V_2}{sC} {29}$$

onde  $Gm_1$  é a transcondutância do *gyrator 1*. Observe que a tensão no nó 2,  $V_2$ , é igual à tensão de entrada,  $V_{in}$ , assim e substituindo a Eq.29 na Eq.28 obtemos:

$$I_{in} = \frac{G_{m1}G_{m2}V_{in}}{sC}$$

$$Y = \frac{I_{in}}{V_{in}} = \frac{G_{m1}G_{m2}}{sC}$$

(30)

A Eq.30 corresponde à admitância do IA, portanto a impedância é:

$$Z = \frac{V_2}{I_{in}} = S \frac{C}{G_{m1}G_{m2}} \tag{31}$$

Da Eq.31 pode-se observar que o *gyrator-C* se comporta como um indutor (*sL*) com valor de indutância igual a:

$$L = \frac{C}{G_{m1}G_{m2}}$$

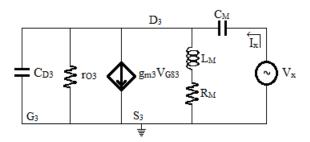

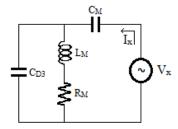

Um indutor ativo precisa, para ser implementado, de uma transcondutância positiva e outra negativa para que possa apresentar o atraso de fase necessário para emular a impedância indutiva. Estas transcondutâncias podem ser fornecidas pelas mesmas configurações apresentadas na Figura 19: a configuração fonte comum (FC) apresenta transcondutância